基于FPGA单精度浮点数算术运算系统的设计与仿真

2018-02-27谢四雄李克俭蔡启仲潘绍明

谢四雄 李克俭 蔡启仲 潘绍明

摘要

本文应用FPGA自主设计浮点数算术运算系统,根据单精度浮点数的特点,设计了其存储格式,采用模块化设计方式设计了浮点数算术运算系统的组成结构,该系统可以根据运算指令要求的精度、数据来源方式、操作数个数进行加、减、乘、除运算。设计的系统采用Altera公司的EP4CE115F23I7N芯片实现,该芯片的时钟频率为48MHz,设置运算系统运行频率为192MHz,并通过仿真测试可知,设计的浮点数算术运算系统满足各种运算要求,运算系统仅占用了FPGA芯片总逻辑单元的18%,片内存储器使用量占用了不到1%。

【关键词】FPGA 单精度浮点运算 模块化 系统

FPGA近年来在体系结构、技术水平和持续改进的设计方面进行了提高和完善,弥补了专用处理器灵活性不足之处,FPGA的容量、速度和资源已经有了更好的提高。在微处理器的指令系统中,浮点数加/减和乘/除法指令都是实现2个单精度浮点数的运算,浮点数算术运算系统的设计通常采用流水线和自顶向下方式,但对于所执行的浮点数算术运算指令需要应用上一条运算指令的运算结果作为操作数的指令,则浮点数算术运算的流水线操作失去作用,影响了浮点数算术运算指令执行的速度。本设计利用Verilog语言,采用基于FPGA自主设计的浮点数算术运算系统,进行浮点加减乘除运算验证和仿真,提高了运算的操作速度,具有较强的通用性和可操作性。

1 单精度浮点加减乘除运算

1.1 单精度浮点数表示

IEEE754标准中,一个规格化32位的浮点数表示为:

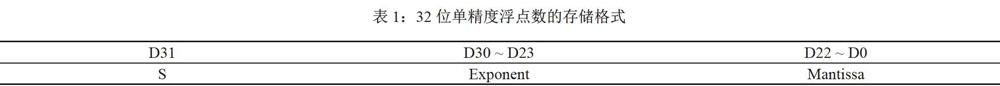

其中用1位表示数字的符号S,S为。表示正数,S为1表示负数。IEEE754标准中规定的规格化浮点数的阶码是用移码表示,用8位来表示阶码E,E是带有偏移量的阶码,偏移量是127,e是实际阶码,在计算实际阶码e时,对阶码E的计算采用源码的计算方式,32位浮点数的8位的阶码E的取值范围是0到255,用23位来表示尾数M,尾数用原码表示,其中尾数域值是1.M。单精度浮点数的存储格式如表1所示,因为规格化的浮点数的尾数域最左位总是1,故这一位不予存储,而认为隐藏在小数点的左边,使用的时候再恢复出来。

1.2 单精度浮点数加减运算方法

一般的规格化浮点数的加减运算步骤都要经过对阶,尾数加减,尾数规格化,舍入,判断溢出5个步骤。

对阶:根据两个数的正负号及操作指令来确定实际的运算是加还是减,如果是加法指令,当两个数的正负号相同时做加法运算,当两个数的正负号不同时做减法运算;如果是减法指令,当两个数的正负号相同时做减法运算,当两个数的正负号不同时做加法运算。同时,在计算两个数阶码的差值时,首先需要判断那个数的绝对值大,结果的符号和绝对值较大的浮点数的符号相同。最后根据前面计算出的阶码差值也就是右移的位数,把绝对值较小的尾数连同隐藏位一起右移。

尾数相减:对阶完成后,按照里面的操作,首先需要对两个数的绝对值进行计算。

尾数规格化:这步需要对结果规格化,使尾数格式为1.M的形式,找出高位第一个1,根据它所在的位置把尾数左移或右移后调整阶码,左移n位就从阶码中减n,右移n位就从阶码中加n。

舍入:IEEE754定义了就近舍入,向正无穷大舍入,向负无穷大舍入,向0舍入四种方式。

判断溢出:判断和或者差是否溢出,有溢出阶码就加1,没溢出就直接输出阶码。

1.3 单精度浮点数乘除运算方法

单精度浮点数乘法:首先是通过把两个数的符号进行异或运算来确定结果S的符号,其次是计算结果的阶码,然后是尾数相乘,最后是对尾数进行规格化处理。

单精度浮点数除法:首先也是通过把两个数的符号进行异或运算来确定结果S的符号,其次是计算结果的阶码,然后是尾数相除,最后是对尾数进行规格化处理。

2 单精度浮点数算术运算系统设计

2.1 单精度浮点数算术运算系统指令格式设计

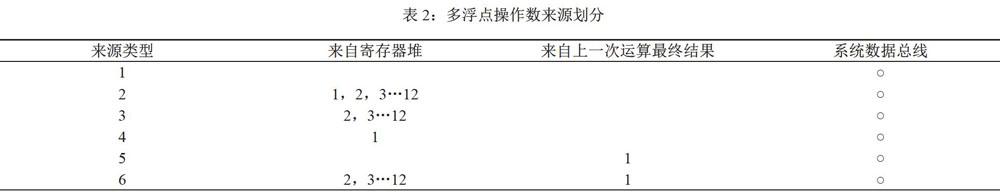

设计的单精度浮点写入操作数的方式是从系统数据总线上面写入算术运算系统,一条运算指令后面可以带上n个浮点操作数参与到运算过程,当满足操作数的数量大于等于两个的时候,算术运算系统就会根据指令的要求组织操作数运算,其中参与运算的浮点操作数来源有三种:系统数据总线、寄存器堆和算术运算系统内部的累加器,单精度多浮点操作数来源划分如表2所示,整个运算结束,算术运算系统会把运算结果放到系统数据总线上面,算術运算系统会通知总控制器读取结果。

其中1,2,3…12表示第n个操作数,o表示运算结果是写到系统数据总线。例如来源方式1:第1~12个操作数都来自系统数据总线。来源方式3:第1个操作数来自系统数据总线,第2~12个操作数由寄存器堆提供。制定的算术运算系统的指令格式包含了运算类型、参与运算的操作数个数、数据来源类型、精度方式和舍入模式信息,见表3。

在32位指令中:

D0:进行哪种精度的运算,。单精度运算。

D2~D1:舍入模式。最后的结果需要做哪种舍入方式的处理,数值为00的时候为向零舍入,01向最近的偶数舍入,10向正无穷舍入,11向负无穷舍入。

D5~D3:数据来源方式。对应表2的六种来源方式。001表示来源方式1,010表示来源方式2,011表示来源方式3,100表示来源方式4,101表示来源方式5,110表示来源方式6。

D31-D6:操作码与操作数的数量。其中D31~D10共22位信息,以两位表示一种运算符(00加,01减,10乘,11除)的话,一条运算指令最多可以执行11次运算。而对应的浮点运算操作数最多为12个,用4位D9~D6表示参与运算的操作数个数。

例如FPGA的控制模块发给算术运算系统一条指令32b000000000000000000_0

100_0011_101_01_0,其中DO为。(即单精度浮点操作数),D2~D1为01(即结果向最近的偶数舍入),D5~D3对应的是二进制数101换成十进制数即5,也就是表2中第5种数据来源方式。D9~D6对应的是0011即3,是3个操作数。这三个操作数中的第一操作数是来自于算术运算系统的累加器,第二和第三操作数是来自于系统数据总线。D13~D10对应0100即00代表加运算,01代表减运算,第1和2操作数先进行加运算然后和第3操作数进行减运算。

2.2 浮点数算术运算系统结构设计

浮点数算术运算系统的构建采用模块化设计,分为调配控制、数据分配、队列、累加器、浮点运算控制、浮点运算执行和结果标志寄存器七个模块。系统结构框图如图1所示。总控制器选中浮点数算术运算系统后,由调配控制模块对指令进行译码,组织系统数据总线或数据通道F_S_DB的多个浮点操作数,将其分配到累加器或队列模块,等待参与运算。同时,调配控制模块会向浮点数运算控制模块写一个命令,开始运算,并将寄放在队列和累加器的操作数写到浮点数运算模块参与运算。进入运算后,调配控制模块会不断查询运算的运行状态,运算结束,会把结果标志位放到结果标志寄存器里面,同时,使能累加器读取最后的运算结果。通知总控制器读取结果,并将结果写回系统数据总线。该运算系统接收到总控制器运算指令后,可以自主完成不同模式下的加、减、乘、除四种运算功能。

nQRY:读操作数请求,低有效;

wr_op:写运算结果请求,低有效;

F_S_DB:与算术运算系统之间的传输操作数和运算结果的通道;

n_ANS:发给算术运算系统的读操作数应答,低有效;

n_REPLY:写运算结果应答,低有效。

3 浮点数算术运算系统的运算过程

调配控制模块在对运算指令译码后,当运算的操作数、操作码和舍入模式信息都发送给运算控制模块后,开始控制运算执行模块进入单精度运算,浮点数算术运算系统运行的时钟频率为48MHz,系统运行的频率为192MHz,其中单精度的处理运算过程见图2所示。

(1)规格化预处理单元(加/减运算):操作数预处理,将两个32位的操作数opa,opb进行规格化处理,从单精度格式中恢复成浮点数源;价码对齐:价码向大对齐,取得价码差,然后执行对齐操作;尾数运算预处理:根据操作数的符号位,处理尾数;

(2)规格化预处理单元(乘/除运算):将两个32位的操作数opa,opb进行规格化处理,从单精度格式中恢复成浮点数源;尾数运算预处理:根据操作数的符号位,处理尾数;

(3)加减单元:尾数执行加减法运算;

(4)乘单元:符号位运算,符号位运算操作独立运行;阶码和尾数运算,阶码运算操作和尾数运算操作独立运行;

(5)除单元:符号位运算,阶码运算和尾数运算独立运行;

(6)规格化与舍入单元:结果预处理,规范化最后结果,取得运算结果的符号位,更新正值化运算结果;调整运算结果,并将最后结果以适合于浮点数源的格式输出;

(7)异常处理单元:输出和格式化,检测价码溢出,尾数零值等錯误,此外根据浮点运算控制模块的舍入模式执行舍入:当运算的结果出现非数等异常情况时,输出相应的标志位。

操作数预处理的目的就在于恢复隐藏在操作数中的符号位,其中加/减法与乘/除法在预处理单元的不同点在于:

(1)乘除运算没有阶码对齐这一步骤:

(2)乘除法不需要额外的空间来补偿尾数因位移而失去的部分:

(3)乘除法运算隐藏位的恢复取的是一位。所以要将这两部分分开操作。

4 仿真与验证

应用Altera公司的Quartus Ⅱ11.0软件作为可编程设计环境,对浮点数算术运算系统的内部结构进行程序编写、综合及仿真,调用ModelSim SE-64 10.0c仿真软件完成对运算系统内部数据变化及外部端口的输出状态的波形观测和验证,并在Cyclone ⅣEP4CE115F23I7N芯片上对综合仿真后的浮点数算术运算系统进行硬件测试。将调配控制、数据分配、队列、累加器、浮点运算控制、浮点运算执行和结果标志寄存器七个模块都写到顶层文件里面,这样就构成了完整的浮点数算术运算系统。

单精度浮点加减运算结果验证,编写testbench测试代码,由总控制器发出命令选中算术运算系统(系统地址总线等于6b111110),依次写入二个单精度浮点操作数32h40166666,32h42aabd71和32h3cc08312,然后写入运算指令32h000010d2(32'b000000000000000000_0100_0011_010_01_0),观察最后的运算结果是否正确,共二个浮点操作数,进行先加后减的运算。仿真结果如图3所示。

从图3中可以看到在8600ns后结果为32'h42af640b。也就是单精度浮点数32'h40166666+32'h42aabd71-32'h3cc08312=32'h42af649b(转换为十进制数即2.3499+85.3700-0.0235=87.6964)误差为0.02,表明浮点数算术运算系统可以按运算指令完成运算功能。

单精度浮点乘除运算结果验证,同样再编写一个testbench测试文件,按顺序写入二个浮点操作数32'h40166666,32'h3f8ccccd和32'h40166666,然后写入运算指令32h000038d2换位二进制即32b000000000000000000_1110_0011_010_01_0,同样也是二个浮点操作数,进行先乘法后除法的运算。仿真结果如图4所示

从图4中可以看到在90O0ns结果为32h3f8ccccc。也就是单精度浮点数32h40166666X32h3f8ccccd÷32h40166666=32h3f8ccccc(换十进制数即2.3499×1.1÷2.3499=1.0999),误差为0.0001,表明浮点数算术运算系统可以按运算指令完成运算功能。仿真验证结果表明所自主设计的浮点数算术运算系统满足运算要求。算术运算系统的资源使用情况如表4所示,浮点算术运算系统在编译后占用了总逻辑单元的18%,片内存储器使用量占用了不到1%。

参考文献

[1]何星宏,阴亚芳,戴程.浮点及整数混合运算器的设计与实现[J].微电子学与计算机,2018,35(02):52-60.

[2]张玲玲,李克俭,蔡启仲.基于FPGA自主控制浮点加减乘除控制器设计[J].计算机测量与控制,2014,22(10):3375-3380.

[3]张素萍,李红刚,张慧坚,董定超.单精度浮点运算单元的FPGA设计与实现[J].计算机测量与控制,2011,19(05):1178-1183.

[4]Tsoumanis,K,Xydis S,EfstathiouC,et a1.An Optimized ModifiedBooth Recoder for Efficient Designof the Add-Multiply Operator[J]Circuits and Systems I:RegularPapers,IEEE Transactionson,2014,Vol.61(4),pp.1133-1143.

[5]李光赫.高性能向量协处理器的运算单元设计与FPGA实现[D].天津:天津大学,2016.

[6]戴丹丹.基于FPGA浮点运算器的研究[D].内蒙古自治区:内蒙古大学,2012.

[7]武迎飞.基于FPGA的浮点运算加速方法的研究[D].天津:河北工业大学,2014.

[8]李克俭,李洋,柯宝中,雷琳.基于FPGA的寻址与运算操作数存储IP核设计[J].广西科技大学学报,2017,28(04):72-79.