基于飞腾1500A/4的嵌入式操作系统适配技术

2018-02-25张静李娟

张静 李娟

摘要 以国产处理器飞腾1500A/4多核处理器为硬件平台,通过分析处理器的硬件特征以及国产嵌入式实时操作系统的体系结构,提出了基于飞腾1500A/4的锐华国产嵌入式实时操作系统处理器支持包适配技术,详细介绍了关键功能模块的实现方式,对提升我国国产软硬件的自主可控水平具有重要意义。

【关键词】飞腾1500A/4 锐华 嵌入式实时操作系统CSP

飞腾1500A/4处理器是国防科技大学自主研发的国产处理器芯片,主频1.5GHz,兼容ARMV8指令集,集成4个SMP架构的xiaomi处理器核(飞腾C660),支持PCIE、UART、GMAC等丰富的外设接口。

锐华嵌入式实时操作系统是华东计算技术研究所自主研制的国产嵌入式实时操作系统。产品通过了信息产业部华东工程软件测评中心以及总装备部测评机构的第三方软件测试,支持PowerPC、X86、ARM、国产龙芯、飞腾等主流处理器,且目前已经在多种军事装备中广泛应用。

1 锐华嵌入式实时操作系统

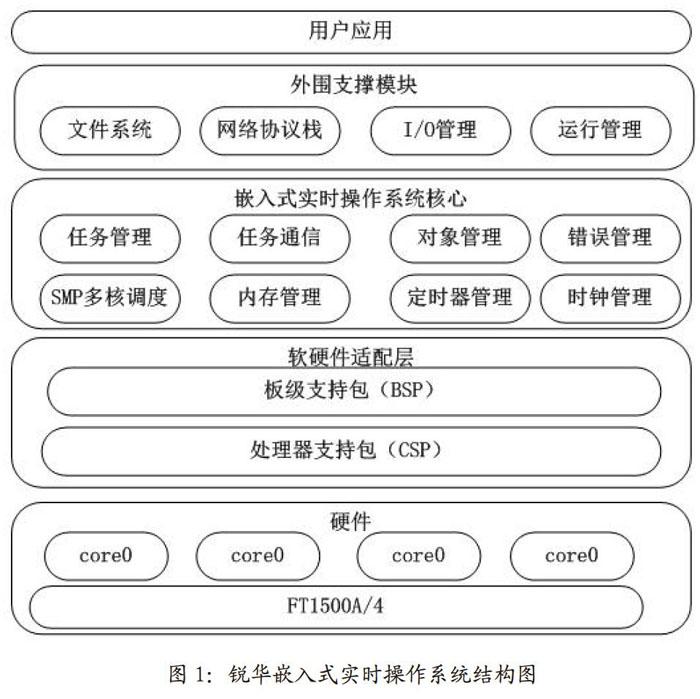

锐华嵌入实时操作系统具有强实时、可裁剪、可扩展等特性,其结构如图1所示。

锐华嵌入式实时操作系统组成分为:

1.1 软硬件适配层

主要包括处理器支持包河板级支持包,实现针对处理器及板卡的初始化、任务上下文切换管理、中断/异常管理管理以及设备驱动等功能,屏蔽底层硬件区别,为操作系统提供统一接口。其中处理器支持包与CPU类型密切相关。

1.2 嵌入式实时操作系统核心

嵌入式实时操作系统核心提供强实时内核,支持实时调度、内存管理、时钟管理、定时器管理等功能,支持SMP多核并行处理架构,提供任务管理、任务通信、对象管理等操作系统功能,提供符合POSIX规范的操作系统接口。

1.3 外围支撑模块

外围支撑模块主要包括文件系统、网络协议栈、I/O管理等功能,为用户提供统一的文件、字符设备、塊设备以及网络设备操作接口。运行管理提供动态加卸载功能,可灵活加载用户应用,并提供实时监控功能。

本文主要研究内容为处理器支持包的实现,研究实现基于国产飞腾1500A/4处理器的软硬件优化适配技术。

2 处理器支持包

处理器支持包主要实现操作系统对飞腾1500A/4国产处理器的优化适配,为操作系统核心提供统一实现接口,屏蔽处理器体系结构差异,是本设计中的主要研究内容。

飞腾15 00A/4兼容ARMV8指令集,支持SMP架构。本设计中操作系统为32位地址空间模式,因此飞腾1500A/4工作在32位模式即ARM AArch32模式,设计中采用兼容ARMV7的32位指令集。

基于飞腾1500A/4处理器的处理器支持包适配关键技术为:

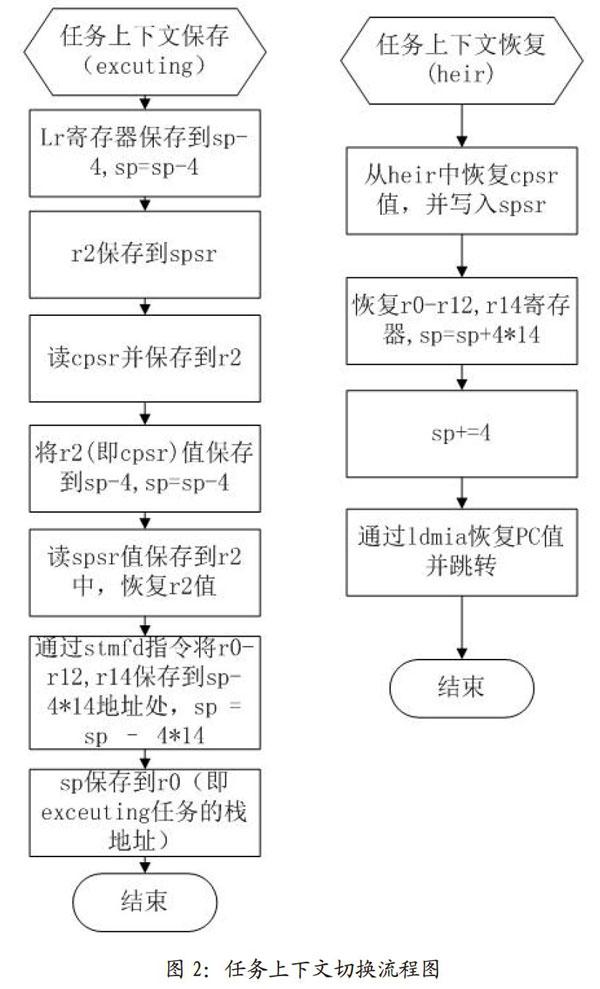

2.1 任务上下文切换

任务上下文切换是操作系统多任务运行的关键,在任务切换时将当前运行任务的寄存器保存在堆栈中,在任务恢复时将之前保存的任务上下文恢复使任务继续运行。由于操作系统运行过程中任务切换频繁,因此该部分功能的实现要高效、简洁,在本设计中采用汇编语言实现。

通过Context Ctrl结构体保存任务运行时所需的寄存器值,使用Context_Ctrl *excuting和heir分别表示任务切换时正在运行的任务和将要运行任务的寄存器地址。飞腾15 00A/4处理器在AArch32模式下需要保存的寄存器主要为:rO—rl0,fp,r12,lr(r14)、cpsr和pe值,其中cpsr为处理器当前状态寄存器,本设计中主要用来保存任务切换时的中断使能状态(cpsr bit7),pe值(r15寄存器)为保存任务切换时刻的运行地址。在SVC模式下,基于飞腾1500A/4的任务上下文切换流程图如图2所示。

2.2 中断处理

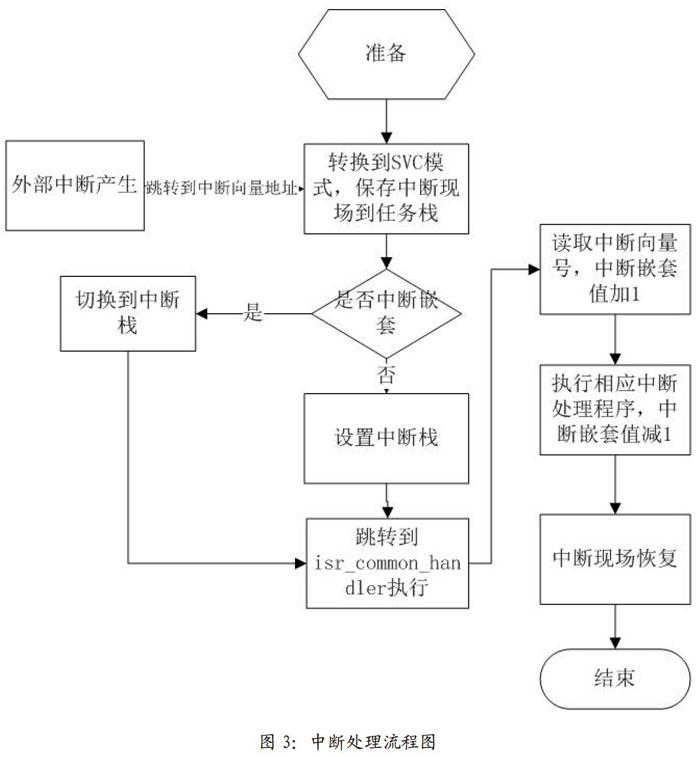

飞腾1500A/4处理器的中断处理设计关键部分为:

(1)中断向量表地址设置及初始化;

(2)中断现场保存及恢复。

在中断使能前,需要设置VBAR寄存器以确定中断向量表地址,即系统产生中断/异常时的跳转地址。然后将中断处理程序拷贝到设置的向量表地址处,以实现对中断现场保存和恢复以及中断的处理。

为保证实时操作系统的中断响应时间,中断现场保存及恢复采用汇编语言实现,且中断服务程序尽可能短,以避免系统锁中断时间过长而影响实时性。基于飞腾1500A/4的中断处理流程如图3所示。

中断返回时,如果没有更高优先级的任务,则直接恢复到被中断打断的任务中运行;否则切换到更高优先级的任务中运行。

2.3 多核同步与互斥

基于飞腾1500A/4多核处理器的同步于互斥主要实现多核操作系统的完整性保护,防止一个程序对资源进程访问的过程中,该资源又被其他程序访问、引用或修改。针对飞腾1500A/4处理器,需要研究实现适用于多核系统的底层同步原语,主要为原子操作、自旋锁、以及内存屏障。

飞腾1500A/4处理器提供“不可被中断的”原子操作指令ldrex和strex,分别用来取和存内存中的数据。本设计中通过该对指令实现基本的原子操作,如原子加、减、设置、获取、原子与、清除等。

为了保证读内存和写内存完全按照顺序执行,飞腾15 00A/4处理器提供内存屏障指令“dmb”,基于该指令实现内存读屏障、写屏障和读写屏障。

锐华操作系统在获取自旋锁和释放自旋锁之间采用完全内存屏障,保证读内存和写内存完全按照顺序执行,通过原子操作指令设置和获取自旋锁的状态。根据不同的使用场景,多核操作系统中的设计了禁止抢占的自旋锁和禁止中断的自旋锁。为保证实时性,禁止中断的自旋锁根据应用场景又分为公平自旋锁和非公平自旋锁。公平自旋锁针对需要高性能自旋锁同时对公平性和确定性要求较高的应用场景,非公平自旋锁针对需要高性能自旋锁但是对公平性和确定性要求相对不高的应用场景。

3 结语

以国产飞腾1500A/4多核处理器为硬件平台,通过分析国产锐华多核嵌入式操作系统及处理器的硬件架构,提出了机遇锐华操作系统的飞腾1500A/4处理器优化适配关键技术及实现方式。目前,基于飞腾1500A//4的锐华嵌入式操作系统已经在项目中进行应用,满足用户应用需求,为其他嵌入式操作系统在飞腾处理器上的适配具有一定的参考作用,对国产处理器及嵌入式操作系统的应用推广具有重要意义,进一步提升我国基础软硬件的自主可控水平。

参考文献

[1]赵星星,罗克露,张军等,嵌入式实时操作系统移植技术的研究与应用[J].计算机工程,2007,33 (17): 90-92.

[2]Jean J.Labros se著,邵贝贝等译.嵌入式实时操作系统μC/OS-II(第二版)[M].北京:北京航空航天大学出版社,2003.

[3]周民军,基于ARM的嵌入式操作系统的设备驱动程序设计[D].武汉:武汉理工大学,2010:1-3.

[4] PHYTIUM飞腾.FT-15 00A/4数据手册Vl.5 [Z].2016.

[5] ARM. Arm architecture ReferenceMannual ArmV8, for Armv8-Aarchitecture

profile [Z]. 2013. http://www.arm.com.