基于CRO的低相噪频率合成器设计

2018-01-30张海拓

张海拓

摘要:频率合成器是现代电子系统的重要組成,本文采用同轴陶瓷介质振荡器(CRO)进行了压控振荡器(VC0)设计,给出了频率合成器的实现原理和设计方法,实现了低相噪的频率合成器模块,并对其性能进行了测试。

【关键词】频率合成 锁相环 介质振荡器 相位噪声

1 概述

频率合成器是被称作现代通信系统的心脏,它对整个系统的性能指标起决定作用,广泛应用于数字通信、卫星通信、雷达、导航、航空航天、遥控遥测以及高速仪器仪表等领域。频率合成的方法有多种,具体采用那种方法实现,要根据实际工程需要进行选择。相位噪声频率合成器的关键指标,是衡量输出信号相位抖动大小的重要参数。随着数字通信的应用越来越广泛,研制具有低相位噪声的频率合成器具有十分重要的意义。

2 工作原理

锁相式频率合成技术,是在四十年代初根据控制理论的线性伺服环路发展起来的,它是目前频率合成器的主流,本文采用该方案进行设计。在锁相式频率合成器中,锁相环路相当于一窄带跟踪滤波器,能很好地选择所需频率的信号,抑制杂散分量,且避免了大量使用滤波器,十分有利于集成化和小型化。一个设计良好的压控振荡器具有高的短期频率稳定性,而标准频率源具有高的长期频率稳定度,锁相式频率合成器把这二者结合在一起,使其合成信号的长期稳定度和短期稳定度都很高。

构成锁相式整数频率合成器的关键部分是锁相环,它是一个相位误差控制系统,通过比较输入信号和压控振荡器输出信号之问的相位差,产生误差控制电压,调整压控振荡器的频率,以达到与输入信号同频同相。

压控振荡器(VCO)是锁相环频率合成系统的重要组成部分,在微波频率范围内的低频端,常采用集中元件构成振荡器,基本的振荡器电路组态有三种:考毕兹型、哈特莱型及克拉泼型振荡器。考毕兹型(a)用一电容器作为调谐电路中的分压器,哈特莱型(b)用一抽头式电感调谐电路,而克拉泼型振荡器(c)则相似于考毕兹型,不同的是另外用了一只电容与电感相串连,以改善频率稳定性。加入反馈网络的目的,在于增加负阻电阻值,以获得最佳功率输出。

3 设计方案

本设计需求是输出频率为1600MHz的信号,相位噪声是需重点关注的关键指标。相位噪声与环路带宽密切相关,环路带宽内的相位噪声主要由输入噪声决定,而环路带宽外的相位噪声则主要由VCO的相位噪声决定,环路带宽也与鉴相频率有关,一般不超过鉴相频率的1/5。要注意倍频对相位噪声的影响,倍频将会造成参考信号相位噪声的恶化,恶化的程度为20logN,其中N是分频器的分频比,也就是锁相频率合成器的倍频数。

本设计对VCO相位噪声要求较高,传统的三点式振荡器中,电感一般是相位噪声提高的制约因素。终端短路结构的CRO器件在自谐振频率以下可等效为高O值的电感,可用来进行高性能压控振荡器的设计。

本文采用ADI公司的单片集成锁相环芯片ADF4113作为锁相环电路的鉴相器,通过环路滤波器和压控振荡器电路的设计,实现了低相噪的频率合成器。

3.1 压控振荡器(VC0)设计

本设计中的VC0的结构简单介绍如下,该电路是在克拉泼电路结构上做一定改动后的西勒振荡结构,该结构由于在电感的两端并联一个电容,更利于调节和起振。三极管采用NE68519,在低电源低电流下具有较高的增益。Rl,R2和R3,R4为三极管提供偏置,Ll起到扼流的作用,CI,C2提供反馈回路,CSER与L2,CVAR,Cl,C2提供谐振频率。CVAR -般采用变容二极管实现,通过调节CVAR两端的电压实现频率调节。

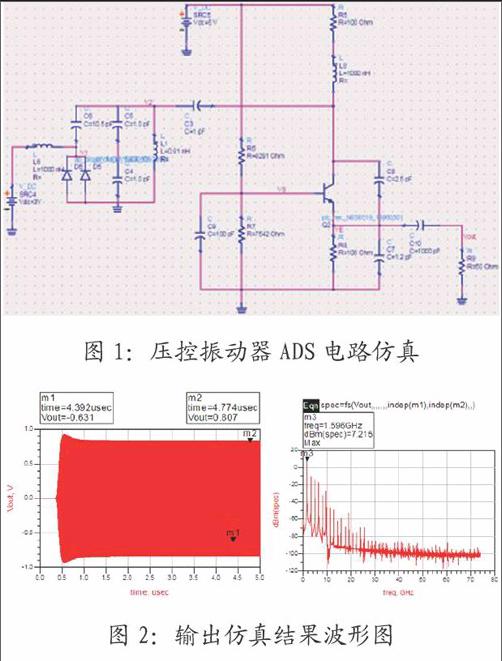

图1为仿真电路,设计参数如图所示,采用ADS2008对上述电路进行仿真,由图2可知,设计实现了振荡功能,压控电压为3V时,输出频率为1.596GHz,调试时对电容微调即可得到需求的1.6GHz。

3.2 环路滤波器设计

采用ADI公司的锁相环仿真软件ADIsimPLL进行设计和仿真,采用四阶环路滤波器设计,可有效抑制参考杂散。设计时输入参考频率为10MHz,VC0使用ADS仿真的结果,环路带宽可设置为5KHz,相位余量为45°。

4 实现及测试

根据以上仿真优化结果,在FR-4介质板上制作电路,用Agilent N9030A信号分析仪对设计的频率合成器进行测试。通过测试结果,可以看出,其实现的相位噪声指标较高,达到了-llldBc/Hz@lOkHz,-128dBc/Hz@lOOkHz,-142dBc/Hz@lMHz,满足设计要求。

5 结束语

本文根据使用需求,通过理论分析进行了低相位噪声频率合成器设计,试验情况表明,同轴谐振振荡器(CRO)在自谐振频率下,比电感具有更高的温度稳定性和更高的0值,采用CRO进行锁相环电路中的压控振荡器设计,可实现低相位噪声的频率合成器产品。

参考文献

[1]邱迎锋,刘光斌,频率合成技术:历史、现状及发展[J],工业仪表与自动化装置,2005(05),12-14.

[2] Dean Banerjee, PLL Performance, Simulation, and Design (4th Edit ion)。2 006.

[3]Lance Lascari, Accurate Phase Noise Prediction in PLL Synthesizers, Applied Microwave&Wireless. PP: 30-38.endprint