基于FPGA与AD5422的PLC模拟量扩展单元的设计

2018-01-22鲍长君

鲍长君

摘要:本文设计了一种以FPGA为核心,基于AD5422实现多路高精度输出的PLC模拟量扩展单元模块。设计先对现有的方案进行了分析和讨论,之后对FPGA内部相关处理机制和实现方案做了详尽的论述,经过仿真和测试验证了设计的可行性。相比于传统的模拟量扩展单元模块,本系统具有处理速度快、方便、灵活,电路精简,抗干扰能力强等优点。

关键词:FPGA;AD5422; 串行外设接口

DOI: 10.3969/j.issn.1005-5517.2017.8.014

1 系统总体设计

1.1方案论述

工业自动化控制系统经常需要用到4-20mA或者±5V等模拟量信号,用以控制变频器等需要模拟信号输入控制的设备,而模拟量扩展单元也是PLC产品重要的扩展单元之一。一个良好的模拟量扩展单元产品的设计希望不仅能够保证系统运行的可靠性,还希望系统设计能够非常精简,有足够的鲁棒和可扩展性,在成本性、能等各方面组合成一个最优的结果。是PLC模拟量扩展单元产品设计一直追求和努力的方向。

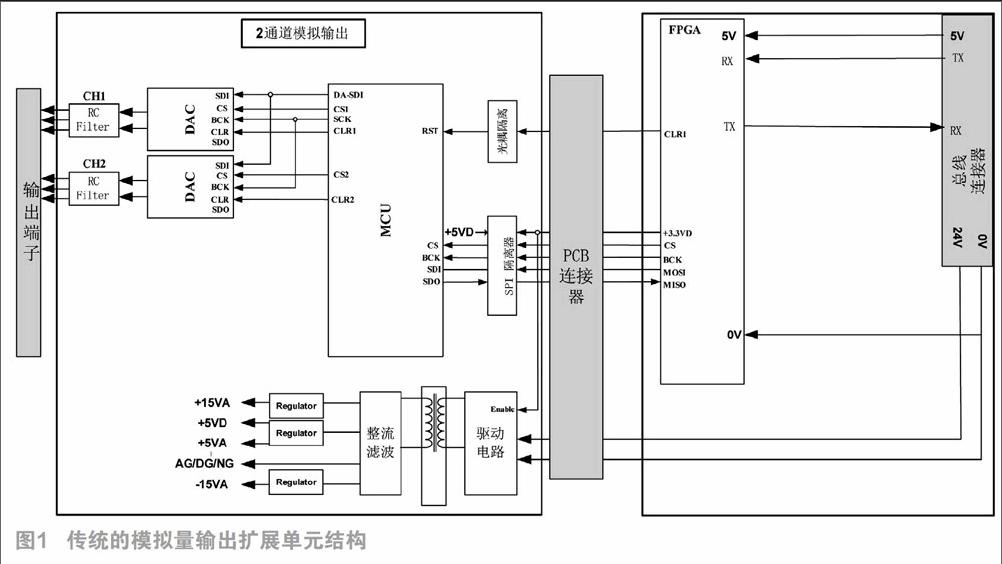

传统的模拟量输出扩展单元结构如图1,其工作原理是:1、FPGA将扩展通信总线上的数据通过SPI通信隔离器进行电器隔离,然后将数据交互给MCU;2、由MCU负责数据的转换和进行相关的配置工作,并通过MCU的SPI接口控制输出的DAC获得相应的模拟电压或者电流输出值。

不难看出,FPGA和MCU之間通过SPI通信,MCU和DAC之间也通过SPI通信,如果我们能把MCU的工作都集成到FPGA内完成,那方案就可以省略MCU,由FPGA直接控制DAC实现功能。但是在省略MCU前要对现有方案做以下进一步的分析。

1.2 实现多DAC的SPI接口级联方式

在使用传统MCU控制DAC的回路设计时,MCU有足够的IO口可以单独或者级联控制DAC芯片,但是如果换用FPGA来直接替换MCU控制,则会因为需要更多的数据隔离通道使得物料成本上升,因此,若想FPGA直接控制DAC,则最好所有的DAC能进行级联设计,即通过一个SPI隔离器和少数光耦实现全部的通信和控制功能。

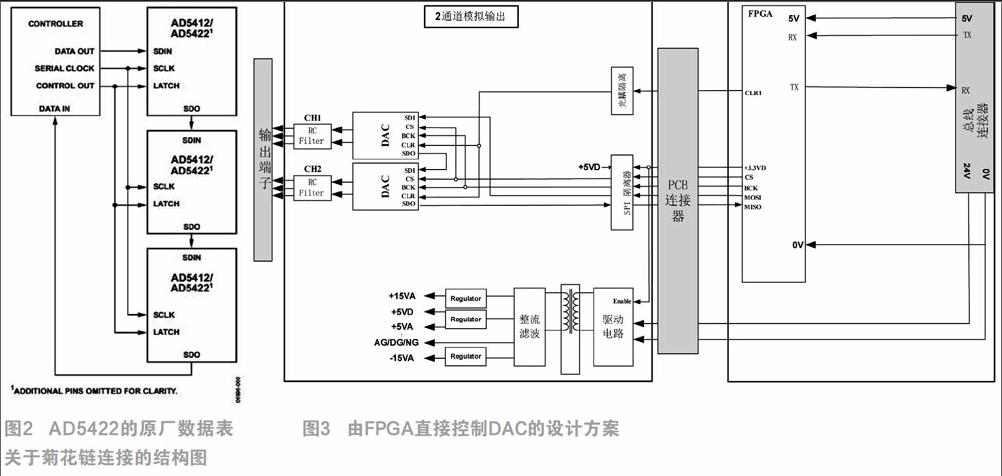

参考AD5422芯片数据手册,实际上该芯片具有多片菊花链连接方式,只要设计得当,多个DAC就可以在同一个SPI接口上级联工作,图2是AD5422的原厂数据表关于菊花链连接的结构图…。

1.3 每个DAC的硬件清零信号处理方法

应对开机复位或者某些紧急情况,DAC需要实现硬件清零工作。关于DAC硬件清零脚的设计,我们可以用FPGA闲置的IO脚通过光耦隔离后来控制它。当然若想每个DAC都可以独立完成清零的工作,则需要由软件通信的方法控制相应的寄存器来实现软件清零。

1.4 MCU需要完成的任务内容

从PLC编程给模拟量输出扩展的数据以及相应的AD5422原厂数据表看, MCU需要在这个中间环节完成以下几个任务:

1)复位,取消复位,清零,初始化DAC芯片;

2)拆分SPI数据,完成各DAC量程,输出使能等相关的配置工作:

3)完成数据转换:包括单极性和双极性数据转换,数据位数扩充,数据加偏移量等工作;

4)完成DAC状态相关回读工作,包括DAC电流输出断线报警,芯片过热等异常情况。

1.5 FPGA直接控制DAC的设计方案

综合以上的设计分析,我们修改了整体硬件设计方案,由FPGA直接控制DAC的设计方案如图3所示。这样MCU要完成的工作就必须在FPGA内处理完成[2]。

2 FPGA内部具体设计实现的方案

2.1 FPGA的数据处理流程

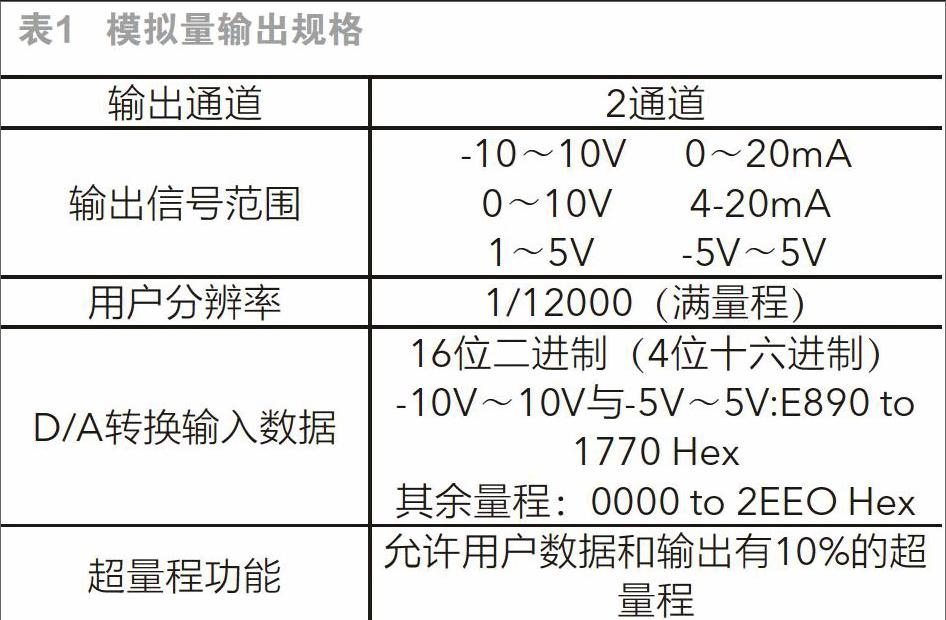

表1列举了模拟量输出规格,包括量程、用户分辨率、用户编程的数据范围等。

可见因为我们给PLC编程的数据和最终送给AD5422芯片的数据有一定的区别,则对于数据处理来说,我们需要完成以下几个功能:

1)识别数据有效性:PLC给用户1/12000的分辨率和控制字并不能占用OxOOOO-OxFFFF全部范围内的数据,也就是说存在一部分的输入数据是非法的无效的,需要在经过处理前识别出来,避免后续处理出错,FPGA设计通过数据比较输出数据有效或者无效判断,当然设计可以选择无效数据丢失或者输出报警信号。

2)双极性转换: 对应双极性输出数据中的-10-+10V的数据范围是十六进制的OxE890到Ox1770对应十进制的-6000到+6000,而AD5422的-10V-+1 0V对应的数据范围是十六进制的Ox000-OxFFFF是单极性的,所以先要给双极性的原始数据加上十进制的6000,统一输入为十六进制的Ox0000-Ox2EEO,对应十进制的0-12000。

3) 数据扩充:通过乘法器实现输入数据的扩充,从给用户的十六进制Ox0000-Ox2EEO需要对应转换到十六进制OxOOOO-OxFFFF。特别地,对于1-5V量程来说因为输出有个1V的基准量,在适用AD5422的0-5V量程时通过扩展到AD5422对应的0-4V量程,即十六进制的OxOOOO-OxCCCC,当然,这一步的处理需要在FPGA内部设计硬件乘法器,使得每个量程都能乘上响应的系数完成数据扩充工作。

4)添加偏移量:对于1-5V量程来说这个1V的基准量是始终存在的,这就需要在完成数据扩充后添加偏移量,其他量程则不需要这个偏移量的添加。

2.2 FPGA其余需要添加的功能块还包括

1)控制字识别模块:针对获得的命令控制字,需要能甄别,并且分离出每个通道的量程和使能信息,在获得合法的控制字后才能通知初始化模块开始正常的数据运行。对于非法的控制字信息也能报错并停机。endprint

2)初始化模块:在上电后初始化每一个DAC芯片,包括复位芯片,开启菊花链使能,清空输出数据寄存器等操作I1)。

3) SPI接口模块:该模块能自动的将处理完成的数据添加字头地址并发送,而且能够配合初始化模块完成DAC的初始化工作。在完成数据发送后最好还可以自动回读DAC的状态信息了解DAC是否过热,电流环开路等信息。在处理完成所有工作后,自动的提供一个帧复位信号给状态机完成一帧数据的处理工作。

4)时钟控状态机:该模块能协调每个模块的工作顺序,使这个机制在数据帧能顺利工作并且自动复位。

5)通道识别模块:对于多通道数据使用同一个数据处理线来说,要有效的识别通道,通知各模块装载对应的量程控制字和控制SPI模块的菊花链数据装载顺序。 图4是FPGA内部整体处理机制的结构图。

3 FPGA仿真测试

通过Verilog HDL语言编写相关的硬件描述语言模块,并综合生成实例。图5是FPGA内部实现DAC数据转换处理的实例模块,也是本设计的核心模块,其相应的输入端口包括:模块复位rst-n;模块主时钟输入mclki:通道1的总线送来的十六位数据BUSdatal[15:0];通道2的总线送来的十六位数据BUSdata2[15:0];2个DAC通道的配置数据(包括量程和使能信号)configdata[7:0];转换使能信号sta rt;相应的输出信号包括送往SPI通信模块发送给DAC1的数据Txdatal[15:0];发送给DAC2的数据Txdata2[15:0],以及转换完成的使能信号TXok。

使用ModeISim軟件对FPGA内部的处理机制进行仿真测试,图6是SPI端口对DAC进行初始化的时序仿真结果。包括发送Ox560001进行复位功能,发送Ox560000取消复位功能,发送Ox550008开启菊花链使能等操作。

图7显示了FPGA内部数据转换的仿真测试结果,我们先预设了DAC工作在-10-10V量程下,并在该模式下给FPGA送入十进制的6000对应Ox1770代表要求DAC输出正10V满量程,计算结果输出是有符号数的Ox7FFF,说明和预期结果一致,即这部分功能模块可以正常工作。

样机测试使用Microsemi的FPGA为处理核心,使用Libero SoC开发平台下移植了以上设计进行实体电路的运行,图8为样机的实物照片,左边为顶层FPGA板,右边为底层模拟量输出板。其中模拟部分的硬件设计可以参考EVAL_AD5422[3]。另外,注意要做好输出ESD保护对策。图9显示了该样机输出O-10V階跃信号的实测波形,验证了设计的可行性,完成了相关产品的开发任务。

4 结论

本设计凭借FPGA强大的硬件可编程能力,在硬件设计方面直接省略了一颗MCU处理器及相关配套的硬件,既可以极度的精简物料表。提升整体硬件可靠性,降低系统功耗,又不用担心MCU会存在死机等实际运行的风险。

对于数据处理交由FPGA来实现,既可更严格的管理完善整体系统运行的时序。而且输入输出数据的关联性更差,这样整个设计具有更好的保密性。利用FPGA的灵活性,使电子设计能够在很短的周期内完成[4],而且FPGA内部设计硬件乘法器,加法器等硬件模块可以极大的提升数据处理速度,从而提升系统响应时间[5]。

参考文献:

[1]AD5422 Datasheet[Z] Analog Devices, Inc

[2]于笑凡,费树岷基于FPGA与AD5422的多功能信号发生器的设计[J]信息技术与信息化,2013(6)53-55

[3]UG-422:Evaluating the AD5422 Single Channel.16Bit.Current Source and Voltage OutputDAC.HART Connectivity.[Z] Analog Devices, Inc

[4]王珏文,金伟信,蔡一兵,等基于FPGA的SPI总线接口的实现叫现代电子技术,2010(14):102-104

[5]周维龙基于FPGA的智能变送器的设计与开发[D]长沙:湖南大学,201018-22endprint