符合ccsds标准的遥测同步和信道编码系统及FPGA实现

2018-01-18赵文剑王竹刚

赵文剑 ,王竹刚

(1.中国科学院大学北京100190;2.中国科学院国家空间科学中心,北京100190)

随着对高效、高可靠性卫星通信系统需求的增长,传统的遥测同步和信道编码系统已经无法满足实际的要求,在复杂多变的空间通信环境中如何降低系统信息传输误码率,实现可靠的信息传输已经成为遥测系统需要解决的关键性问题[1]。依照CCSDS制订的分包遥测标准[2]体系中同步和信道编码标准[3-8],文中在FPGA平台上实现了一套遥测编码系统。整个遥测同步和信道编码流程可以概括为:首先,信道编码使用LDPC码,它具有接近香农极限的误码性能和较高的编码增益,适用于空间探测、载人航天等空间应用领域[9];然后,数据加扰采用和伪随机序列做相关运算的方法,它保证了信道的转变密度,避免了长时间出现‘0’或‘1’[10];其次,加扰后的数据添加相对应的同步码,构成适合于分包遥测体系传输的遥测信道数据访问单元(Channel Access Data Unit,CADU),再进行物理层的基带、中频和射频处理,最后送入物理信道进行传输。

1 符合CCSDS标准的遥测同步和信道编码

1.1 LDPC(2048,1024)编码

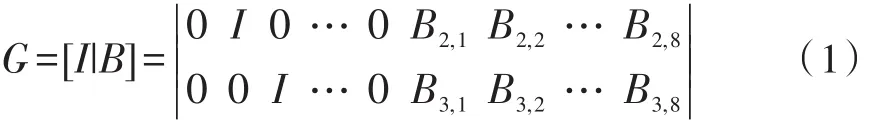

LDPC码可以获得较高的编码增益,在卫星通信场合具有很好的应用前景[11]。本设计中采用了LDPC(2048,1024)码,又称1/2码率LDPC码。这是一种准循环LDPC码(Quasi-Cyclic Low Density Parity Check Code,QC-LDPC),可对 1024个信息比特编码,并输出2048位码字,常应用在深空通信场合。该码的生成矩阵G具有系统循环结构,维数是1024×2048,结构如式(1)

式(1)中,矩阵左边是一个1024×1024的单位方阵,右边是8行8列共64个128×128的循环子矩阵块Bij构成的1024×1024维矩阵。Bij的每一行由其上一行向右循环移位1位构成,第一行是最后一行的循环移位,因此存储生成矩阵简化为存储其生成向量,可以节约大量的存储资源。

1.2 伪随机化

为了保证信道的转变密度,避免长时间出现‘0’或‘1’,使用生成多项式h(x)=x8+x7+x5+x3+1产生周期为255的伪随机序列与LDPC编码之后的比特流相异或,即伪随机化(Pseudo-Randomizer)。因为异或操作具有结合性,假设原始数据为D,用来加扰的伪随机序列为P,随机化后的数据为R,则R⊕P=(D⊕P)⊕P=D⊕(P⊕P)=D⊕0=D。因此,地检设备解帧时只需用同样的伪随机序列再次与除同步码以外的每一位进行异或,即可恢复原数据[12]。

1.3 附加同步码(Attached Sync Marker,ASM)

为了实现帧定界,方便接收端帧同步,经LDPC编码和伪随机化后的每帧数据需附加相应的同步码,依据标准建议,对应LDPC(2048,1024)编码的同步码为64比特,其十六进制表示为034776C7272895B0[13]。综上所述,整个遥测同步和编码的数据封装过程如图1所示。

2 FPGA实现

2.1 LDPC(2048,1024)编码器

已知信息码序列M和式(1)生成矩阵G,可由式(2)求得码字序列A。

图1 遥测同步和信道编码数据封装过程

其中M为输入信息序列,I为式(1)中单位矩阵,B为式(1)中的循环矩阵,C为校验序列,编码后的码字序列A由输入信息序列M和校验序列C两部分组成。由式(2)可知,(2048,1024)LDPC码的编码实际上仅需要计算校验序列C=M×B[14]。矩阵B的每个块矩阵具有循环特性,存储生成矩阵时只需存储每个块矩阵的第一行,依次向右循环移位即可得整个生成矩阵,因此,原本需要1024×1024个存储空间,现只需128×64个存储空间。下面推导编码运算公式:记Bi,j=[bli,j(k)],其中i,j=1,2,…8表示8行8列块矩阵;k=1,2,……,128表示每个块矩阵的128列元素;l=0,1,…,127表示每个块矩阵的行元素向右循环移位的位数。M(j)表示输入信息的第j比特位;R(n),n=1,2,…1024表示1024个1024维矢量信号。

当输入第1比特信息M(1)时,M(1)与B第1行全部元素相乘,结果为:

当输入第2比特信息M(2)时,M(2)与B第2行全部元素相乘,结果为:

当输入第j比特信息M(j)时,M(j)与B的第j行元素全部相乘,结果为:

其中,“%”表示求余,“/”表示整除所得的商。

综上,记accv(v=1,2,…,8)表示8个128位校验码寄存器,acc表示1024位的校验码寄存器则

其中,“{}”表示8个128比特的accv寄存器拼凑为1024比特。

根据式(3)~(6)的计算过程,校验序列的计算电路设计如图2所示,利用循环移位寄存器、乘法器及异或累加器为核心实现向量与矩阵的乘法,极大地减少了运算量和资源消耗,有利于编码器的硬件实现。

图2工作过程如下:

图2 LDPC编码电路

1)初始时刻128位循环移位寄存器cshift1、cshift2…cshift8分别读入G中B1,1,B1,2…,B1,8的第1行数据其中k=1,2,…,128 。同时与第1位信息位M(1)进入与门做乘法,再由异或门相加后分别存入acc1,acc2,…,acc8;

3)重复步骤2);

4)当M(128)输入电路并运算完成后,移位寄存器cshift1、cshift2…cshift8分别读入G中B2,1,B2,2…,B2,8的第1行数据与第129位信息位M(129)进入与门做乘法,结果分别与acc1,acc2,…,acc8中的值相异或后存入acc1,acc2,…,acc8。

重复上述过程直到信息序列M的最后一位M(1024)进入电路运算完成后,取出acc1,acc2,…,acc8中的值,赋值给校验码寄存器acc,即acc={acc1,acc2,…,acc8},所得即为LDPC编码的校验码字。

2.2 伪随机

生成多项式h(x)=x8+x7+x5+x3+1产生周期为255的伪随机序列与LDPC编码之后的2048比特信息逐位异或,实现帧数据加扰。伪随机电路使用如图3所示的线性反馈移位寄存器(Linear Feedback Shifting Register,LFSR)实现:

图3 伪随机化电路

初始化时,8位寄存器置‘1’,伪随机序列的每位输出与LDPC编码后码字相异或同时返回LFSR中参与后一位随机位的生成运算,一个周期即255个时钟周期之后,LFSR寄存器呈全‘1’,接着重复上一个周期的输出,直至整帧数据完全加扰,即完成一帧数据的处理[15]。

2.3 帧同步

伪随机之后的2048比特信息码附加64位同步码构成2112比特标准数据帧。每一帧数据经过LDPC编码和伪随机处理后输出一个时钟周期的脉冲信号,ASM电路接收到该脉冲后,将64位同步码打进64位移位寄存器,下一个时钟即输出同步码最高位,同时将伪随机后生成的信息码逐位移入64位移位寄存器,从而实现CADU码流的串行输出,ASM电路实现如图4所示。

3 测试结果及分析

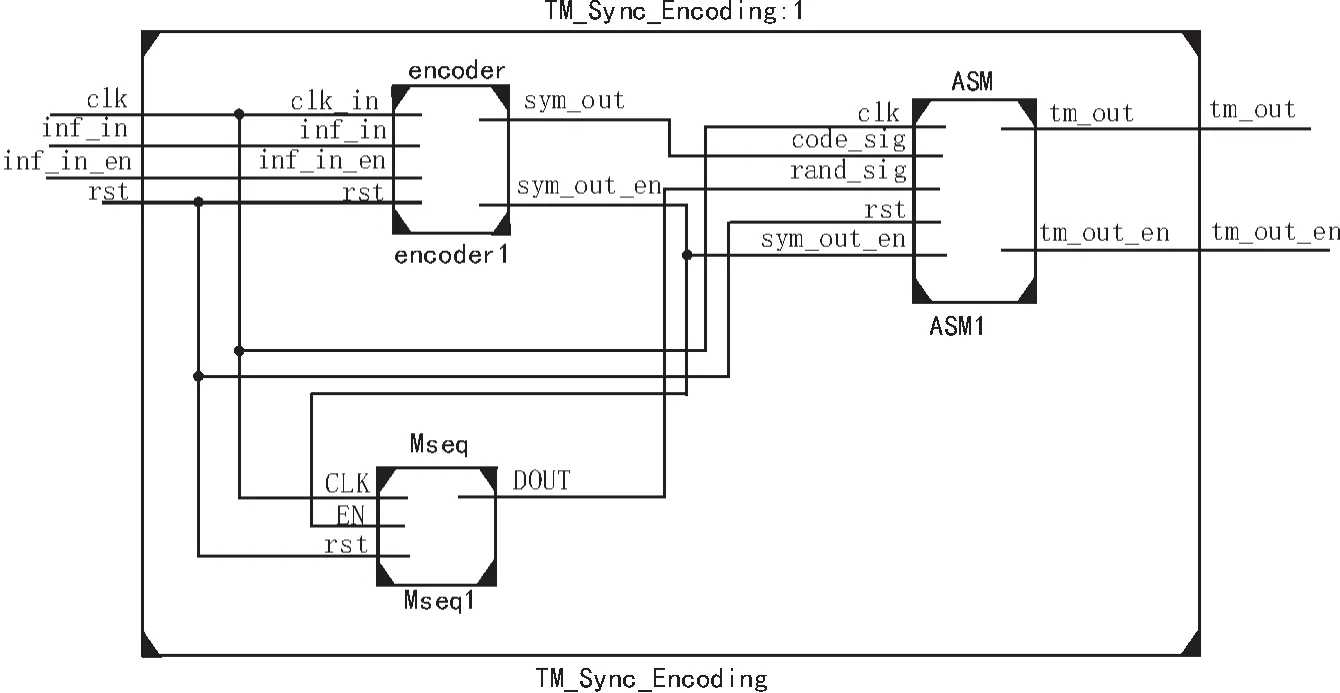

本设计使用Xilinx公司的xc4vsx55芯片实现,并在ISE14.6环境下使用Verilog HDL完成电路设计、综合、布局布线及程序下载。本系统的实现结构图如图5所示,clk为时钟信号;rst为系统复位信号,高电平有效;inf_in为串行输入数据;inf_in_en,输入数据有效标识信号,高电平有效;tm_out为串行输出数据;tm_out_en,输出数据有效标识信号,高电平有效。

设计中遥测同步和信道编码系统综合后的FPGA资源使用情况如表1所示,可见,系统在占用较少资源的情况下,实现了同步和编码功能,大大节省了资源消耗。

图4 帧同步电路

图5 遥测同步及信道编码系统结构

表1 遥测同步及信道编码系统资源占用

系统吞吐量Throughput的计算公式如式(7)所示,其中n表示一帧待处理信息数据的比特数,c表示完成一帧数据处理所需的主时钟周期数,T表示系统时钟[16]。

由表1,当系统工作频率为150 MHz时,对于1个数据帧,从第1个信息比特输入,到CADU最后1个比特数据输出,实验结果表明一共需2 120个主时钟周期,即c=2 120。系统中数据帧包含的信息比特数为1 024,则由式(7)计算的吞吐量约为72 Mbps。

4 结论

文中依照CCSDS分包遥测标准建议,在FPGA平台上实现了一套遥测同步和信道编码系统。该系统应对复杂多变的空间环境,具有较高的数据传输可靠性,同时硬件实现简单,数据吞吐量高,在占用资源较少的情况下,能准确完成遥测数据的同步和信道编码任务,满足深空通信要求。

[1]Lin S,Costello D J,Jr.差错控制编码[M].北京:机械工业出版社,2013.

[2]Packet Telemetry.CCSDS 102.0-B-5.Blue Book.Issue 5[S].2013.

[3]TM Synchronization and Channel Coding.CCSDS 131.0-B-2.Blue Book.Issue 2[s].2013.

[4]CCSDS.CCSDS130.0-G-3Overviewofspacecommunicationsprotocols[S]. Washington D.C.:CCSDS Secretariat,2014.

[5]CCSDS CCSDS 355.0-R-4 Space data link security protocol[S].Washington D.C:CCSDS,2014.

[6]CCSDS.CCSDS 732.0-B-3 AOS space data link protocol[S].Washington D.C:CCSDS Secretariat,2015.

[7]CCSDS.CCSDS 230.1-G-2 TCsynchronization and channel coding--summary of concept and rationale[S].Washington D.C:CCSDS Secretariat,2012.

[8]TM ChannelCoding Profiles.CCSDS 131.4-M-1.Magenta Book.Issue 1[S].2012.

[9]郭经.CCSDS遥测信道编码标准简介[J].航天标准化,2012(2):42-45.

[10]马苗,朱岩.基于CCSDS标准的卫星数据处理软件设计[J].电子设计工程,2015,23(1):16-20.

[11]雷光雄,王赛宇.基于CCSDS建议的纠错码技术研究[J].计算机与网络,2015(2):19-25.

[12]杜兵团,赵建功.基于CCSDS标准的高速LDPC译码算法[J].无线电工程.2013(10):59-66.

[13]易茂祥,张浩,郭红卫等.m-序列数据扰码技术及其在SATA中的应用[J].微电子学,2012,42(4):502-505.

[14]谢勇,姚远程,秦明伟.QC-LDPC码编码器的FPGA实现[J].西南科技大学学报,2013,28(1):84-87.

[15]程磊,杜锋,张健.深空通信中LDPC码编码器设计与FPGA实现[J].电子质量,2015(4):34-38.

[16]刘兰,姚行中,王振宇等.适用于CCSDS的“一帧一密”加/解密方案的FPGA实现[J].计算机工程与应用,2015,51(10):84-88.