FPGA的1553B总线编码IP核设计

2018-01-15

(中国空空导弹研究院,洛阳 471009)

引 言

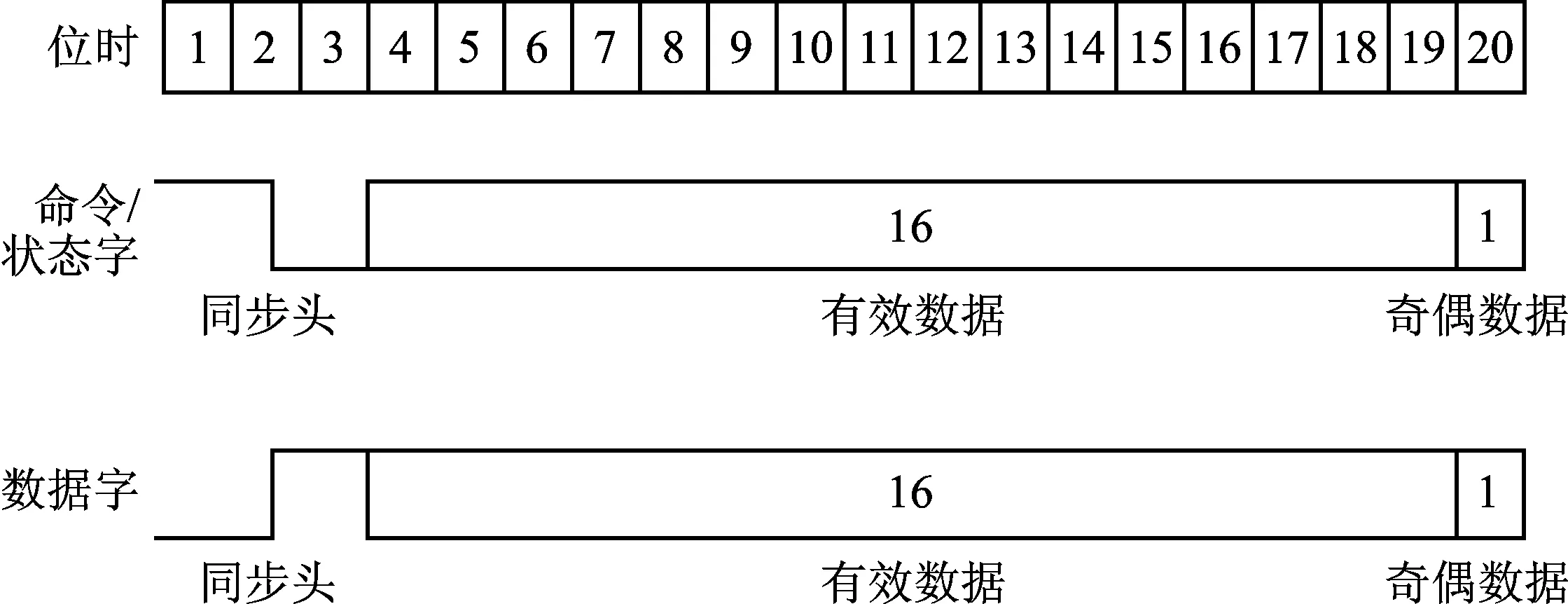

图1 1553B总线数据格式

1553B总线是MIL-STD-1553美国军用标准总线的简称,在飞机的航电系统中得到了广泛的应用[1-3]。目前,为了实现1553B总线的通信,大多是开发独立的通信接口模块,不但成本高,整个系统的重量和体积也会因此增加,不利于航空领域的使用[4-5]。FPGA 近年来在国内发展得非常快,它具有编程方便灵活、集成度高、处理速度快、低功耗等优点[6-8],同时在FPGA内部还集成了ARM硬核、MICROBLAZE软核等微处理器,使得FPGA在嵌入式系统设计中得到了更加广泛的应用。本文将ZYNQ-7000系列FPGA内部的ARM硬核处理器与1553B总线编码IP核结合起来,实现对1553B总线数据的发送功能,从而节约了芯片成本和PCB面积。

1 1553B总线数据格式

1553B总线的数据传输速率可达到1 MB/s,即每一位数据都是在1 MHz的时钟频率下发送和接收的[9-10]。1553B总线发送或者接收的每一个字都包含20位,其中前3位用来区分命令/状态字和数据字,最后一位是奇偶校验位,中间16位是有效数据。前3位同步头在1.5位处有一个跳变,先高后低表示命令/状态字,先低后高表示数据字,1553B总线数据格式如图1所示。

2 1553B总线编码规则

1553B总线采用曼彻斯特II型双相编码的规则进行编码,这种编码方式适用于变压器耦合。曼彻斯特II型双相编码是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。在曼彻斯特II型双相编码中,每一位的中间都存在一个跳变,这个跳变既可以作为时钟,也可以作为数据。先低后高的跳变表示“0”,先高后低的跳变表示“1”。所谓的双相也就是双极性,由于这种双相编码方式本身就包含了自定时信息,因此就不再需要独立的信道携带位定时信息。曼彻斯特II型双相编码如图2所示。

图2 曼彻斯特II型双相编码

3 1553B总线编码IP核设计

3.1 曼彻斯特II型双相编码逻辑设计

曼彻斯特编码逻辑的功能框图如图3所示。

图3 曼彻斯特编码逻辑的功能框图

编码模块输入输出端口如下:① 时钟输入:enc_clk;② 16位并行数据输入:tx_dword;③ 命令/状态字标志输入:tx_csw;④ 数据字标志输入:tx_dw;⑤ 发送忙状态指示输出:tx_busy;⑥ 串行数据输出:tx_data;⑦ 发送数据有效状态指示输出:tx_dval。

编码器需要一个时钟频率为2 MHz的时钟(enc_clk),正好是需要的数据速率(1 MHz)的2倍。编码周期开始于tx_csw或tx_dw脉冲,伴随着命令状态字或者数据字被发送。然后编码器发出tx_busy信号,直到编码器按照所有的编码功能(插入同步头、插入奇偶校验等)连续地将这个字发送出去,最后释放tx_busy来等待接收下一个新字。

首先写入要发送的16位并行数据tx_dword和字标志(命令/状态字标志tx_csw或者数据字标志tx_dw),当检测到有效的字标志(tx_csw或tx_dw)后,就开始将16位并行数据tx_dword转换成曼彻斯特码格式的数据。因为编码时钟频率为2 MHz,所以形成的曼彻斯特码格式的数据为40位。同步头按照有效的字标志(tx_csw或tx_dw)形成,命令字或者状态字的同步头为6’b111000,数据字的同步头为6’b000111。16位并行数据tx_dword的每一位按照“1”对应2’b10,“0”对应2’b01来进行编码,形成32位数据。奇偶检验位采用16位并行数据tx_dword,按位异或的计算形成奇偶检验结果。曼彻斯特II型双相编码仿真波形如图4所示。

图4 曼彻斯特II型双相编码仿真波形

3.2 1553B总线编码IP核设计

3.2.1 IP核寄存器设计

在VIVADO开发平台下自动生成自定义IP核的模板,模板中slv_reg0寄存器对应了IP核的基地址,当FPGA的ARM硬核处理器对IP核的基地址进行写操作时,就将数据写入了slv_reg0寄存器,所以可以将slv_reg0寄存器当作1553B总线编码IP核的控制寄存器。slv_reg0寄存器中的第31位表示命令/状态字(tx_csw),第30位表示数据字(tx_dw),第15位至第0位表示有效数据。IP核slv_reg0寄存器设计如图5所示。

图5 IP核slv_reg0寄存器设计

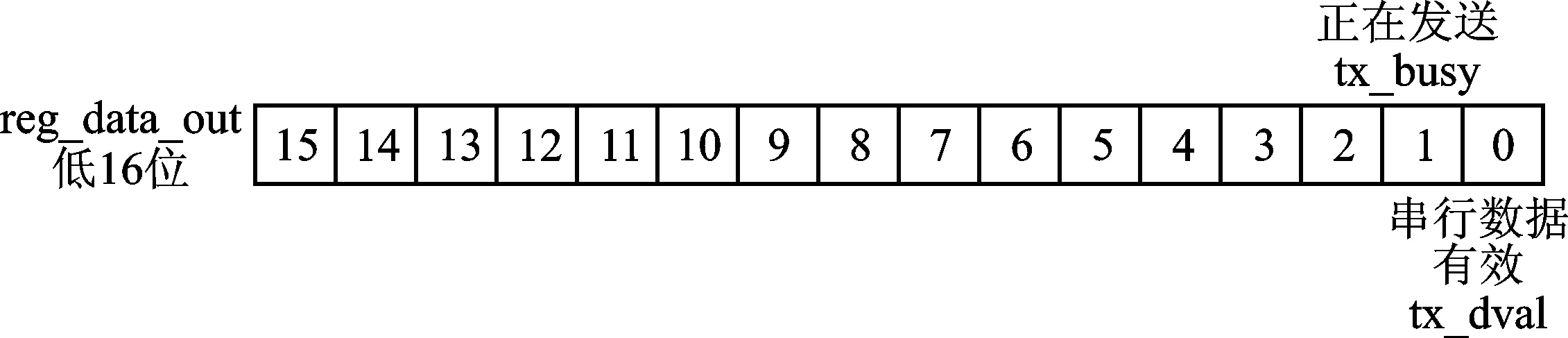

同时,模板中reg_data_out寄存器也对应了IP核的基地址,当FPGA的ARM硬核处理器对IP核的基地址进行读操作时,就将reg_data_out寄存器中的数据读取出来了,所以可以将reg_data_out寄存器当作1553B总线编码IP核的状态寄存器。reg_data_out寄存器中的第0位表示串行数据有效(tx_dval),第1位表示正在发送串行数据(tx_busy)。IP核reg_data_out寄存器设计如图6所示。

图6 IP核reg_data_out寄存器设计

3.2.2 IP核设计仿真验证

硬件系统设计如图7所示。

图中ZYNQ7 Processing System为ARM硬核处理器,TX1553B_v1_0就是自定义的1553B总线编码IP核,它们之间通过专用的AXI4Lite总线连接并分配地址。利用在线逻辑分析仪(ila_0)抓取TX1553B_v1_0的串行输出引脚的波形。设计仿真验证:①发送命令字0x5555,即将0x80005555写入IP核控制寄存器slv_reg0,观察输出波形,如图8所示;②读取IP核状态寄存器reg_data_out,观察IP核的状态,如图9所示。

图7 硬件系统设计

图8 1553B总线编码IP核输出波形

图9 IP核状态寄存器

结 语

[1] 蒋国峰,白红.1553B总线监控器的设计与实现[J].电子设计工程,2011,19(17):98-100.

[2] 李辉,张敬波,张磊.1553B多功能RT IP核的设计与实现[J].航天控制,2012,30(1):59-65.

[3] 单忠伟.1553B总线远程终端的FPGA程序设计[J].现代电子技术,2013,36(9):28-30.

[4] 赵明阳,朱岩,张建东,等.基于PCI局部总线的1553B总线接口卡设计[J].现代电子技术,2012,35(10):47-52.

[5] 郑兴,袁斌.基于FPGA的1553B总线RT终端IP核设计[J].河南理工大学学报:自然科学版,2014,33(6):793-798.

[6] 周莉,安军社,谢彦,等.基于ASIC技术的1553B IP核的设计[J].空间科学学报,2014,34(1):127-136.

[7] 高亚军.基于FPGA的数字信号处理[M].北京:电子工业出版社,2012.

[8] 张谨,史田甜.基于FPGA的1553B协议接口的实现[J].集成电路通信,2011,29(1):15-19.

[9] 熊华刚,王中华.先进航空电子综合技术[M].北京:国防工业出版社,2009.

[10] 李宪强.FPGA项目开发实战讲解[M].北京:电子工业出版社,2015.

张文波(工程师),主要研究方向为嵌入式系统设计。