基于FPGA和ARM的高速数据采集系统设计

2018-01-05刘美枝党婵娟

杨 磊,刘美枝,高 海,党婵娟

(山西大同大学物理与电子科学学院,山西大同037009)

基于FPGA和ARM的高速数据采集系统设计

杨 磊,刘美枝,高 海,党婵娟

(山西大同大学物理与电子科学学院,山西大同037009)

数据采集是完成信号分析、信息处理的必要前提。能够对高速数据精确采集、信号实时处理,在现场测控系统中起到至关重要的作用。文章介绍了采用FPGA控制高精度高采样率的A/D电路对高频信号实时采集,以ARM处理器做为数据远程传输的控制器,通过DM9000实现高速数据网络传输,将数据存储在远程PC端。通过实验测试表明,该高速数据采集远程实时存储系统可以稳定的采集各类高频信号,能够广泛应用于多种现场测控系统,具有极大的应用价值。

FPGA;ARM;高速数据采集

在故障诊断等现场测控系统中,高效采集大量原始数据是提取和分析系统运行过程中各阶段不同信号的必要前提,为后续信号处理提供了重要保证。

目前的数据采集系统种类繁多,一般处理器不能同时满足其高速采集、远程传输存储和实时并行处理。FPGA(Field Programmable Gate Array)是一种大规模现场可编程逻辑门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有编程器件门电路数有限的缺点[1-2]。FPGA在高速数据采集和并行算法处理方面具有单片机和DSP所不具备的优点。FPGA内部有丰富的可编程逻辑单元、大量的硬件乘法器模块、充足的I/O引脚资源,以及多个锁相环(PLL)可以把系统输入时钟倍频到几百兆赫兹,以提供给系统内部时序电路使用。采用FPGA进行高速数据采集存储系统设计,具有开发周期短、集成度高、功耗低、工作频率高(时钟延时为ns级)、可现场反复编程、可靠性高等一系列优点。FPGA和ARM(Advanced RISC Machines)单独都可以完成数据采集工作,但是要想同时满足高速数据的并行采集和同步远程传输存储,必须把FPGA和ARM有效的结合起来,充分发挥FPGA对高速并行数据的处理优势,利用ARM与PC机接口实现数据通过以太网实时远程传输,具有成本低、可靠性高、稳定性强的优点。因此,在高速实时测控领域有着非常广阔的应用前景。

本文设计了基于FPGA+ARM的高速数据采集和远程传输存储系统。FPGA采用模块化的设计方法,利用Verilog HDL硬件语言设计A/D模数转换控制器和16位并行缓存控制器,通过Quartus II和Modelsim对系统的顶层模块及各子模块进行功能仿真和时序仿真,静态时序分析验证系统设计的合理性。首先FPGA控制AD7622实现32MSPS数据并行采集,然后与ARM进行DMA方式的高速数据传输,并在linux内核中移植TCP/IP协议和DM9000网卡的驱动编写,最后在PC机上设计SOCKET网络接口,实现高速数据的实时采集和远程存储。

1 系统整体设计

高速数据的实时并行采集和存储是信号分析处理的前提,保证现场测控系统实时高效运行。系统输入端接入宽带高频信号传感器,利用FPGA实现高速数据采集,ARM处理器实现DMA控制器的高速数据传输,输出端通过TCP/IP网络协议与PC机实现网络接口通信,完成高速数据采集与实时存储[3]。

系统的主要硬件结构包括宽带高频传感器、AD7622数据采集模块、FPGA数据采集主控模块、ARM9(S3C2440A)的DMA控制器模块、DM9000网络传输模块和PC机数据接收的软件模块。系统的基本结构如图1所示。

图1 系统基本结构图

高速数据采集与存储系统实现的基本功能是利用高频宽带传感器检测各类高频信号,经过信号调理电路对采集信号放大、滤波处理。FPGA核心处理器控制AD7622数据采集模块的初始化设置,以32MSPS速率并行采样。在ARM的linux内核版本为2.6.25.8操作系统下,配置数据传输方式为内存直接存取(DMA)方式,以及DMA控制器的传输方式、服务模式和请求方式等;移植TCP/IP协议和编写DM9000网卡驱动实现高速数据实时传输。在PC机端通过SOCKET网络接口实现数据接收。最终将大容量的数据写入PC机硬盘的TXT文件中。

系统硬件接口设计如图2所示。

图2 系统硬件接口图

图2中,高频宽带传感器的输出信号直接传送给A/D数据采集调理电路的信号接收接口,并将两者共地降低干扰。FPGA工作在100Mhz的时钟频率下,控制AD7622的cnvst启动转换引脚(低电平表示启动转换),实时检测busy信号的下降沿(高电平表示AD7622正在转换)。FPGA同时与ARM的系统总线接口通信,在ARM端设计DMA控制器完成高速数据传输,其中FPGA的16位并行数据输出给ARM的数据总线LDATA接口,其它DMA通信用到的信号线包括:DMA外部请求DREQ,DMA外部响应DACK,S3C2440A的存储器BANK3的使能信号nGCS3和读写控制信号nEW、nOE,DMA的数据读写时钟CLKOUT和一次单服务模式DMA开始信号start。通过这些信号控制接口完成FPGA与ARM的DMA方式数据传输通信。最后,ARM与PC机通过有线网络接口实现高速数据实时采集存储。

2 系统软件设计与仿真

FPGA控制高精度高采样率的ADC电路,在高速数据采集的逻辑设计方面具有容量大、处理速度快、集成度高等优点。逻辑单元LE是FPGA的基本单元,也是衡量其容量性能的最重要指标,FPGA通过四输入的查找表(16*1RAM)实现组合逻辑的设计,可现场反复编程[4-5]。为了提高FPGA的运算性能,芯片制造商在其内部集成了专用硬件乘法器等硬核[6]。DMA(Direct Memory Access)技术是一种高速的数据传输方式,允许在外部设备和存储器之间、存储器和存储器之间等直接传输数据。当DMA控制器从数据源(外设和存储器)将数据读到数据总线后,会立刻在同一个DMA周期内把数据直接传送到目标地址单元内,而不需要像CPU那样先接收后转发。FPGA控制的数据采集和ARM端控制的DMA方式数据传输协同工作,高效完成高速数据采集和实时同步传输。

2.1 高速数据采集模块的FPGA设计

本系统的核心处理器选用Altera公司Cyclone IV系列的FPGA芯片EP40E40F23C6,系统最高工作频率为400 Mhz。为了保证不失真的数据采集,设计AD7622为2MSPS*16bit的并行转换模式。FPGA系统时钟是外部50 Mhz晶振时钟经过内部PLL倍频之后得到的100 Mhz,时钟周期为10 ns。这样满足每50个时钟周期(500 ns)完成一次采样数据转换。AD7622的数据采集转换时序如图3所示。

图3 AD7622数据转换时序图

配置AD7622为进行连续读写转换。AD7622的转换过程是:初始化时CNVST信号线为高电平,BUSY信号线为低电平,由FPGA控制CNVST输出4个周期(t1时间)低电平信号作为AD7622的开始转换启动信号,当AD7622内部机制检测到CNVST的低电平时,令BUSY信号由低电平变为高电平,表示正在进行单次数据的并行转换,同时PFGA内部以100 Mhz的时钟频率检测BUSY信号由高变低的下降沿,来判断单次数据转换完成。利用Quartus II和Modelsim对数据采集模块进行时序仿真[7],结果如图4所示。

图4 Modelsim数据采集模块时序仿真图

图4中,clk为100 Mhz的系统时钟;reset为复位信号(低电平有效);32MSPS的采样率下,一个采样周期为50个时钟(500 ns),cnvst前4个时钟周期为低电平;busy在第36个时钟周期出现下降沿,表示一次数据转换完成;lock在每次采样周期结束时为高电平,表示采样完成;d[15:0]表示16位的AD7622输出信号;q[15:0]表示FPGA的读取信号。利用嵌入式逻辑分析仪(SignalTap II Logic Analyzer)对AD7622数据采集卡的测试结果如图5所示。

图5 AD7622数据采集硬件测试结果图

对AD7622数据采集模块进行验证,首先将传感器信号输出到数据采集模块的输入端,并把数据采集模块的十六位数字信号和转换控制信号连接到FPGA的GPIO接口,因为传感器实际输出经过信号调理电路滤波、衰减,最终转换信号的幅值为0.9 V左右,满足AD7622差分输入范围。图5中,经过试验测试采集到的数字信号以二进制补码编码,并以十六进制显示。由于AD7622的基准电压是2.048 V,所以电压值的最小分辨率是62.5 uV。经过换算,十六进制3900H转换成实际模拟电压是0.912 V,符合高速数据采集的设计要求。

2.2 数据传输模块的DMA设计

DMA控制器既是一个具有系统总线控制能力的主控部件,又是一个工作方式必须由CPU进行设置的受控部件。受控部件需要由CPU对它进行工作方式的设置,以确定通道的选择、数据传输模式及类型、内存区域的首地址、地址是递增或递减、传送的总字节数等[8]。主控部件掌握总线,可以产生寻址存储器的地址信号以及进行数据读写的控制信号。DMA方式传输与CPU共享系统总线,对于I/O设备进行快速数据传输,必须采用DMA方式实现。

DMA数据传输的整体结构如图6所示。

图6 DMA数据传输的整体结构

DMAC(DMA控制器)是数据传输的核心电路,HOLD和HLDA用于DMA方式请求和响应。DMA数据传输过程一般分为如下四个阶段:申请阶段、响应阶段、数据传送阶段和传送结束阶段。

S3C2440A处理器拥有4个独立通道的DMA控制器,每个DMA通道都有6个源,DMA的触发方式分为软件触发和硬件触发。本文选用的是DMA通道0,源为nXDREQ0,DMA的操作方式选择为源设备和目的设备都在系统总线上,采用H/W请求模式(硬件请求模式),数据的传输模式设置为单服务传输模式。DMA的硬件请求时序图如图7所示。

图7 DMA的硬件请求时序图

S3C2440A的DMA通道0共有9个控制寄存器,其中6个用于控制DMA传输,3个用于监视DMA控制器的状态。通过在Linux系统中,配置DMA控制寄存器、S3C2440A的存储器、BNAK选择控制寄存器和时钟控制寄存器,继而控制DMA的运行时钟CLKOUT、外部响应XnDACK的延时、BANK选通信号nGCS的建立时间和延迟时间以及读写使能信号nOE的建立时间和延迟时间。基于FPGA和ARM的DMA通信时序图如图8所示。

图8 基于FPGA和ARM9的DMA通信时序图

图8中,HCLK是ARM9提供的用于DMA传输的时钟100Mhz,XnDREQ是FPGA向ARM9发送DMA请求的外部信号,XnDACK是ARM9接收到外部DMA请求后的响应信号,nGCS是S3C2440A存储器BANK3的选通信号,nOE是系统存储单元读信号的使能端,通过以上方式实现DMA的有效传输。

3 系统的具体实现

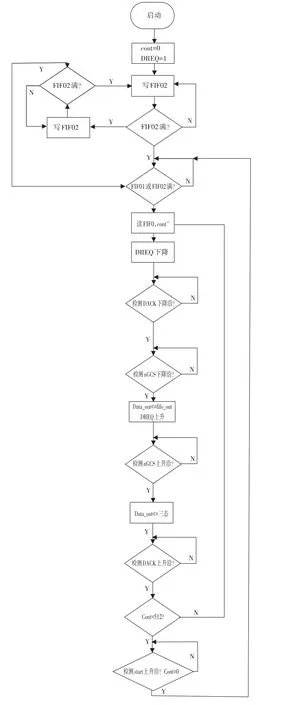

高速数据采集存储子系统利用FPGA和ARM开发平台联合实现,FPGA和ARM采用DMA的方式进行高速数据传输,并在FPGA内部采用双乒乓缓存的异步FIFO解决数据采集和数据传输的同步进行[11]。当系统上电启动时,首先在FPGA内部利用Verilog HDL硬件编程语言初始化各端口的值,令FIFO的计数个数初值count=0,DMA外部硬件请求端DREQ=1,初始化之后开始数据采集,控制AD7622的数据转换,把每次转换完成的16位数字量存在预先定义的16bit*512的FIFO1,直到FIFO1存满了之后开始读,并且令DREQ产生下降沿,计数器计数count++,同时实时采集的数据存到另一个16bit*512的FIFO2,这样保证数据采集能实时连续进行。每当FPGA发生一次DREQ的下降沿请求时,ARM的DMA控制器立即检测到外部请求并申请系统总线,申请成功便产生DACK的下降沿作为DMA的响应信号,FPGA在200 Mhz时钟下检测DACK的下降沿,同时检测nGCS和nOE的低有效信号,只有当ARM端DMA操作内存选通并可以读写时,FPGA才把从FIFO读出的数据放到ARM系统总线的数据总线端口,其他时刻令数据总线端电平为高阻态,保证系统总线读取数据不受污染[9-10]。FPGA内部FIFO的读时钟是由S3C2440经过倍频配置,通过时钟输出引脚CLKOUT提供,时钟频率为100 Mhz。直到ARM的DMA操作完成512次(count=512)之后,把count清零,此时FPGA不断检测ARM发送的下次传送启动信号start的上升沿,当检测到了下一次启动传输信号,便开始下一个512次DMA的数据传送。FPGA和ARM9实现DMA数据传输的流程图如图9所示。

图9 FPGA和ARM9的DMA传输流程图

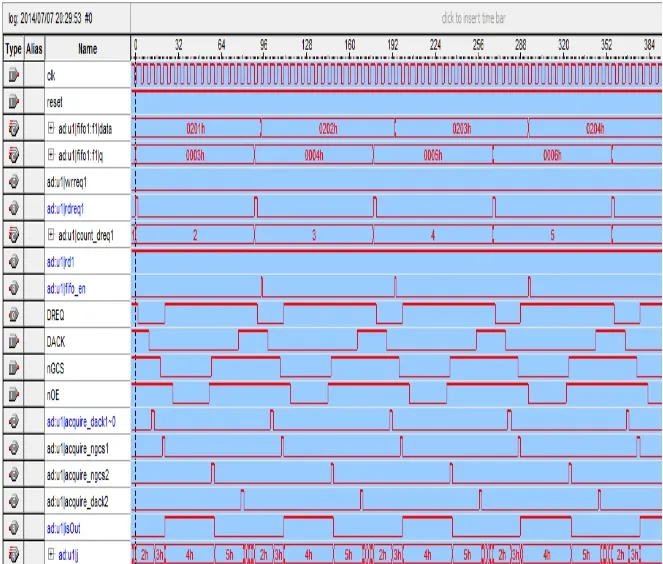

高速数据采集存储子系统设计的关键是FPGA与ARM9的DMA通信。FPGA驱动程序的设计主要包括:AD7622采集卡的驱动程序设计,乒乓缓存FIFO的时序控制,与ARM进行DMA通信的时序控制。ARM系统的重点工作主要包括:Linux系统内部存储器BANK单元的配置,GPIO端口寄存器的配置,DMA相关寄存器的配置,TCP/IP协议的移植,DM9000网卡驱动程序的设计,PC机接收数据是通过SOCKET网络接口实现。FPGA和ARM作为一个整体协同工作,相互配合发挥各自的优势,完成高速数据实时采集,动态传输存储和控制管理等,为后续的软件分析处理提供保障。利用Quartus II内部的SingalTap II Analyzer对系统性能进行分析与验证,系统工作时序图如图10所示。

图10 FPGA与ARM的DMA通信测试时序图

图10中,clk为FPGA工作时钟100 Mhz;reset为复位信号,低电平有效;data为AD7622的输出数据;q为FPGA的采集信号;rereq和wrreq为FIFO的读写信号;count_dreq为DMA传输数据的个数;DREQ、DACK、nGCS、nOE为DMA的传输控制信号;其他信号为FPGA内部沟通信号。由图可知,DMA方式的数据传输满足32MSPS采样率下高速数据的实时传输,达到系统的设计要求。

4 结论

本文分析了FPGA和ARM分别在高速数据采集和处理方面的优缺点,结合整个系统需要实时同步传输数据,最终采用FPGA做为数据采集核心控制器,ARM做为数据DMA方式传输的控制器,通过与PC机的网络接口连接,实现并行采集和实时同步传输。

整个系统的硬件接口的设计思路具有很强的通用性,也可以广泛应用于各种高速低速信号的采集,用户方便修改升级,具有很强的实用性。

[1]邓志阳,曹玉雯,祝海江.一种基于FPGA的超声信号高速采集与压缩方法[J].计量技术,2010(1):27-29.

[2]于宗光,魏敬和,王国章.SoC和FPGA技术未来的发展趋势[J].电子与封装,2006,6(3):1-5.

[3]朱建光,余红英.基于ARM和FPGA的高速数据采集系统[J].伺服控制,2010(3):75-77.

[4]麦晓明,王锐,陈海涵,等.输电线路无人机巡检数据链路通信系统设计[J].广东电力,2014,27(4):76-81.

[5]张晓娟.基于FPGA的实时视频信号处理系统的设计[D].太原:太原理工大学,2012.

[6]郝宇宁.基于DSP的小波分析在声发射信号处理中的应用研究[D].南宁:广西大学,2007.

[7]邬琦,杨江涛,马喜宏.基于FPGA的高速信号采集电路的设计与实现[J].实验室研究与探索,2015,34(4):124-128.

[8]甘利军.装甲车发动机检测与故障诊断设备的研究[D].武汉:武汉理工大学,2009.

[9]张伟,刘爽,王炳义,等.基于ARM的CCD数据远程采集系统设计[J].微计算机信息,2009,25(4):89-90.

[10]王珊.基于ARM9的近程无人机数据采集系统[J].测控遥感与导航定位,2013,43(8):40-43.

[11]施华钧.高效异步FIFO的设计实现[D].长沙:湖南大学,2013.

Design of High-speed Data Acquisition System Based on FPGA and ARM

YANG Lei1,LIU Mei-zhi1,GAO Hai1,DANG Chan-juan1

(School of Physics and Electronic Science,Shanxi Datong University,Datong Shanxi,037009)

Data acquisition is the necessary premise to complete signal analysis and information processing.It can be used for accurate data collection and signal processing of high-speed data,which plays a crucial role in the field measurement and control system.

A/D circuit controlled by FPGA with high precision and sampling rate is used to perform real-time acquisition of high freduency signal,ARM processor as the controller of data remote transmission,high-speed data network transmission are realized by DM9000,store the data in the remote PC.The experimental tests show that the high-speed data acquisition remote real-time storage system can gather all kinds of high frequency signal steadily,can be widely used in a variety of field measurement and control system,has a great application value.

FPGA;ARM;high-speed data acquisition

TH86

A

1674-0874(2017)06-0032-05

2017-05-16

杨磊(1988-),男,山西大同人,硕士,助教,研究方向:网络化测控。

〔责任编辑 高彩云〕