一种应用于MCU待机模式的超低功耗LDO设计*

2018-01-04张超张志鹏刘铁锋

张超,张志鹏,刘铁锋

一种应用于MCU待机模式的超低功耗LDO设计*

张超,张志鹏,刘铁锋

(中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016)

设计了一种应用于MCU待机模式的超低功耗低压差线性稳压电路(LDO)。采用较少的MOS管以及简单的结构,只需提供一个15nA的偏置电流,可自产生偏置电压,无需带隙基准(Bandgap reference)电路提供基准电压。针对与主LDO协同工作的情况设计了输出级,能有效避免LDO同时工作引起的电源电压波动。在MCU的待机模式下,可以给上电复位(POR)、唤醒电路(Wakeup)、低功耗振荡器(LPOSC)、数据保持(Data retention)电路提供电源电压。该电路采用TSMC 0.18μm标准CMOS工艺。经过Synopsys Hspice仿真验证,输入电压为3.3V,输出电压为1.78V,在-25~125℃温度范围内温漂系数为30ppm/℃。整个LDO电路的整体的静态电流只有60nA,版图尺寸为25μm×38μm。

微控制器;LDO电路;低功耗;待机模式;输出级;上电复位

1 引言

作为电子设备控制核心的微控制器(Microcontroller Unit,MCU)产品,在物联网时代迎来了更广阔的商机。与此同时,物联网应用的新特性也为MCU的发展带来了诸多挑战。为了实现IoT成功,MCU必需具有尽可能高的能效,从而使这些IoT设备可以更长久地工作,具有更多的功能性,或者更小的外形尺寸。无论智能功能是通过使用SoC器件或分立式MCU器件嵌入在设备中,低功耗都至关重要。

为了降低功耗,MCU一般采用多种运行模式,包括工作模式、待机模式等,其中待机模式的功耗直接影响了MCU的使用范围以及供电电源的使用寿命。为此,设计一种给MCU待机模式下提供内部电源的低功耗LDO,采用较少的MOS管以及简单的结构来实现[1]。

2 LDO的低功耗设计

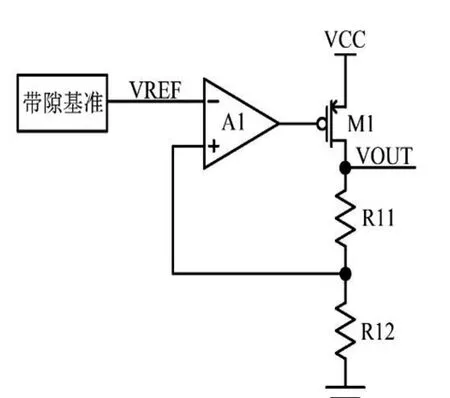

传统的低功耗LDO电路[2-7]由带隙参考电路、差分放大器和电阻分压网络等部分组成,其结构如图1所示。

图1 传统LDO电路结构

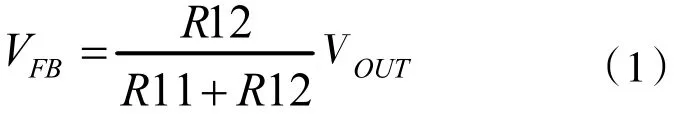

LDO电路根据带隙基准产生的参考电压VREF产生输出电压VOUT,输出电压VOUT经过反馈电阻R11和R12分压之后为差分放大器A1的同向输入端提供反馈电压VFB,上述反馈电压VFB的表达式为:

差分放大器A1将参考电压VREF和反馈电压VFB进行比较得到差值ΔV并将差值ΔV放大后得到Vdrive,Vdrive用于驱动功率输出PMOS晶体管M1的栅极,从而改变通过功率输出PMOS晶体管M1的电流,使得反馈电压VFB与参考电压VREF近似相等,最终使得输出电压VOUT的电压值趋于恒定,如下式所示:

在传统LDO电路结构中,带隙参考电路和差分放大器均需要消耗功耗,因此在降低传统结构的LDO电路功耗时,存在着限制。

芯片工作在待机状态时所需要的电流会很小,通常不到1μA,如果在这种情况下采用传统LDO电路为其供电,可能会出现LDO电路本身消耗的静态电流大于芯片本身消耗电流的情况,即使采用文献[8]所设计的低功耗带隙基准电路,也不能很好满足需求。

另外对传统的LDO电路结构还需要进行补偿以保证环路的稳定性,这就使得电路的设计复杂度增加了。

为此设计一种低功耗LDO,不需要额外的带隙基准电路,只需一个15nA的偏置电流,便可在MCU的待机模式下,给上电复位(POR)、唤醒电路、低功耗振荡器等提供偏置电流。LDO整体电路的静态电流只有60nA。

3 低功耗LDO电路组成及设计

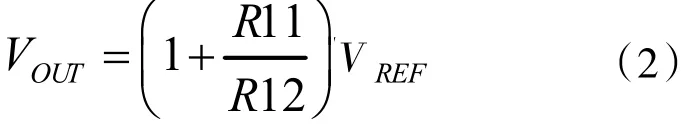

低功耗LDO原理图如图2所示。LDO的基准电压由电流源IREF和两个二极管D1、D2决定。误差放大器A1将VREF与VOUT的误差放大,通过控制调整管PM1的电流使得VOUT等于VREF。

图2 低功耗LDO电路原理

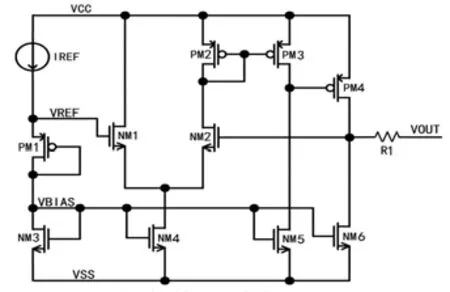

低功耗LDO实际电路图如图3所示,由基准电压源、误差放大器、输出级三部分组成。

图3 低功耗LDO电路

基准电压源由PM1、NM3组成,整个电路只需要15nA的电流源IREF流过PM1和NM3,产生一个基准电压VREF和电流偏置电压VBIAS,其中PM1和NM3由二极管连接。产生的VREF电压可由下式表示:

NM1和NM2组成误差放大器的差分输入对管,输出差分放大信号到PM2和PM3组成的电流镜,通过电流镜以及尾电流源NM5,输出误差放大信号给由PM4、NM6和R1组成的输出级,其中PM4为LDO的调整管,NM6为尾电流源,R1为输出电阻。最终输出LDO输出电压VOUT并反馈给误差放大级。

忽略误差放大级的输入失调电压,并假设误差放大级和输出级的增益足够大,可以得到:

VOUT=VREF (4)

低功耗LDO与主LDO的输出同时连接在一个输出电容CL上,如图4所示。低功耗LDO在MCU芯片中属于常开电路(Alwayson block)。如何避免低功耗LDO与主LDO切换时产生电压波动也是需要关注的问题。为此,低功耗LDO的输出电压VOUT设计应低于主LDO的输出电压,并在输出级设计了一个尾电流源,保证整个低功耗LDO在正常工作模式下也处于工作状态,避免切换LDO时产生启动延时或启动过冲。低功耗LDO的功耗较低,为了满足一定的速度响应要求,调整管PM9的尺寸设计也应较小,使输出电流较小。输出电阻R2作为限流电阻,能有效避免LDO切换时PM9瞬时电流过大的发生。

图4 多LDO协同工作连接示意图

4 仿真结果

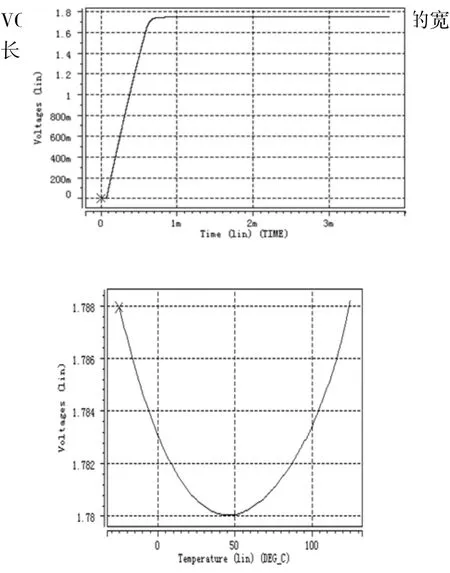

采用台积电TSMC 0.18μm标准CMOS工艺,输出电压VOUT瞬态仿真结果如5图所示,可见启动时间约为700μs,启动时间较长是由较大的输出电容引起的。实际芯片在工作中,电容的充电主要是由主LDO完成的,温度曲线如图6所示。此处采用的电流源属于PTAT电流源,而产生基准电压的

图6 低功耗LDO输出电压与温度关系图

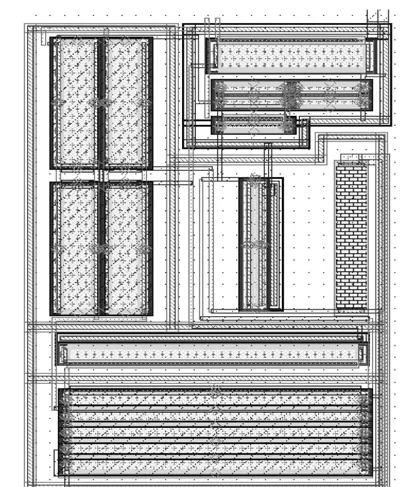

5 版图及流片

采用TSMC 0.18μm CMOS工艺制作低功耗LDO版图如图7所示,整个低功耗LDO电路的版图尺寸为 25μm×38μm,面积为 950 μm2。

图7 低功耗LDO版图设计

6 结束语

设计了一种应用于MCU待机模式下的低功耗LDO电路,无需带隙基准电路,只需提供一个15μA电流源,就可自产生偏置电压,提供电源电压为待机模式下的工作电路供电。整个低功耗LDO的静态电流只有60nA。针对与其它LDO协同工作的情况设计了输出级,能有效避免LDO同时工作引起的电源电压波动。整个LDO所占版图面积为25μm×38μm。在输入电压为3.3V时,可实现输出电压为1.75V,能应用在多工作模式的MCU芯片中。

[1] G.A.Rincon-Mora and P.E.Allen.A Low-Voltage,Low Quiescent Current,Low Dropout Regulator[J].IEEEJournal of Solid-State Circuits,1998,33:36-44.

[2] M.Ho and K.N.Leung.Dynamic bias-current boosting technique for ultra low-power low-dropout regulator in biomedical applications[J].IEEE Trans.Circuits Syst.II,Exp.Briefs,2011,58(3):174-178.

[3]M.Amayreh,J.Leicht and Y.Manoli.A 200ns Settling Time Fully Integrated Low Power LDORegulator With Comparatorsas Transient Enhancement[J].International Symposium on Circuitsand Systems,2016:494-497.

[4] 王忆,何乐年,严晓浪.温度补偿的30nACMOS电流源及在LDO中的应用[J].半导体学报,2006,27(9):1657-1662.Wang Yi,He Lenian,Yan Xiaolang.ATemperature Compensation 30nA CMOS Current Source and Its Application in LDO[J].Journal of Semiconductors,2006,27(9):1657-1662.

[5] Man,T.Y.,and Mok,P.K.T..A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement[J].IEEE Trans.Circuits Syst.II,2007,9:755-759.

[6] C.Chen,J.Wu,and Z.Wang.150 mA LDO with selfadjusting frequency compensation scheme[J].Electron.Lett.,2011,47(13),767-768.

[7]P.C.Crepaldi,T.C.Pimenta,R.L.Moreno,etal.ALow Power CMOSVoltage Regulator for a Wireless Blood Pressure Biosensor[J].IEEE Trans.Instrum.Meas.,2012,61(3):729-739.

[8] 杨学硕,陆铁军,宗宇.一种用于低功耗LDO的CMOS电压基准设计[J].电子设计工程,2015,23(22):98-100.Yang Xueshuo,Lu Tiejun,Zong Yu.A Design of CMOS Voltage Reference for Low Power LDO[J].Electronic Design Engineering,2015,23(22):98-100.

An Ultra Low-Power LDO for MCU in Standby Mode

An ultra low-power Low-Dropout(LDO)voltage regulator for MCU in standby mode is designed.The LDO generates the reference voltage using fewer transistors and simple structure with a 15nA current reference.The output stage is optimized for working in coordination with main LDO.The LDO provides the power supply for POR,wakeup circuit,low-power oscillator and data retention while MCU works in standby mode.The circuit is simulated in TSMC 0.18μm standard CMOSprocess.By simulation with Hspice,the circuit achieves an output voltage of 1.78V with input voltage of 3.3V.The temperature coefficient is 30 ppm/℃ in temperature range from-25℃ to 125℃.It only consumes a quiescent current of 60nA.The layout of ultra low-power LDO circuit occupies 25μm×38μm.

Microcontroller unit;LDO;Low-power;Standby mode;Output stage;Power-on reset

10.3969/j.issn.1002-2279.2017.06.008

B

1002-2279-(2017)06-0033-04

国家科技重大专项 新一代宽带无线移动通信网重大专项资助(03专项),高实时WIA-PA网络片上系统(SoC)研发与示范应用(编号:2015ZX03003010)

张超(1980—),男,四川省自贡市人,副研究员,硕士,主研方向:模拟集成电路设计。

2017-12-12