基于EPLD设计的基站中频系统

2017-12-21秦文丽

秦文丽

摘要:本文设计了一种基于EPLD器件的基站中频系统,该系统采用了ALTERA公司的MAXII系列中的EPM1270芯片。首先简单介绍了EPLD的接口特点,随后对该设计系统的硬件和软件两方面都做了详细论述。硬件部分给出了系统的总体设计方案,软件部分主要由固件设计、驱动程序设计和应用程序设计三部分组成。

关键词:EPLD;MPC875;WD2;复位;告警

中图分类号:TP391.4 文献标识码:A 文章编号:1007-9416(2017)10-0146-03

1 概述

随着电子行业的发展,大规模集成电路的运用越来越普遍,用EPLD( Erasable Programmable Logic Device)开发新产品是当前很多实际情况的需求。本文详细描述了EPLD在基站上中频板卡上所实现的功能及接口信号。

2 硬件设计

2.1 系统方案

基站上面有一块IFU板(中频板),负责发射信号。中频板上有一片EPLD可擦除可编辑逻辑器件,称为IFRCE(IFU Reset,Control/Configuration,ioExpander),采用EPM1270芯片实现,属于ALTERA公司的MAXII系列。

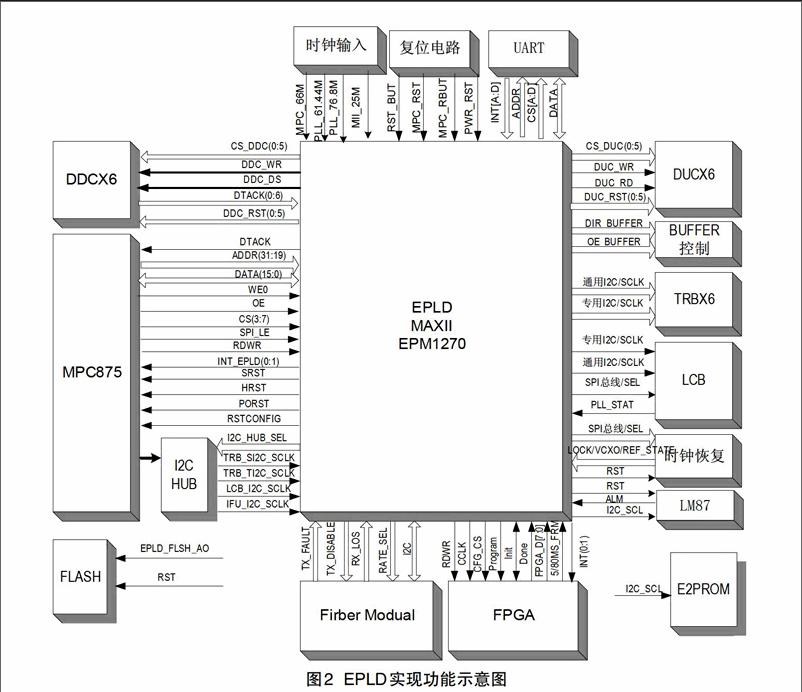

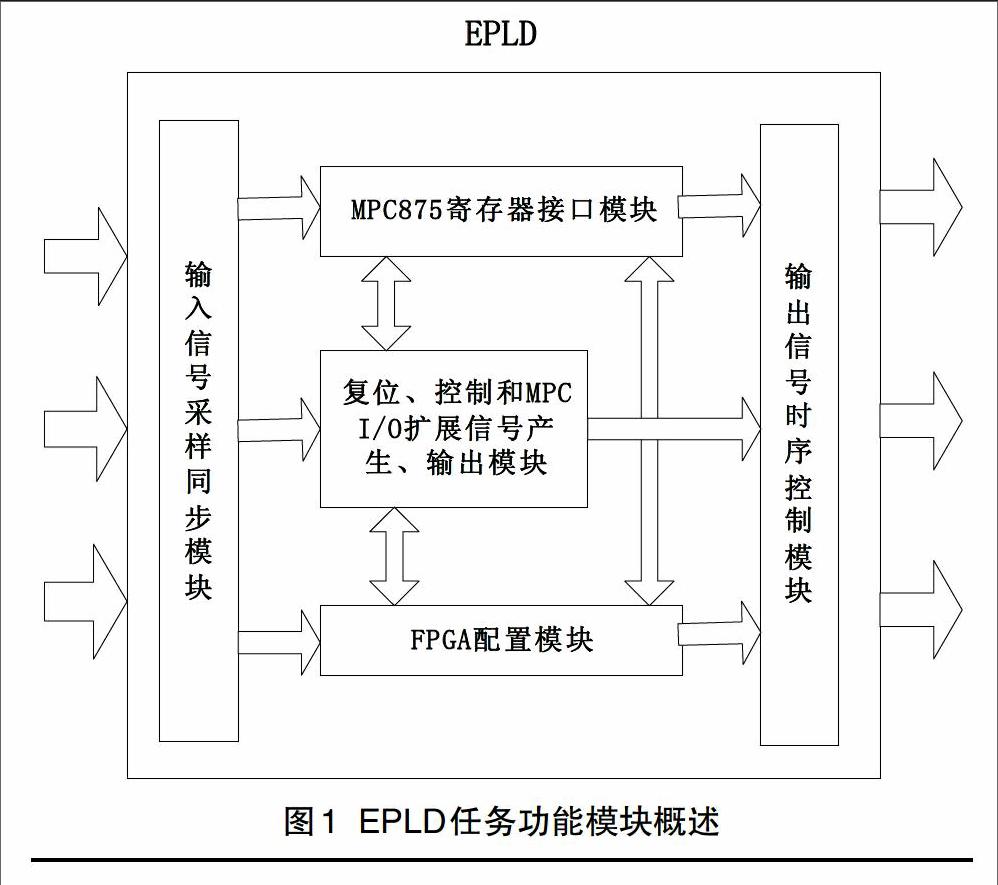

IFRCE主要实现IFU板的复位控制、FPGA(Field-Programmable Gate Array)上电配置、MPC875寄存器接口管理和MPC875的I/O扩展,同时对外部输入信号还有进行去毛刺和同步采样处理,对输出信号进行时序控制使其满足硬件时序要求。其主要任务是实现对如图1、图2所示的各功能模块。

2.1.1 芯片物理特性描述

MAXII器件提供基于行和列的结构来实现用户逻辑。每个逻辑阵列块(LABs)包含10个逻辑单元(LE);内部互连的MultiTrack为LAB提供小颗粒的时间延迟;I/O管脚由位于器件外围的IO单元(IOE)驱动。时钟网络包括四根时钟线,它贯穿整个器件,为器件上的各种资源提供时钟。

MAXII 器件还包含一个FLASH存储体,一部分是用来存储SRAM配置信息的CFM块,另一部分是用户FLASH存储块(UFM)。

2.1.2 管脚分配

每片EPLD分为四个I/O Bank,均采用3.3V供电,接口标准为TTL3.3。

EPLD 的管脚分配,合计:197个信号 (197/212=93%)

2.2 实现功能描述

EPLD主要完成的功能包括:MPC875存储器接口;IFU板的复位控制与管理;硬件复位配置字(HRCW)的读取;双地址BOOT机制;IFU板光模块、温度检测模块、时钟模块、LCB板频率合成模块告警检测;FPGA、DDC、DUC、UART配置接口控制逻辑;LED灯的控制。

EPLD内部功能多用组合逻辑实现。告警检测、输入信号采样和输出信号的时序控制采用时序逻辑。

3 软件设计

3.1 MPC875存储器接口模块

MPC875与EPLD的硬件接口框图如图3所示。

3.2 IFU复位控制与管理模块

IFU复位类型按级别可分为:整板复位(包括处理器和周边器件)、处理器复位(MPC875)和周边器件复位(包括FPGA、6×DDC、6×DUC、UART、2×CDC7005、PHY芯片、LM87、FLASH)。

3.2.1 复位事件归纳

(1)发起整板复位的情况归纳如下:IFU板上电时,由MAX811板产生一个上升沿整板复位脉冲到EPLD;全局复位按钮产生一个下降沿脉冲到EPLD;EPLD内部复位命令字控制寄存器全局复位控制位被置为有效。

(2)发起MPC875复位的情况归纳如下:MPC875复位按钮产生一个下降沿脉冲到EPLD,发起MPC875 PORST复位;EPLD内部复位命令字控制寄存器PORST/HRST/SRST被置为有效;EPLD内部复位命令字控制寄存器SW_REBOOT被置为有效。

3.2.2 复位标志位的管理

当由某种复位源引起的复位发生时,该寄存器中的相应位就会置“1”。这样,在发生异常事件时,可以通过查询该寄存器得知是因为什么事件引起的复位。在复位标志寄存器中设置了八个标志位:MPC875复位按钮复位标志,上电复位标志,外部看门狗复位标志,全局按钮复位标志,远程复位标志,命令字复位标志,软件重起标志,FPGA按钮复位标志。每一种复位事件在置位相应标志位的同时,会清除所有其他标志位。软件对该寄存器的任何写操作都会导致该寄存器清0。这样为软件提供一种清除该寄存器的途径。

3.3 WD2的實现和控制

利用EPLD的可编程特性,在内部实现一个外部Watch Dog 2,这样定时可以比较长,还可以随时关闭。

为了系统调试的方便,操作系统在进程切换的时候,会调用专门的函数,在一个history memory中记录当前调用的进程,如果系统出现异常或死掉,在异常处理子函数或Watch Dog处理子函数中会把history memory的内容写入寄存器中保存,系统再启动之后,通过这个history memory就可以得知最近执行过哪些进程。

Watch Dog 2在定时溢出的时候需要通知MPC875,可以采用产生PORESET或者是NMI中断,采用中断的方式是为了避免程序死在高优先级中断处理子函数里,在每个中断处理子函数内部开始屏蔽其它中断的地方,都不能屏蔽Watch Dog 2中断,这样Watch Dog 2中断就可以打断任何中断处理子函数的执行。IFRCE中对复位的两种方式都支持,软件可以通过寄存器中的WD2 _RST2INT _CTRL位来选择WD2产生PORESET复位还是产生NMI中断。默认WD2产生PORESET复位。endprint

Watch Dog 2的使能由软件控制。软件是通过对寄存器的WD2_EN位置位使能WD2,默认WD2不使能。而且可以通过读取WD2_EN来确认WD2是否使能。

Watch Dog 2的喂狗(即Watch Dog 2计数器清零)的方式有两种:通过置寄存器相应位来清零;每次板级复位或MPC875复位事件发生后,也会对Watch Dog 2计数器清零。

3.4 双地址BOOT机制

系统设计了采用双地址BOOT的机制,框图如图4、图5所示。

BOOT FLASH采用SPANSION的S29GL128N。该FLASH为16位位宽,地址空间8M,23根地址线,或表示为16Mbyte。

对应双地址BOOT方式,有两个BOOT程序:BOOTROOM和BOOST,它们存放在FLASH的不同地址空间内。板卡正常工作时,从BOOTROOM正常启动。当需要进行单板测试或BOOTROOM被损坏的情况下,可以通过图4加跳线跳通,来选择从BOOST启动。这样单板可以正常连接进行相应BOOTROOM文件下载。

FLASH地址空间分配如图5所示。正常情况下从BOOTROOM启动,启动地址为0Xfff00000,当从BOOST启动时,启动地址为0Xffb0000,差别在第23位不同。因此EPLD只要对这一位进行处理就能实现启动地址的转换。MPC875有32根地址线,A(0)为最高位,A(30)为最低位,按8位位宽寻址。由于FLASH是按位宽16位寻址,有23根地址线,因此MPC875连接到FLASH的地址线的最低位应为A(30),最高位为A(8)。当正常从BOOTROOM启动时,JP0为断开,这时A(9)从EPLD作串通;当从BOOST启动时,JP0为跳接状态,这时A(9)被EPLD屏蔽,输出置为0,从而实现了启动地址的变换。

板卡启动情况总结如下:

(1)板卡正常运行的情况:

图4中JP0跳线不加,从BOOTROOM正常启动。

(2)正常测试使用或只有BSP损坏的情况:

图4中JP0跳线加上,从BOOST启动,进行全面测试。

3.5 告警检测

EPLD进行告警检测的芯片包括:IFU板光模块、温度检测芯片、时钟芯片和LCB板的频综模块。EPLD对这些芯片的告警信号采用周期性的检测策略,复用MPC_INT1_EPLD将告警上报MPC875。在ALM_LOS_FM1和ALM_LOS_FM2产生时,EPLD分别将MPC_INT1_EPLD和MPC_INT0_EPLD置為”01”和”10”,通知FPGA。

检测流程如图6所示。

4 结语

本文结合实际应用,提出了一种基于中频板的EPLD可编程器件设计系统,并给出了整个系统的软、硬件设计方法。在EPLD中没有专门的测试模块,对EPLD所完成的功能需要在中频板测试中验证。由于EPLD具有其他总线不可比拟的优点,越来越多的数据采集系统采用EPLD芯片,相信EPLD将成为逻辑控制的主要接口。

参考文献

[1]秦宏,尹常永,李川.用VHDL语言的CPLD器件设计[J].黄金学报,2001(1):49-51.endprint