基于65 nm CMOS工艺的D波段功率放大器设计

2017-12-18高向红孙玲玲苏国东

高向红,孙玲玲,苏国东

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

基于65 nm CMOS工艺的D波段功率放大器设计

高向红,孙玲玲,苏国东

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

基于65 nm CMOS工艺,研究和设计了一款四级全差分结构的D波段功率放大器芯片.采用交叉耦合电容中和技术抵消了硅基CMOS晶体管栅漏寄生电容,提高了放大器的增益和稳定性.通过优化输入输出巴伦和级间变压器,功率放大器的增益和输出功率得到了显著改善.仿真结果显示,在1.2 V的电源电压下,工作在140 GHz的功率放大器的功率增益为16.7 dB,饱和输出功率为11.3 dBm,输出1 dB压缩点为7.0 dBm,功耗为130 mW.芯片面积为500 μm×455 μm.

D波段;CMOS;功率放大器;中和;变压器

0 引 言

随着CMOS工艺的快速发展,晶体管的特征频率不断提高,使得CMOS器件工作于毫米波频段成为可能.毫米波具有带宽宽、安全度高以及抗干扰能力强等特点,因此,在无线通信中被广泛研究.同30 GHz以下的频率相比,毫米波具有更加丰富的频谱资源以及更高的传输速率,成为学术界和工业界的研究热点.特别是在140 GHz附近,毫米波的传播衰减具有极小值,引起了更多的关注.

功率放大器是相控阵雷达、高速通信系统以及汽车传感器等应用中一个重要的模块.由于在毫米波波段,硅基CMOS工艺衬底损耗高、寄生效应严重以及晶体管的供电电压低,实现高输出功率和功率增益的功率放大器面临较大的挑战.目前工作在D波段的功率放大器已有报道.2009年,S. Munkyo等[1]通过采用dummy预填充的微带线结构设计了一款1.1 V,150 GHz功率放大器,实现了8 dB的增益和6 dBm的饱和输出功率.2011年,Xu Z. W.等[2]通过采用cascode管的体端接高电压的共源共栅结构设计了一款三级全差分的128 GHz~157 GHz CMOS放大器,实现了20 dB的增益.2012年,Z. M. Tsai等[3]通过采用一种新颖的阻抗变换网络,设计了一款1.2 V的宽带D波段功率放大器,实现了13.2 dBm的输出功率.2013年,Li C. L.等[4]通过采用由3个电感组成的T型阻抗匹配网络设计了一款147 GHz的全差分放大器,实现了7.1 dB的功率增益.然而,同时实现高增益和高输出功率的功率放大器还未报道.为此,本文设计了一款基于65 nm CMOS工艺的D波段功率放大器电路.

1 功率放大器的分析和设计

1.1 毫米波功率放大器设计的考虑

窄带功率放大器可以等效为输入阻抗变换网络、有源器件和输出阻抗变换网络的级联,其等效电路如图1所示.有源器件的输出阻抗用Ro和Co的并联表示.假定输入和输出阻抗变换网络是无耗的.根据能量守恒定律,功率放大器的最大电压增益可以表示为:

(1)

根据式(1)可以得到功率放大器设计的一些指导原则.首先,有源器件的输出电阻Ro应该足够大,共源共栅结构是可供选择的拓扑之一;其次,晶体管的偏置、尺寸以及版图等必须仔细考虑以使特征频率fT最大化;最后,阻抗变换网络的损耗应最小.

在毫米波频段,无源器件的欧姆损耗以及衬底损耗严重恶化了阻抗变换网络的插入损耗,进而影响了功率放大器的增益.因此,最厚的顶层金属常被设计成高Q值无源器件.同时,衬底屏蔽技术用来防止电磁场向衬底传播并以此减少衬底损耗.变压器具有插入损耗小、尺寸小等特点,常用来执行多种功能,包括阻抗匹配、单端和差分之间的转换、级间交流耦合以及直流偏置等.

1.2 电容中和技术

随着CMOS工艺特征尺寸的不断减小,工作在100 GHz以上甚至太赫兹的硅基集成电路成为可能.然而,晶体管栅极和漏极之间寄生电容引起的反馈严重降低了晶体管的增益,降低了输出和输入之间的隔离度,并造成潜在的不稳定.电容中和技术常被用来改善晶体管的性能[5],如图2(a)所示.交叉耦合电容Cc可以抵消栅漏之间的寄生电容.

图2 电容中和技术差分对的小信号等效电路以及稳定系数和最大增益曲线

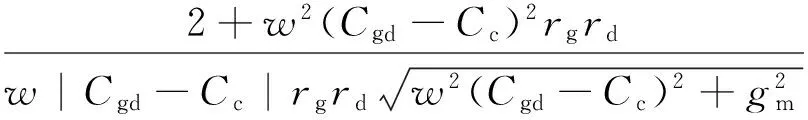

差分对的稳定系数可以表示为:

(2)

最大稳定增益可以表示为:

(3)

其中,gm,Cgs和Cgd是有源器件的小信号参数,Cc是交叉耦合电容,rg是栅极电阻,rd是漏极电阻,Vi是输入电压,Vdd是电源电压.根据式(2)和式(3),可以看出,当Cc等于Cgd时,稳定系数和最大稳定增益可以显著提高.

从图2(b)可以看出,在频率在140 GHz处,由于中和电容的作用,稳定系数和最大增益分别增加了1.8 dB和4 dB.

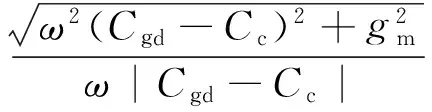

尺寸为60 μm/60 nm的晶体管组成的差分对的稳定系数和最大增益随中和电容的变化曲线如图3(a)所示.可以看出Cgd的过补偿将造成稳定性的降低,这是因为Cc造成的正反馈导致稳定系数下降到1以下.Cc的值选为14 fF,这样可以得到最好的稳定性.

从图3(b)可以看出,频率在140 GHz处,中和电容使得隔离度提高了22 dB.

图3 电容中和技术对差分对稳定系数、最大增益和隔离度的影响

1.3 功率放大器的设计

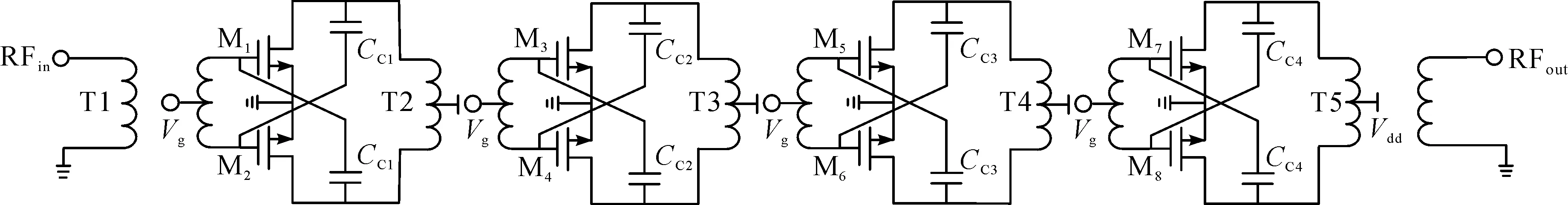

四级全差分功率放大器的拓扑结构如图4所示.

图4 四级全差分功率放大器原理

功率放大器每一级均为差分共源结构,且采用了电容交叉中和技术以提高其增益,稳定性及反向隔离度[6].中和电容选为14 fF以使稳定系数最大.晶体管偏置在最优电流密度0.3 mA/μm以最大化fT.栅极和漏极偏置电压通过变压器的中心抽头供电,其中,栅极偏置电压Vg为0.8 V,漏极偏置电压Vdd为1.2 V.NMOS晶体管的尺寸需要在最大稳定增益和最大输出功率之间折中.为了提高版图的对称性并保证流片成功率,共源放大器的尺寸均为60 μm/60 nm.最顶层的两层厚金属用来形成变压器以减小损耗,衬底屏蔽技术用来减小差模衬底损耗.变压器T1和T4的内径为25 μm,线宽为5 μm.变压器T2和T3的内径为20 μm,线宽为5 μm.

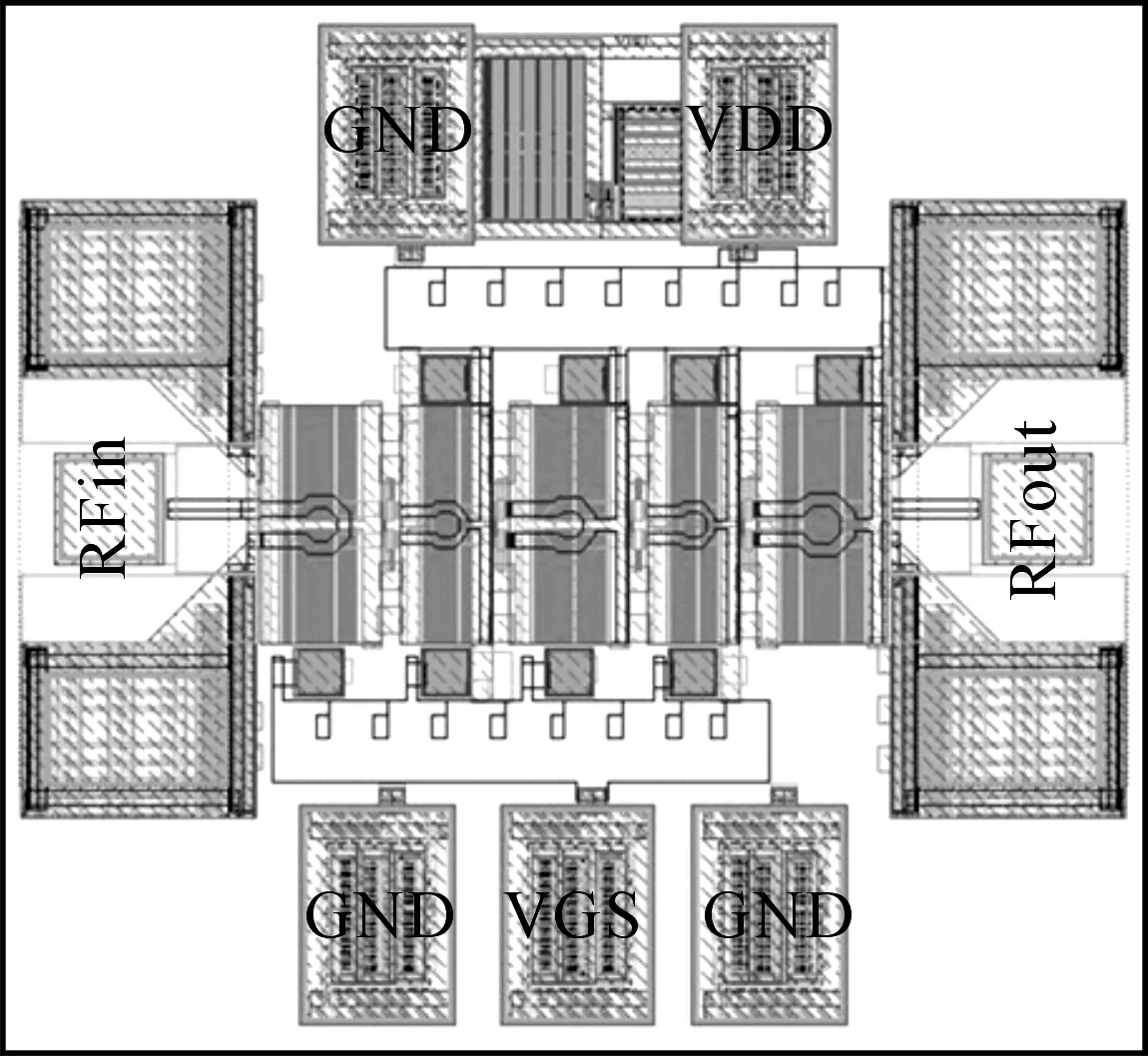

图5 功率放大器版图

2 仿真结果

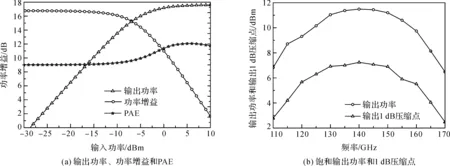

功率放大器的版图如图5所示,版图面积为500 μm×455 μm.版图中的无源器件均通过ADS Momentum的电磁场仿真.功率放大器的后仿结果如图6和图7所示,该功率放大器全频段稳定,频率在140 GHz处,功率放大器的小信号增益为16.7 dB,3 dB带宽为17 GHz(136 GHz~153 GHz),饱和输出功率为11.3 dBm,输出1 dB压缩点为7.0 dBm,PAE最大为4%.

图6 功率放大器的小信号性能曲线

图7 功率放大器的大信号性能曲线

3 结束语

本文针对100 GHz以上高速无线通信和成像系统,设计了一款应用于D波段的功率放大器芯片.提出了一种窄带功率放大器的等效模型,采用的电容中和技术有效地解决了CMOS晶体管高频增益低和不稳定等问题,并利用变压器结构来减小无源器件的插入损耗,同时实现了较高的功率增益和输出功率.本文设计的功率放大器芯片已进入流片阶段,有待进一步验证其实际效果.

[1] Seo M, Jagannathan B, Carta C, et al. A 1.1 V 150GHz amplifier with 8dB gain and+ 6dBm saturated output power in standard digital 65nm CMOS using dummy-prefilled microstrip lines[C]//Solid-State Circuits Conference-Digest of Technical Papers, 2009. ISSCC 2009. IEEE International. IEEE,2009:484-485.

[2] Xu Z, Gu Q J, Chang M C F. A three stage, fully differential 128-157 GHz CMOS amplifier with wide band matching[J]. IEEE Microwave and Wireless Components Letters,2011,21(10):550-552.

[3] Tsai Z M, Liao H C, Hsiao Y H, et al. A 1.2 V broadband D-band power amplifier with 13.2-dBm output power in standard RF 65-nm CMOS[C]//Microwave Symposium Digest (MTT), 2012 IEEE MTT-S International. IEEE,2012:1-3.

[4] Li C H, Lai C W, Kuo C N. A 147 GHz fully differential D-band amplifier design in 65 nm CMOS[C]//Microwave Conference Proceedings (APMC), 2013 Asia-Pacific. IEEE,2013:691-693.

[5] 邸士伟,王硕,张健,等.基于中和电容的60 GHz CMOS功率放大器设计[J].电子器件,2015,38(6):1253-1256.

[6] Ye W, Ma K, Yeo K S, et al. A 65 nm CMOS Power Amplifier With Peak PAE above 18.9% From 57 to 66 GHz Using Synthesized Transformer-Based Matching Network[J]. Circuits and Systems I: Regular Papers, IEEE Transactions on,2015,62(10):2533-2543.

DesignofD-band65nmCMOSPowerAmplifier

GAO Xianghong, SUN Lingling, SU Guodong

(KeyLaboratoryofRFCircuitandSystem,MinistryofEducation,HangzhouDianziUniversity,HangzhouZhejiang310018,China)

This paper presents a four-stage fully differential D-band power amplifier in 65 nm CMOS technology. Cross-coupled capacitors are adopted to neutralize the gate-drain parasitic capacitance of silicon-based CMOS transistor, which improves the gain and stability of the amplifier. By optimizing the Balun and inter-stage transformers, this power amplifier achieves a better power gain and output power. The post-layout simulation results show that the power amplifier achieves a power gain of 16.7 dB, saturated output power of 11.3 dBm, 1 dB compression point of 7.0 dBm and power consumption of 130 mW at 140 GHz from a power supply of 1.2 V. The power amplifier occupies a chip area of 500 μm×455 μm.

D-band; CMOS; power amplifier; neutralization; transformer

10.13954/j.cnki.hdu.2017.06.002

2016-12-22

国家自然科学基金资助项目(61331006);浙江省自然科学基金资助项目(LY16F040004)

高向红(1991-),男,河南洛阳人,射频/毫米波集成电路设计.通信作者:孙玲玲教授,E-mail:sunll@hdu.edu.cn.

TN402

A

1001-9146(2017)06-0005-04