基于无线收发信机的高频锁相环电路设计

2017-12-06高彦曹文田刘宗武

高彦,曹文田,刘宗武

(78156部队,甘肃兰州,730020)

基于无线收发信机的高频锁相环电路设计

高彦,曹文田,刘宗武

(78156部队,甘肃兰州,730020)

在无线收发信机电路中,除了发射机和接收机外,还有一个非常重要的部分就是本地振荡电路。为了保证本地振荡模块输出信号的频率稳定性和较低的相位噪声,通常本振采用锁相环技术来实现,特别在无线通信领域。本文阐述了锁相环的基本结构和工作原理。

锁相环;鉴相器;环路滤波器;压控振荡器

0 引言

锁相技术是一种相位负反馈技术,锁相环电路具有极其优良的性能,它的主要特点是:锁定时无剩余偏差、具有良好的窄带载波跟踪性能、具有良好的宽带调制跟踪性能、门限性能好等,因此锁相环电路在电子系统中得到了广泛的应用[1],特别是无线通信领域。通常在设计收发信机时,对于比较低的频率信号,很容易用晶体振荡器实现,但对于类似410MHz的高频信号,用晶体振荡器不易实现,所以我们采用锁相环(PLL)频率合成的方法来产生。本文从锁相环的原理开始分析,给出了高频锁相环的设计思路和电路实现方法,并通过仿真实验进行了结果验证。

1 锁相环结构组成

锁相环的基本组成包括三个基本的部件,鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)。

(1)鉴相器。鉴相器是相位比较装置,所以有时也叫做相位比较器或相敏检波器。它把输出信号u2(t)和参考信号u1(t)相位进行比较,产生对应于两个信号相位差e的误差电压ud(t)。

(2)环路滤波器。环路滤波器的作用是滤除误差电压ud(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。

(3)压控振荡器。压控振荡器受控制电压uc(t)的控制,使压控振荡器的频率向参考信号的频率接近,也就是使差拍频率越来越低,直到消除频率差而锁定[2]。锁相环总是能使输出依赖跟踪输入信号相位的,环路总是锁定的。但是,当一个较大的频率阶跃加到输入信号是可能会引起环路失锁。当然,锁相环本身的控制机构会努力去再次锁定。这就引出锁相环得一个非常重要的性能即锁相环的稳定性。

2 锁相环电路设计

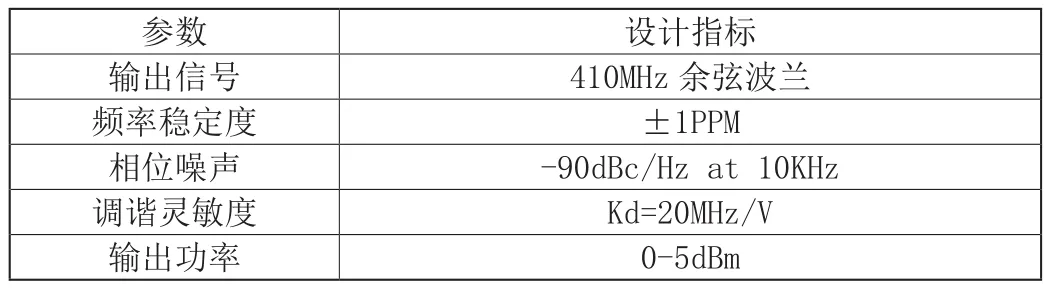

拟设计的高频锁相环的技术指标如表1所示。

表1 锁相环的技术指标

此锁相环的核心是频率合成器芯片ADF4116。使用单片机ATTINY26对内部寄存器进行操作,设定参考分频器和程序寄存器分频比及其他工作状态。参考频率选择高稳定度(±1PPM)的10MHz温度补偿晶体振荡器,输入ADF4116后首先经过参考分频器,分频后作为鉴相器的参考频率。鉴相器输出的电流大小反映了反馈频率和参考频率的差别,环路滤波器采用RC三阶环路滤波器,由于压控振荡器的输入端的电压较大,而频率合成器输出电压小,所以选择了运算放大器芯片AD820把误差电压信号放大,控制压控振荡器POS-535,输出信号即为410MHz的本地振荡器信号。下面具体介绍锁相环的各个部分模块电路设计和仿真。

(1)频率合成器。在实际设计中,选择了ADI公司的频率合成器[芯片AD4116,它集成了一个低噪声的数字鉴相器、一个可编程的分频器以及其它模块。另外可以通过简单的3-Wire接口控制片内的寄存器,从而方便地控制芯片的工作状态。

(2)单片机。选用Atmel公司的ATTINY26对频率合成器进行控制,这个控制器已经够用,没有必要使用ATmega8/16等比较高端的单片机。

(3)环路滤波器。采用三阶环路滤波器,环路带宽20kHz。主要作用是衰减误差电压的高频分量,提高抗干扰能力。

(4)运算放大器。由于三阶环路是有条件稳定的,而本锁相环又需要加一级运放来放大误差电压,因此设计中,将无源三阶滤波器和运放和二为一,采用二阶有源比例积分滤波器,既可以增加环路的稳定性,又可以有一定的高频增益,有利于环路的捕捉特性,还可提供足够的电压驱动后级压控振荡器。采用ADI公司的运算放大器AD820,实际上是用运算放大器实现二阶的低通滤波器电路,它的使用可以增加系统的稳定性。

(5)压控振荡器。当输出410MHz的信号时,调谐灵敏度是20MHz/V,同时调谐电压为8V。其主要技术指标如表2。

表2 POS-535的相关技术指标

3 设计方案仿真验证

利用ADI公司仿真软件对锁相环进行性能仿真,仿真结果从图1、图2可以看出,输出信号的中心频率完全达到了410MHz的设计要求,频率误差上也随着不断的锁定也逐渐趋于稳定,达到了设计要求。

4 结束语

本文分析了锁相环电路的基本组成和工作原理,着重从稳定性的角度出发,对高频的锁相环电路进行设计,给出了锁相环的设计方法,并通过软件仿真及实际电路的设计和调试,验证了设计的正确性。

图1 输出频率-时间图

图2 相位噪声图

[1]杨必文.一种CMOS电荷泵锁相环设计[D].电子科技大学,2014.

[2]陈超.CMOS压控振荡器的研究[D].南京理工大学,2013

Design of high frequency PLL circuit based on wireless transceiver

Gao Yan,Cao Wentian,Liu Zongwu

(unit 78156,Lanzhou Gansu,730020)

In the wireless transceiver circuit,except for transmitter and receiver,there is a very important part is the local oscillator circuit In order to ensure the stability of the local oscillation frequency of the output signal module and low phase noise,usually the vibration using PLL technology to achieve,especially in the field of wireless communications.This paper expounds the the basic structure and working principle of the phase-locked loop

Phase locked loop;phase discriminator;loop filter;voltage controlled oscillator