基于SystemVerilog的同步FIFO的验证平台搭建

2017-10-20邱玉泉刘世伟杨明翰

邱玉泉,曾 维,刘世伟,冯 坤,杨明翰

(成都理工大学 信息科学与技术学院,四川 成都610000)

基于SystemVerilog的同步FIFO的验证平台搭建

邱玉泉,曾 维,刘世伟,冯 坤,杨明翰

(成都理工大学 信息科学与技术学院,四川 成都610000)

针对于传统验证平台利用Verilog搭建的验证平台效率低,准确度低的局限性,提出了一种基于SystemVerilog系统级语言的验证平台建模方法,可以有效地降低复杂度和设计风险。由于FIFO在大多数工程中利用率极高,也极易出现问题,通过对FIFO模块进行验证平台建模,可以有效地降低设计与验证的时序竞争风险,实现验证平台的复用和验证过程中的自动监测,并且在搭建验证平台的过程中阐述了基本的验证流程,以及结合SystemVerilog语言介绍了一些基本建模规则和技巧。

验证流程;验证平台;SystemVerilog;FIFO

0 引言

以往在采用Verilog搭建测试环境时,设计者难以对测试环境进行分层设计,往往将大部分测试组件放在一个模块中[1]。SystemVerilog则采用面向对象编程(Object Oriented Programming,OOP)的思想来完成验证平台的分层建模。由于FIFO的功能并不复杂,因此将其中的一些放在一个组件来完成相关的功能[2]。

FIFO是一种先进先出的数据缓存器,根据工作时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作,而异步FIFO指读写时钟不一致,读写时钟是相互独立的[3]。

1 FIFO测试验证与分析

该FIFO使用16×8的FIFO,其接口包括datain写入数据、dataout读出数据、FIFO_push写入使能信号、FIFO_o_valid读出使能信号、rst复位信号、clk时钟信号、FIFO_rdy_n数据丢失测试信号以及FIFO_almost_full接近满指示信号[4]。

该FIFO包括正常写入写出情况、输出数据丢失情况。数据接近满时警告指示,数据满时无法写入。通过上述功能的描述,可以制定以下验证计划[5]:

根据FIFO的功能要求,制定相应的验证计划。其验证计划如下:① 验证FIFO是否能够正常读写,其FIFO读入数据与写出数据一致;② FIFO接近满时,fifo_almost_full拉高提示快满的指示;③ 在丢失数据的情况下,判断FIFO是否正常完成从FIFO中提取数据,进行输出,保证输出的数据不被丢失。

2 搭建验证平台

根据FIFO的功能不复杂和满足通用性的原则,搭建基于SystemVerilog的FIFO通用验证平台,可以满足基本FIFO的功能验证。现根据FIFO的功能以及为了验证代码的可维护性和可读性以及扩展性,将验证代码分为顶层模块、接口模块和测试模块3部分[6]。

2.1 顶层模块(TOP)

顶层模块包括时钟产生以及DUT例化程序。若在后续的FIFO验证过程,需要增加FIFO的一些其他功能端口信号,只需在该模块增加端口定义即可。时钟的频率也可以在此模块修改参数模拟实际情况FIFO的频率[7]。

时钟激励主要程序如下[8]:其中Simulation_cylce为时钟周期,每隔10 ns翻转一次。

parameter simulation_cycle =20;

forever begin

#(simulation_cycle/2) SystemClock =

~SystemClock;

end

2.2 接口模块(interface)

使用接口模块为了提高设计复用,降低错误风险,SystemVerilog采用接口(interface)对多个模块共同使用一组信号,实现封装,使之类似总线。该模块主要是实现连接、同步以及2个或多个块之间的通信功能,连接了设计块和测试平台[9],如图1所示。

图1 横跨两个模块的接口

本文将接口设计代码放在FIFO_io.sv文件中,用interface和endinterface将接口代码包裹在里面,并且声明信号的位宽以及接口类型,其部分代码如下:

interface fifo_io(input bit clk);

logic rst_n;

logic [DW-1:0] fifo2bus_data; //fifo to bus data

clocking cb @(posedge clk);

………

endclocking

modport TB(clocking cb,output rst_n);

endinterface

上面fifo_io的接口声明中,将接口中所要用到的所有信号都放入接口声明中,并且使用clocking……endclocking将同一个时钟域的信号包裹一起,这些代码在时钟clk上升沿发生时都处于激活状态[10],同时使用modport对这些信号指定方向[11]。

2.3 test模块

该文件主要编写所有FIFO所有情况下的验证代码,根据验证计划,主要分为正常读入写出情况和输出数据丢失情况。由于同步FIFO的功能较简单,故driver、monitor以及compare都以task的形式放在test模块中[12]。

由于仿真是可以无限仿真的,在test中增加了对仿真时间的控制,有利于减少仿真时间,并达到需要的效果。并且在其中增加了S|vcdpluson语句,以便可以生成vdp的波形文件,若需要使用fsdb波形文件,则可以用 S|fsdbDumpfile(“xxx.fsdb”)、S|fsdbDumpvars命令[13]。

仿真时间控制命令和生成波形文件的命令如下[14]:

S|vcdpluson;

# (300000*CLK_PRIOD);

S|finish;

根据验证计划,FIFO正常读写情况下,输入和输出在同时钟的控制下同步进行,FIFO不会出现空和满的情况,其模拟这种一直输入和输出的时序的主要代码如下[15]:

fifo.cb.fifo_i_data<=cnt;

tdata[cnt]<=cnt;

cnt<=cnt+1;

repeat(1) @(fifo.cb);

根据传输的机制,丢失数据的现象不可避免。根据FIFO的需求,该FIFO对丢失数据有相应的处理,故为了验证其FIFO的功能正确性,现根据需求模拟出FIFO丢失数据的情况。其核心代码如下[16-17]:

if(S| urandom_range(1,8)!=3) begin

fifo.cb.fifo_rdy_n<=1′b0;

ready<=1′b0;

repeat(1) @(fifo.cb);

end else begin

fifo.cb.fifo_rdy_n<=1′b1;

ready<=1′b1;

repeat(1) @(fifo.cb);

end

代码中根据S|urandom_range(1,8)!=3来模拟丢失数据的几率,此处根据实际应用场景来设置相应的概率。该FIFO具有提前警示FIFO几乎满的功能,当丢失数据个数超过24 h,其FIFO_almost_ful会拉高来警示FIFO快要满了。根据DUT中的相应的设计,其Verilog代码实现如下:

if( fifo_level > ({{(AW-3){1′b1}},3′b0}))

fifo_almost_full <= 1′b1;

if(fifo_level < ({1′b1,{(AW-1){1′b0}}}))

fifo_almost_full <= 1′b0;

在通常的情况下,经过FIFO数据量很大,通过肉眼观察波形来检查FIFO输入输出的数据是否正确,其效率极低。特别是在信号繁多,数据和协议复杂的情况下,更需要一种机制来自动检测DUT的功能和数据正确性。其monitor就是实现这种自动监控输出的机制,使验证更加高效可靠。以下是FIFO的monitor核心代码实现:

if(fifo.cb.fifo_o_valid) begin

rdata [r_cnt]<=fifo.cb.fifo_o_data;

r_cnt<=r_cnt+1;

repeat(1) @(fifo.cb);

end else begin

repeat(1) @(fifo.cb);

end

当monitor监测到输出时的有效数据时,需要通过将输出和输入数据进行自动比较,来检测FIFO在传输数据的过程是否改变了相应的值。其compare进行比较的核心代码实现如下[18]:

if(tdata[i]==rdata[i]) begin

S|display("tdata[%0d]=%0d",i,tdata[i],

S|display("rdata[%0d]=%0d",i,rdata[i],

S|display("-----SUCCESSFUL----- ");

repeat(1) @(fifo.cb);

end else begin

S|display("tdata[%0d]=%0d",i,tdata[i],

S|display("rdata[%0d]=%0d",i,rdata[i],

S|display("-----FAILED----- ");

repeat(1) @(fifo.cb);

end

3 验证结果的确认

验证结果的确认主要通过自动监测确认和波形确认,根据验证结果来判断FIFO设计是否符合设计要求。

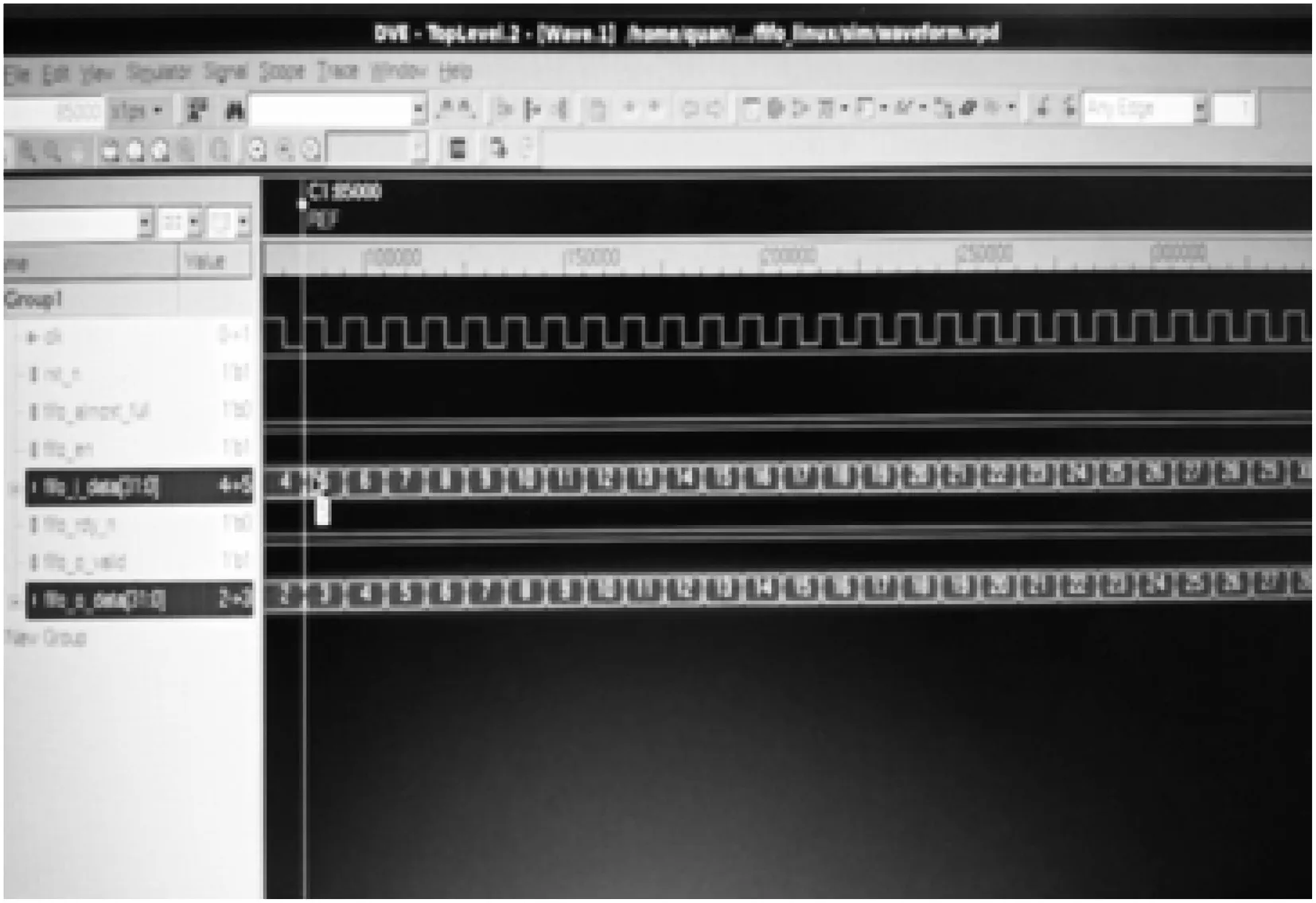

为了方便波形观察,本文采用计数的方式对FIFO进行输入。其FIFO正常读写情况下波形如图2所示,可以观察到波形中的输入输出数据来初步确定FIFO满足设计要求。

图2 FIFO正常读写波形图

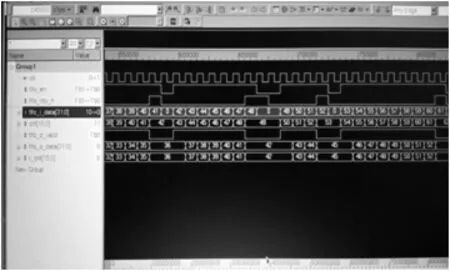

图3是在FIFO在丢失数据的情况下,可以看出FIFO在丢失数据时能够将数据保存下来,等待下一时刻有效时将丢失数据重新发送出去。

图3 FIFO丢失数据波形图

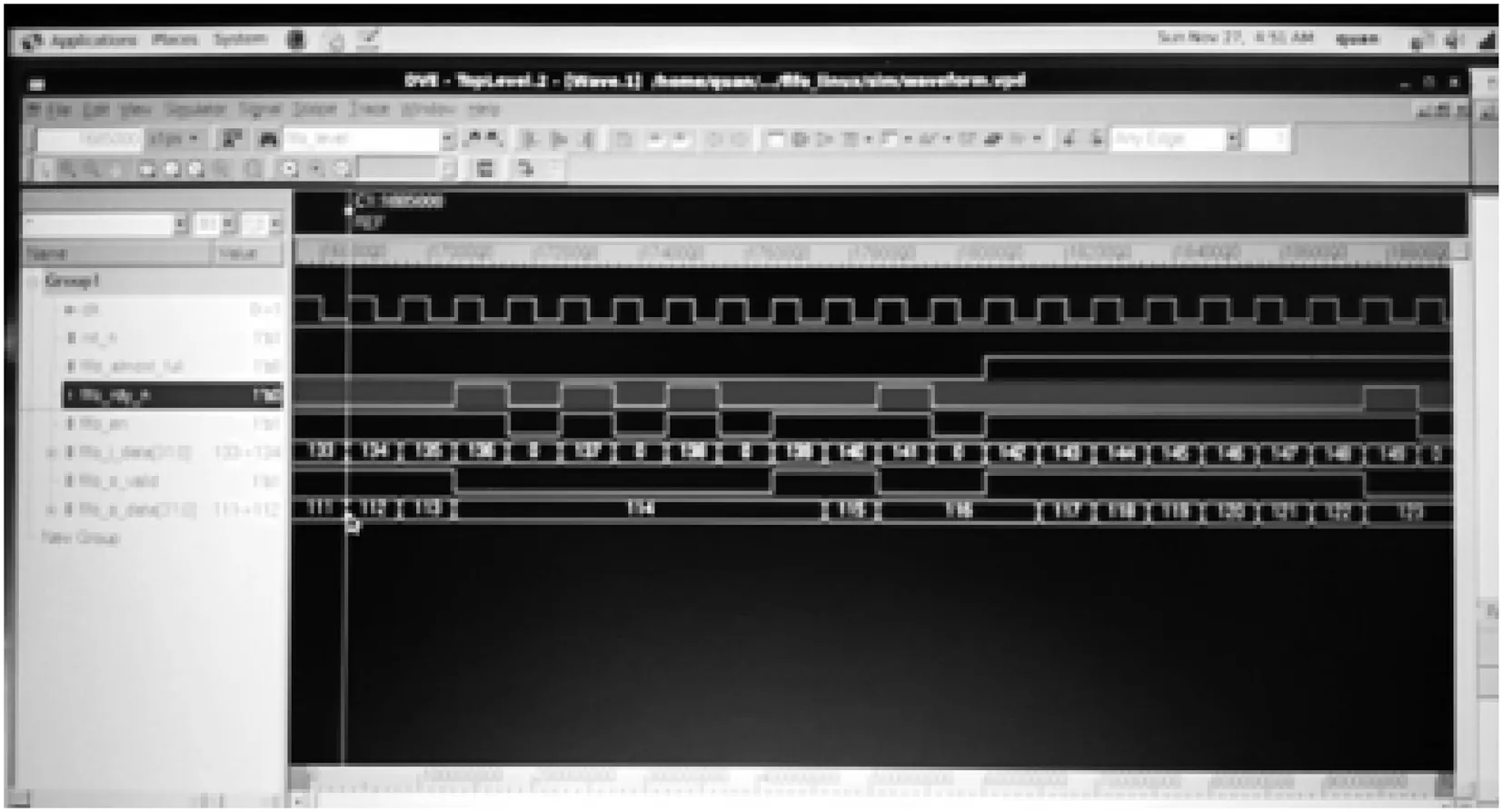

当丢失的数据超过24 h,fifo_almost_full几乎满信号拉高,如图4所示。

图4 几乎满信号波形图

根据monitor和compare的代码实现,其自动监测部分结果如下,通过打印的消息可得出结论,该FIFO设计满足功能的实现。

tdata[0]=0 300135

rdata[0]=0 300135

------------SUCCESSFUL------------

tdata[1]=1 300145

rdata[1]=1 300145

------------SUCCESSFUL------------

tdata[2]=2 300155

rdata[2]=2 300155

------------SUCCESSFUL------------

tdata[3]=3 300165

rdata[3]=3 300165

------------SUCCESSFUL------------

tdata[4]=4 300175

rdata[4]=4 300175

------------SUCCESSFUL------------

4 结束语

在此,介绍了使用SystemVerilog进行验证平台建模的一般原则和技巧,以及面对建模过程中使用的一些接口,将自动检测等新技术用于同步FIFO验证平台的建模中,并使用VCS仿真验证工具进行检验。结果证明,使用这些建模技术的设计的验证平台,很容易完成代码的复用和验证过程中的自动监测。

[1] 张明.Verilog HDL实用教程[M].成都:电子科技大学出版社,1999.

[2] SystemVerilog Testbench Workshop Student Guide[M].California:Synopsys Customer Education Services,2011.

[3] Cummings C E.Simualtion and Synthesis Techniques for Asyachrononous FIFO Design[M].USA:Sunburst Design,Inc.,2000.

[4] 张毅,周成英.高速同步FIFO存储器在数字信号源中的应用[J].电子技术,2003(11):48-50.

[5] Lam W K.Hardwave Design Verification:Simulation and Formal Method-Based Approaches[M].Upper Saddle River,NJ:Prentice Hall,2005:81-120.

[6] Janick B.Writing Testbench Using SystemVerilog[M].USA:Springer,2005.

[7] Janick B,Eduard C,Hunter A L ,et al.SystemVerilog 验证方法学[M].夏宇闻,杨雷,陈先勇,等,译.北京:北京航空航天大学出版社,2007.

[8] 张春,麦宋平,赵益新,译.SystemVerilog测试验证平台编写指南[M].北京:科学出版社,2009

[9] Stuart S,Simon D,Peter F.SystemVerilog for Design[M]. US:Springer:2006.

[10] Janick B.Write Testbenches Using SystemVerilog[M].USA:Springer,2006.

[11] Lam W K.Hardwave Design Verification:Simulation and Formal Method-Based Approaches[M].Upper Saddle River,NJ:Prentice Hall,2005.

[12] 常勇,申敏.一种基于事务的SoC功能验证方法[J].微计算机信息,2008,24(2):137-139.

[13] 闫沫,张媛.基于SystemVerilog语言的设计验证技术[J].现代电子技术,2008,31(6):8-11.

[14] Bhadra J,Abadir M S,Wang L,et al.A Survey of Hybrid Techniques for Functional Verification[C]∥Design & Test of Computers,2007:112-122.

[15] 钟文枫.下一代芯片设计与验证语言:SystemVerilog(验证篇)[J].电子设计应用,2008(12):61-67.

[16] 刘杰,徐伟杰,夏宇闻,等.设计验证中的随机约束[J].中国集成电路,2006(11):28-31.

[17] Willamette H D L.SystemVerilog for Verification Training[M].USA:Willamette HDL,2008.

VerificationPlatformofSynchronousFIFOBasedonSystemVerilog

QIU Yu-quan,ZENG Wei,LIU Shi-wei,FENG Kun,YANG Ming-han

(College of Information Science & Technology,Chengdu University of Technology,Chengdu Sichuan 610000,China)

This paper mainly introduces the practical verification environment of synchronous FIFO based on SystemVerilog structures,which breaks through the traditional limitations in verification platform modeling,can greatly improve the efficiency of chip test and interface protocol,and can effectively reduce the risk of design. The FIFO verification platform in this paper can effectively reduce the risk of the time sequence competition between design and verification,realize verification platform reuse and automatic monitoring in verification process. The paper also describes basic verification process,and introduces some of basic rules and modeling skills combined with SystemVerilog language in the process of building verification platform.

verification process; verification platform; SystemVerilog; FIFO

TP391.8

A

1003-3114(2017)06-64-3

10. 3969/j.issn. 1003-3114. 2017.06.16

邱玉泉,曾维,刘世伟,等.基于SystemVerilog的同步FIFO的验证平台搭建[J].无线电通信技术,2017,43(6):64-66,96.

[QIU Yuquan,ZENG Wei,LIU Shiwei,et al. Verification Platform of Synchronous FIFO Based on SystemVerilog [J]. Radio Communications Technology,2017,43(6):64-66,96.]

2017-07-23

邱玉泉(1992—),男,硕士研究生,主要研究方向:FPGA嵌入式设计与验证。曾 维(1976—),男,副教授,主要研究方向:数字电路设计和模拟电路分析。