数据采集系统ADC接口设计与实现

2017-09-28白晨边庆

白晨,边庆

(中航工业西安航空计算技术研究所,陕西西安,710068)

数据采集系统ADC接口设计与实现

白晨,边庆

(中航工业西安航空计算技术研究所,陕西西安,710068)

本文提出了基于AD7981的数据采集系统ADC接口设计方案。从硬件设计和软件开发两个方面阐述了ADC接口的具体设计和实现方法。ADC接口电路采用模数隔离设计,防止噪声串扰。模数转换芯片性能优越,留有较大的性能余量,扩展了系统的使用范围,前端信号调理电路引起的噪声和误差控制得当,使得ADC接口电路具备较高的准确性和可靠性。

数据采集系统;ADC;采样率;FPGA

0 引言

数据采集系统将自然界中的各种模拟量进行数字量化转换,给人们认识、理解和分析自然提供了更为直观的手段。数据采集系统中模数转换(ADC)接口的性能是保证采集系统结果的准确性和可靠性的重要指标。

1 系统需求分析

硬件设备的设计工作应该从系统的功能需求和性能需求分析开始。数据采集系统需具有较高的数据准确性和可靠性,ADC接口数据准确性和可靠性主要决定因素是ADC前端信号调理电路、ADC的采样精度和ADC的采样率。

1.1 ADC接口需求分析

1.1.1 ADC采样精度

ADC的采样精度比特数主要取决于系统所需的测量的动态范围,以及系统整机噪声水平和量化误差等因素。作为一个工程应用,系统的动态范围为超出需求,留有余量即可。

模数转换器的信号噪声比(S/N)是在模数转换器输出端测得的,信号用基波的均方根幅度表示,噪声是所有非基波信号的均方根之和。信噪比和量化数(ADC的位数)之间的关系是:

其中,ViRMS为输入信号基波的峰-峰值均方根,VeRMS为一个周期内误差信号的均方根。

若选用18bit的ADC,就有6.02*15+1.76=110.12dB的动态范围。本系统整机的噪声水平(指ADC前端的噪声水平)在60dB放大量约为40mV,ADC芯片的满量程为5V,因此噪声约占ADC芯片18bit中的,剩下14个bit就有84dB的动态范围,另外系统检测阀为22dB,这样就还有62dB的动态范围,加上60dB的前级放大,模拟信号采样前端的动态范围是122dB。本数据采集系统应用于声纳中声波信号采集,如果信号衰减只考虑传播损失,衰减可通过传播损失方程计算出来:

其中,r为传播距离,α为声波在水中传播吸收衰减系数,取经验值1dB/km。系统要求最远作用距离为r=4800m,此时的传播损失为76dB(<122 dB),所以18bit采样精度ADC芯片完全满足系统要求。

1.1.2 ADC的采样率

至于ADC芯片的采样率问题,主要是根据接收换能器接收信号频率以及定位算法的精度的要求。系统采样信号最高频点是125KHz,根据奈奎斯特采样定律,采样率最小为250KHz,考虑到留有一定的余量,将采样率设定为500KHz。

2 方案设计与实现

2.1 ADC硬件设计与实现

2.1.1 ADC工作方式和电路结构

本系统中使用满足需求的AD7982作为模数转换芯片,工作方式采用模式的三线式接口。仅使用CNV、SCK和SDO信号,可将线路连接减至最少,在隔离应用中非常有用。此模式时序如图1所示。

根据工作方式、实际需求和ADC芯片类型设计模数转换电路结构如图2所示,其中包括提高输入阻抗的输入模拟信号跟随器,实现输入信号单端转差分的转换器。

图1 三线模式串行接口时序图(SDI高电平)

图2 AD7982模数转换电路结构

2.1.2 ADC转换数值与模拟输入电压的函数关系

ADC芯片AD7982的差分输入端IN+和IN-之间的差值电压为,参考电压是RDF×2。AD7982是18bit的模数转换器,实际中只选用高16bit数据。则AD7982数字数据输出的满量程为216,AD7982的模拟测量范围为[-2REF,2REF](因为模拟输入被驱动器ADA7941衰减成原来的,所以在正电压的数字输出满量程就是32767,负电压的数字输出满量程就是-32768。所以ADC的转换函数就是:

2.2 FPGA控制ADC接口和管理ADC数据程序设计

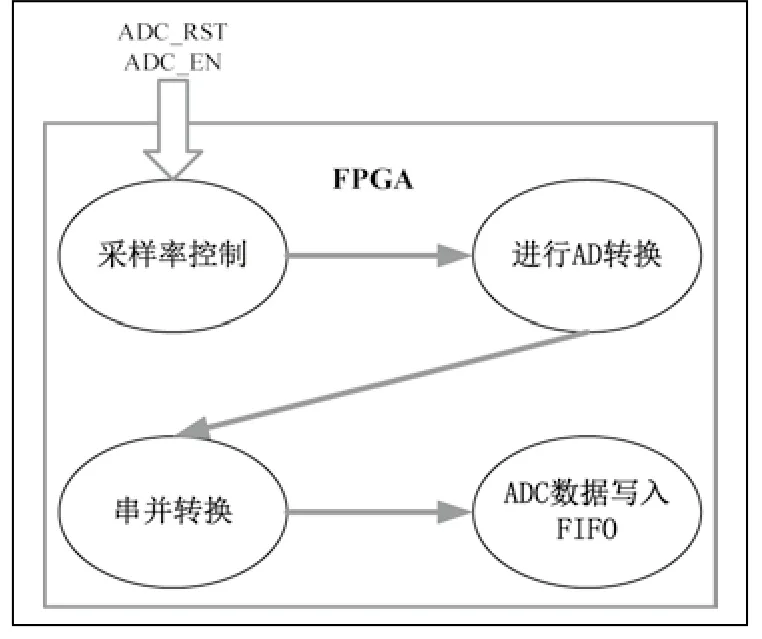

FPGA通过使用One-hot状态机控制ADC和读取ADC数据,之后数据缓存在FPGA内部FIFO中。FPGA控制ADC接口和管理ADC数据的程序的状态如图3所示。当外部控制信号ADC_RST和ADC_EN都有效时,ADC启动;根据系统中采样率的要求,进行转换率控制,启动ADC转换;一次ADC转换结束之后,将转换后的数据读出,同时进行串并转换;串并转换完成之后,将数据送入FIFO,FPGA准备启动下一次模数转换。

图3 FPGA控制ADC和管理数据程序状态图

AD7982使用芯片内置时钟,数据输出使用外部时钟SCK信号。数据在SCK下降沿输出,提高数据的输出速率。使用FPGA给AD7982提供数据输出时钟SCK。

图4 FPGA控制ADC转换程序状态图

FPGA使用状态机One-Hot模式控制AD7982。首先进入ADC复位状态,初始化CNV、SCK和清零时钟计数clk_count;接下来进入ADC转换状态,拉高CNV信号,在这个状态中等待AD7982完成数据转换,等待0x2F个clk,即940ns,满足AD7982转换时间最大710ns的要求;等待转换完成进入ADC数据输出状态,拉低CNV信号,使用ADC时钟计数信号clk_count的0位作为SCK信号,则SCK的频率为clk/2=25MHz,使用SCK下降沿作为FPGA读取AD7983串行数据的触发电平,循环执行读取AD7982数据操作18次,即18个SCK时钟,完成此次18bits的数据读取;读完ADC数据之后进入写FIFO状态,置ADC数据读取完成标志信号sample,等待时钟计数clk_count等于SAMPLE_CLK_COUNT后进入ADC复位状态。至此,一次ADC控制和数据读取操作完成。状态转换图如图4所示。

根据上述接口时序控制,完成一次ADC数据转换和数据读取需要的时间是SAMPLE_CLK_COUNT个adc_clk,可计算出本系统ADC的采样率是:

这样就通过SAMPLE_CLK_COUNT的值间接控制了ADC的采样率。

3 结论

图5 实航和仿真轨迹图

本系统应用在某型声纳,用于对目标的三维轨迹进行测量。图5所示为根据采集数据计算运动轨迹与目标实际航行轨迹的对比,图中直线为目标实际航行轨迹,非直线为根据采集数据计算的运动轨迹,0.5%的定位误差满足设计指标。

[1]席德勋.现代电子技术[M].北京:高等教育出版社,1999.

[2]乌立克(美)洪审 译.水声学原理[M].哈尔滨:哈尔滨船舶工程学院出版社,1990.

ADC interface design and implementation in data acquisition system

Bai Chen,Bian Qing

( Xi’an Aeronautic Computing Technique Research Institute, AVIC, Xi’an Shaanxi, 710068)

This paper puts forward the design of system of ADC interface based on AD7981. It describes the ADC interface of the design and implementation from the hardware design and software development aspects.ADC interface circuit using modular isolation design, to prevent noise crosstalk. The ADC chip is superior in performance, extending the range of use of the system, and the noise and error control caused by the front-end signal conditioning circuit, making the ADC interface circuit with high accuracy and reliability.

Data collection; ADC;Sampling rate;SRAM