改进型CIC抽取滤波器的FPGA实现

2017-09-07谢海霞赵欣

谢海霞 赵欣

摘 要: 为了解决以往设计的CIC抽取滤波器存在的数据速率高以及功耗高的问题,研究了改进型CIC抽取滤波器的FPGA实现过程,优化CIC抽取滤波器硬件实现结构,采用FPGA实现抽取滤波器的设计。分析CIC抽取滤波器的硬件实现结构和位宽,通过Hogenauer抽取滤波器结构,得到6级16抽取的CIC硬件实现结构,将该结构变换成4个CIC抽取滤波器的级联式FPGA实现,逐级降低数据速率,提升数据位宽。以FPGA实现CIC抽取滤波器过程中,分析了其运算时寄存器所需的最高位宽,避免产生数据溢出问题。实验结果表明,所设计的改进型CIC抽取滤波器是有效的,可降低数据速率和系统功耗。

关键词: Hogenauer; CIC抽取滤波器; 数据速率; FPGA

中图分类号: TN713?34; TP368.1 文献标识码: A 文章编号: 1004?373X(2017)16?0148?03

Abstract: In order to reduce the data rate and power consumption of the previously?designed CIC decimation filter, the FPGA?based realization process of the improved CIC decimation filter is studied, the hardware implementation structure of the CIC decimation filter is optimized, and FPGA is used to design the decimation filter. The hardware implementation structure and bit wide of CIC decimation filter are analyzed. The filter structure is decimated through Hogenauer to get the CIC hardware implementation structure whose decimation rate is 16 and decimation degree is 6. The structure is transformed into four cascaded CIC decimation filters implemented with FPGA, which can reduce the data rate and improve the data bit wide. In the implementation process of CIC decimation filter with FPGA, the highest bit wide required by the register while it is operating is analyzed to avoid the data overflow problem. The experimental result shows that the modified CIC decimation filter is effective, and can reduce the data rate and system power consumption.

Keywords: Hogenauer; CIC decimation filter; data rate; FPGA

0 引 言

地震檢波器是地震数据采集系统的核心部件,其可检测到微弱信号,具有较高的探测性能。地震检波器的关键部件是抽取滤波器芯片,芯片可对前端伺服电路调制形成的高速低位数据流实施数据滤波处理,将高速率的低位数据流变换成低速率的高位数据流,完成噪声的限制以及数据的准确采集[1]。CIC(Cascaded Integrator Comb)抽取滤波器是无线通信中的常用模块,其可运行在高采样频率环境中,实现去噪、降采样以及避免混叠等功能。而以往设计的CIC抽取滤波器存在的数据速率高以及功耗高的问题[2],因此,研究改进型CIC抽取滤波器的FPGA实现具有重要意义。

1 改进型CIC抽取滤波器的FPGA实现

1.1 CIC抽取滤波器的硬件实现结构和位宽分析

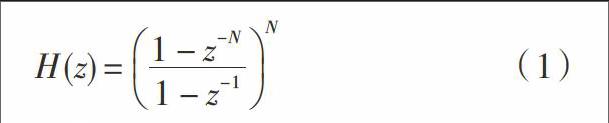

设置CIC抽取滤波器的抽取率是M,级数是N,CIC抽取滤波器的系统函数为:

[H(z)=1-z-N1-z-1N] (1)

设置N=3,基于上述能够获取CIC抽取滤波器的实现结构,如图1所示。按照易位定理再次排列图1描述的结构,获取图2所示的结构。依据Nobel恒等式原理,可对CIC抽取器的先后位置进行排序,确保采用最简单的方式完成系统。若线性系统[F(zN)]后面级联着M倍抽取器,则有:

对CIC抽取滤波器进行优化时,应分析其运算时的位宽问题,避免形成数据溢出问题。从图3能够看出CIC的前级是级联的积分器,按照数字滤波器原理可得,极点不再单位圆内的滤波器是不稳定的。CIC抽取滤波器结构中存在零/极点互相抵消现象[4],说明其是FIR滤波器,是一个因果系统。若获取滤波器输出数据的位宽[5],则滤波器运算时中间寄存器都使用该位宽,可弥补出现有价值数据溢出的问题。

CIC抽取滤波器仅能进行加法运算,两个相同位宽的补码数据融合,输出结果位宽加1,则CIC抽取滤波器的输出位宽运算公式是:

式中:[Wo]是CIC抽取滤波器的输出位宽;[Win]是输入位宽;M是CIC抽取滤波器的抽取率;N是其级数。

1.2 CIC抽取滤波器FPGA实现结构优化

设计的CIC抽取滤波器的抽取率M=16,级数N=6,其系统函数是:endprint

通过Hogenauer抽取滤波器结构,获取6级16抽取的CIC硬件实现结构,如图4所示。

CIC抽取滤波器和sigma?delta调制器级联后,调制器的输出数据位寬是1 b,此时CIC抽取滤波器的输入数据位宽按照2 b运算[6],则有[Win=2],则依据式(3)可获取CIC抽取滤波器的输出位宽是26 b。因此,滤波运算时的中间级寄存器的位宽应为26 b,滤波器的输入数据速率是128 kHz,滤波运算的操作频率为8 kHz。采用该结构FPGA实现[7],使得长字节在高速率下运行,极大地提升了系统的功耗。

为了降低CIC抽取滤波器的功耗,需要对图4结构实施改进,将6级16抽取CIC抽取滤波器系统描述成:

基于式(7)能够得出,将6级16抽取CIC抽取滤波器变换成4个CIC抽取滤波器的级联实现[8],该4个CIC抽取滤波器的级数都是6,抽取率是2。改进后的CIC抽取滤波器的FPGA实现结构如图5所示。图5描述了各滤波器的输出速率以及位宽情况。

分析图5可得,CIC抽取滤波器级联式FPGA实现后,能够逐级降低数据速率,逐级提升数据位以宽到26 b。首个级CIC1内,其滤波运算操作频率是128 kHz,中间级寄存器位宽为8 b,末级CIC4内的中间级寄存器的位宽是26 b,但是其滤波运算处理频率是16 kHz,使得长字节运行在低速率状态下,极大降低了系统的能耗。

2 抽取滤波器的仿真与板级调试结果

2.1 Modelsim仿真结果

Modelsim是一种FPGA仿真软件,其线编写检测文件为testbendi,可向总体滤波器系统提供一个时钟。Sigma?deha调制模块调制125 Hz抽取滤波器检测信号和500 Hz合成的正弦波信号,获取输出功率是128 kHz的bit数据流,该数据流是抽取滤波器的输入端[9]。CIC抽取滤波器通过Modelsim仿真后,得到的仿真结果如图6所示。

图6描述的是CIC抽取滤波器输出数据的模拟格式显示,从图中能够看出CIC抽取滤波器降低了数据速率,输出中仍然包含两个频率成分的正弦波,说明本文设计的抽取滤波器在结构设计以及功能上的准确性。

2.2 板级调试结果

将设计的改进型CIC抽取滤波器的程序下载到开发板上运行后,通过FPGA片上调控工具SignalTap Ⅱ采集各级CIC抽取滤波器的输出,对检测电路实施编译,下载到cy?clone系列EP1C12Q240C8器件后,对改进型CIC滤波器的FPGA实施板级调试,通过Matlab读出数据并实时处理,获取的实时波形如图7所示。

分析图7中的检测结果可得,数字正弦信号X通过4个6级CIC抽取滤波器的2倍抽取后,采样率降低,波形粗糙。说明本文设计的改进型CIC抽取滤波器能降低采样率、抑制噪声,完成数据滤波操作。

2.3 资源和功耗检测结果

实验为了对CIC抽取滤波器的电路实施对比,通过Design compiler对常规结构CIC抽取滤波器和本文滤波器的资源以及功耗进行检测,结果如表1所示。从表1能够看出,相对于常规结构的抽取滤波器,本文设计的抽取滤波器的功耗更低。

表1 不同抽取滤波器的资源和功耗检测结果

3 结 论

本文研究了改进型CIC抽取滤波器的FPGA实现过程,对CIC抽取滤波器硬件实现结构进行了优化,采用FPGA实现了抽取滤波器的设计。

参考文献

[1] 王大伟,贾荣丛,王划一.基于Matlab的巴特沃斯滤波器设计[J].现代电子技术,2012,35(21):71?72.

[2] 徐远泽,戴立新,高晓蓉,等.FIR滤波器的FPGA实现方法[J].现代电子技术,2010,33(22):64?67.

[3] 李飞,冯晓东,李华会.可变带宽数字下变频的设计与FPGA实现[J].电子技术应用,2016,42(4):35?38.

[4] 赵林军.根升余弦脉冲成形滤波器FPGA实现[J].现代电子技术,2011,34(1):23?25.

[5] 黄猛,唐琳,甄玉,等.基于自适应遗传算法FIR数字滤波器优化设计[J].现代电子技术,2010,33(2):143?146.

[6] 聂伟,王天明,邱蓉.改进的时钟偏斜误差校正方法的FPGA实现[J].微型机与应用,2016,35(7):83?86.

[7] 李峰.一种基于宽带信号的抽取滤波器设计[J].舰船电子对抗,2015,38(2):93?96.

[8] 邹兴宇,程树英.优化FIR数字滤波器的FPGA实现[J].现代电子技术,2011,34(6):151?153.

[9] 孙晨,赵毅强,刘强,等.宽带通信芯片中级联积分梳状插值滤波器的优化设计[J].计算机工程,2015,41(8):252?255.

[10] 杨晓晗,李彬华,丁旭.基于FPGA的光栅信号FIR滤波器实现[J].化工自动化及仪表,2016,43(3):272?276.endprint