一种数字接口设备的FPGA应用方案设计

2017-09-03江燕良田晓鹏

江燕良,田晓鹏

(1.许继电气技术中心,许昌 461000;2.许昌市供电公司)

一种数字接口设备的FPGA应用方案设计

江燕良1,田晓鹏2

(1.许继电气技术中心,许昌 461000;2.许昌市供电公司)

针对光纤电流差动保护面临的时间同步和误码校验等技术问题,提出了一种数字接口设备的FPGA应用实现方案。该方案以改善信息传输时延为切入点,从传输方式和码型转换等方面出发,减少了信息传输的中间环节,提高了信息传输的可靠性。同时,使用E1芯片进行信息编码的转换和传输,改善了信息的传输带宽,很好地解决了误码校验精度的问题。

光差保护;SDH系统;FPGA;E1芯片

引 言

随着电力通信网络的日益完善,光纤通信技术在电力系统继电保护领域的应用也越来越广泛。传输容量大、传输距离远、抗电磁干扰能力强和运行可靠性高等天然优势,使其成为电力系统信息传输的主要手段。光纤电流差动保护以其稳定可靠的光纤传输通道保证了电流的幅值和相位可以正确地传送到对侧。目前光纤大多采用64 Kb 数字通道,电流差动保护通道中既要传送电流的幅值,又要传送时间同步信号,通道资源紧张,要求数据的误码校验位不能过长,这样就影响了误码校验的精度[2]。而且光纤复用接口的实现需要借助光纤通信系统SDH等同步传输网来实现信息交互保护。为了保证传输的信息准确、可靠,选用传输容量大的E1 (2.048 Mbps)数字接口,不但很好地解决了误码校验精度的问题,而且SDH设备基本都支持E1接口接入。本文将FPGA与光纤传输技术相结合,基于FPGA的可扩展性强、灵活方便的优点,通过硬件编程语言在FPGA内部设计功能模块,完成光电转换器与E1芯片之间的传输转换。

1 系统概述

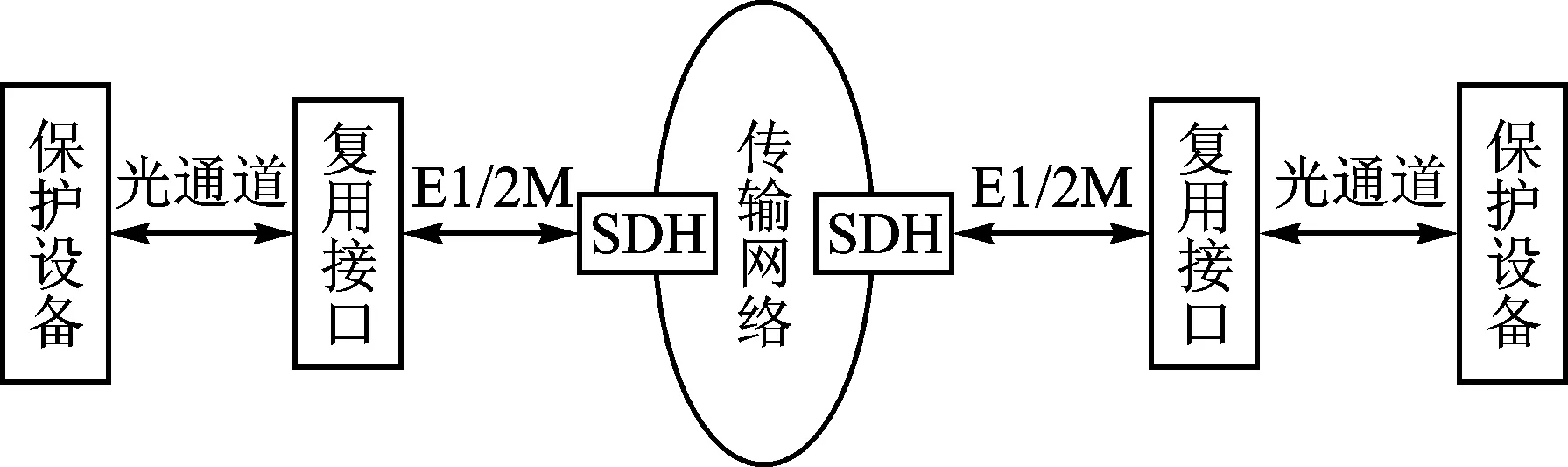

光通信接口设备是光纤纵差保护实现信息远距离传输不可缺少的中间环节,它的可靠性直接影响光差保护系统性能。光差保护远方通信信号转换装置OTEC-2M是由许继电气股份有限公司生产的,是WXH-803/803A、WXH-813/813A等高压线路保护装置的配套产品。保护装置将数据通过光纤链路传输到OTEC-2M,OTEC-2M按照E1信道的通信标准将信号转换成2.048 Mbps 波特率、HDB3编码方式的电信号,通过同轴电缆传输到SDH网络设备,对侧保护装置再通过SDH网络实现数据交互。它完成保护设备光接口到通信设备电接口的通信,并实现2.048 Mbps 传输路由的无损伤切换,为继电保护设备的数据传输提供全透明的传输通道。装置安装在变电站或电厂的通信机房内,与数字通信设备放置在一起,通过75 Ω的同轴电缆与通信设备的2.048 Mbps 终端相连。光纤与安装在主控室/保护室的光纤纵差保护光纤接口相连接,应用方式如图1所示。

图1 应用方式

2 系统构成及工作原理

2.1 系统构成

系统的硬件电路主要由如下几部分组成:

① 电源供电电路,提供系统所需要的5 V、3.3 V和1.2 V电源。

② 时钟管理电路,为系统提供一个稳定的时钟源。其中FPGA和E1芯片各有一个独立的晶振回路为其提供时钟信号,满足芯片内部逻辑功能需要。另外为了保证FPGA和E1芯片之间数据收发同步,将一个时钟信号通过分频分别提供给FPGA和E1芯片。

③ FPGA控制电路,负责E1接口芯片通信中的成帧、解帧、接口通信、硬件配置和控制等。采用Xilinx公司的XC6SLX4-2TQG144芯片作为系统的核心控制器,时序控制精度高,具备并行处理的能力,实现方法简单可靠,无需外部电路便可进行编码方式的切换。

④ E1接口电路,主要负责进行码型变换、信号电平变换、接口阻抗匹配、输出波形形成和时钟恢复等。XRT82D20是EXAR公司生产的E1接口芯片,符合G.703等国际标准规范,其信号编码采用HDB3双极性归零码实现数据传输。输入输出阻抗具有75 Ω、120 Ω两种模式,输入电压也有3.3 V和5 V两种。一般采用一对同轴电缆实现非平衡方式传输,也可以采用两对屏蔽双绞线实现平衡方式传输[3]。

⑤ 光收发模块电路,完成光电信号转换并进行传输。光电转换器选用宇光的GTL9系列光电转换器,光纤的传输方式采用单模光纤,根据传输距离的不同,波长可以选用1300/1310 nm或1500/1550 nm两种[4],传输距离可达40 km。

2.2 工作原理

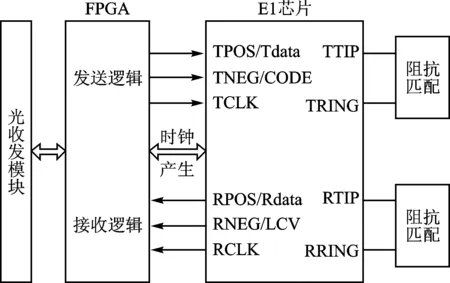

OTEC-2M光差保护远方通信信号转换装置采用E1接口芯片进行码型转换,实现了FPGA内的曼彻斯特码或1B4B 码与HDB3 双极性归零码之间的编码转换,完成光纤转换成E1(2.048 Mbps) 数字接口。它不能作为一个独立的设备运行,只能与WXH-800系列光纤纵差保护配合使用。该装置由光电变换、发送码型变换、发送码极性转换、收发终端及接收码极性转换和接收码型反变换几个部分组成,系统工作原理框图如图2所示。光电变换回路实现光信号和电信号之间的转换,它用于连接OTEC-2M和WXH-813系列纵差保护装置光纤接口。码型变换回路是将保护侧传来的光纤编码信号转换成符合ITU.-G.703的2.048 Mbps同向接口规约的信号方式。收发终端实现与数字通信设备2.048 Mbps同向接口的码型的单、双极性转换以及电平、阻抗匹配。

图2 系统工作原理框图

3 系统设计

系统提供单通道的光纤通信接口和E1通信接口,主要由FPGA与E1芯片完成信号传输和码型转换。继电保护装置之间的光纤通道通信方式采用2 Mbps 复用方式。系统使用75 Ω非平衡同轴电缆延长至集控远动屏位置,提供BNC接口[5]。系统总体架构如图3所示。

图3 系统总体架构框图

3.1 硬件设计

系统硬件设计分为电源供电电路、时钟管理电路、E1接口电路和FPGA控制电路。

① 电源供电电路。系统支持DC 220 V、DC 110 V或DC 48 V电压输入,通过不同的电源模块将输入的电压转为5 V,然后再由转换芯片将5 V转换为3.3 V和1.2 V,分配到各个子电路中。电源供电电路主要为E1接口部分、FPGA部分、时钟管理部分和外围接口芯片部分电路供电。

② 时钟管理电路。系统选用了两种工作频率的晶振芯片,分别为系统输出2.048 MHz和65.536 MHz的时钟信号,其中65.536 MHz的时钟信号提供给FPGA芯片,作为时钟基准,用于处理从保护装置接收的信号。另外,FPGA还需要给E1接口芯片一个2.048 MHz 的参考时钟,用于恢复E1接收端的数据和同步。为了确保FPGA芯片和E1接口芯片通信时的时钟同步,采用ICS8302时钟芯片产生两个2.048 MHz的时钟信号,分别提供给FPGA和E1芯片。同时,E1接口芯片还需要一个2.048 MHz的时钟信号来供芯片内部逻辑使用。

③ E1接口电路。本文采用的E1接口电路,其输入阻抗为75 Ω,输入电压为3.3 V。E1接口详细设计电路如图4所示。

④ FPGA控制电路。系统接收和发送的数据均在FPGA中进行处理,除光电转换器完成光电信号转换以及E1芯片完成HDB3编解码功能外,其他功能均通过FPGA内部可编程逻辑实现。FPGA有三种配置方式:主动串行AS配置方式、JTAG配置方式、被动串行PS配置方式。对于这三种配置方式,通过设置FPGA上的 MSEL0、MSEL1两个引脚的状态进行选择[6]。本文采用主动串行AS配置方式,即MSEL0接高电平,MSEL1接地。信号编码方式(1B4B或曼彻斯特编码)通过跳针选择与保护装置对应的编码方式来控制。

3.2 FPGA设计

FPGA在上电加载程序完成后,对E1芯片进行初始化。光纤信号由光电转换器转换成电信号,经FPGA内部接收模块处理,再发送给E1芯片进行编码转换。FPGA程序设计功能框图如图5所示。具体流程如下:

① 光差信号转换装置通过光电转换器接收保护装置传输的光信号,并将其转换为1B4B或曼彻斯特编码方式的串行电信号,再通过RD端口进行传输。FPGA以其内部时钟为基准对这些串行信号进行采样,并将采样的数据存入缓存区FIFO。接收和存储过程通过状态机实现,根据通信协议设定的空闲码实时检测并判断数据是否有效,从而判断是否存入FIFO。

② FPGA接收时钟以内部时钟为基准接收缓存区的数据,而发送时钟以本地分频时钟为基准,考虑到两种时钟可能存在偏差,发送模块在缓存区存储两个字节的有效数据之后再从缓存区FIFO读取数据并进行发送,同时将缓存区的深度设置足够大,避免缓存区同时读写可能导致的空读或溢出现象。在缓存区为空的情况下,发送模块一直向E1芯片发送空闲码。

③ FPGA通过其发送模块以分频得到的2.048 MHz时钟为基准,将待发送串行数据发送给E1芯片的TData端口。最后,E1接口芯片将E1信道输入的信号,以分频得到的2.048 MHz时钟为基准,将信号编码转换为HDB3码形式,最后经同轴电缆传输至SDH主干网络。

图5 FPGA程序设计功能框图

当信号进行反向传输时,E1信号首先经接口变压器变换后将信号通过RData端口传输给FPGA;FPGA将E1线路接口单元传输的数据送入时钟提取模块,提取出时钟并进行处理、接收和缓存,最后传输给光电转换器的TD端口。

正向和反向传输的存储模块均通过FPGA内置FIFO缓存来实现,FIFO深度可通过判断标志位是否为空以及已存储数据个数进行配置。正向和反向传输功能独立,互不影响。它们的缓存模块均可同时进行读写操作,发送模块无需等待接收模块是否已将有效数据帧完全接收并存储完成,便可启动发送,减少通信延迟。

4 系统测试和分析

4.1 功能测试

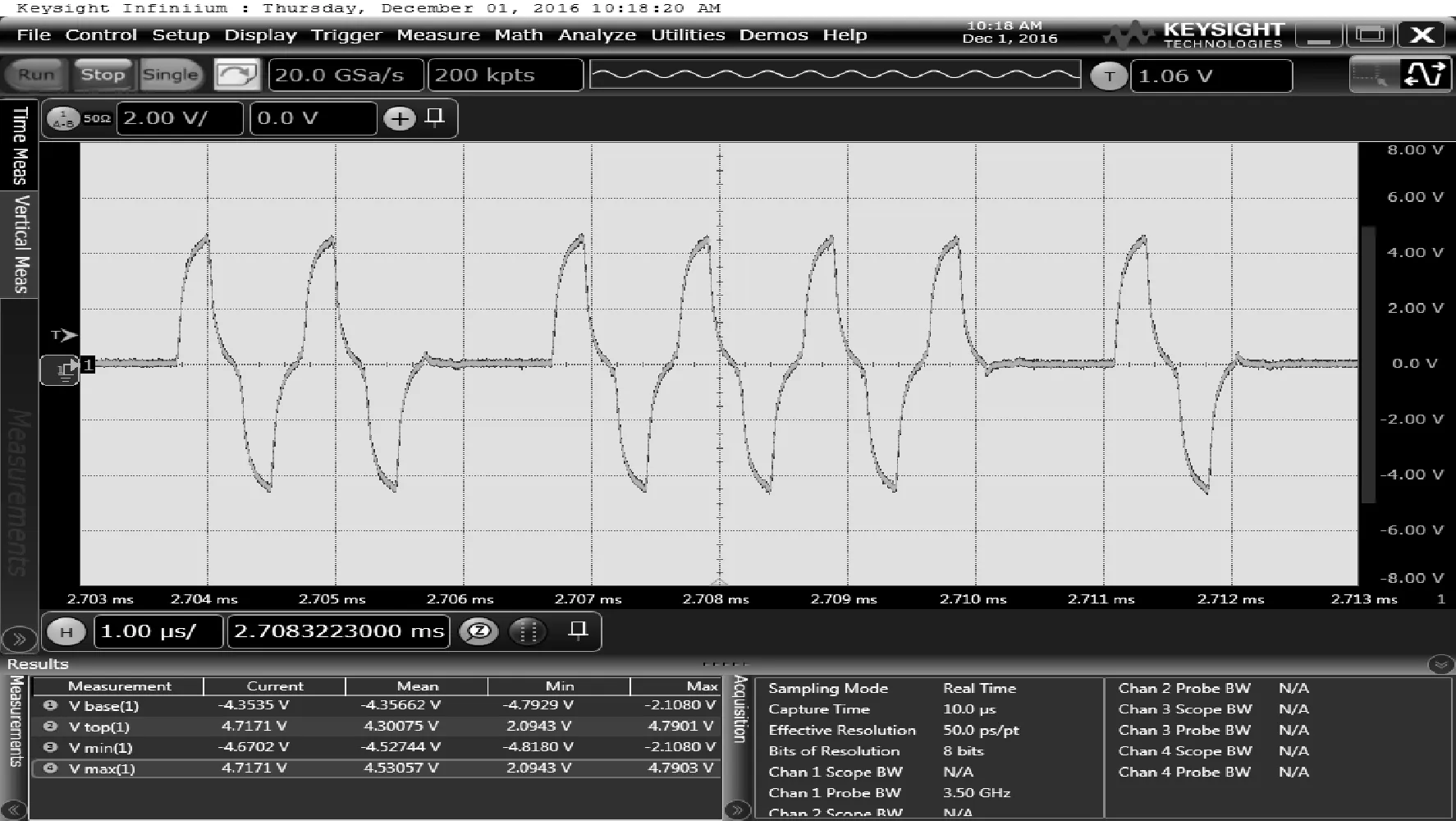

为了验证系统是否满足各项功能以及电磁兼容性能指标,首先用示波器对E1接口的输入和输出波形进行测试。

试验方法:将一台OTEC-2M装置和一台光纤差动保护装置WXH-803A用尾纤分别连接对应的收信和发信,另外将OTEC-2M连接约5 m长的同轴电缆,电缆两端分别对应装置的收信和发信,采用自环方式。通过观察、记录WXH-803A装置的通道状态误码率来判断各种电磁干扰对OTEC-2M的影响。所有试验的干扰等级都是相应电压等级装置的最高级,实验过程中WXH-803A装置的通道状态误码率保持不变为合格。分别对E1接口芯片的发送端TTIP和TRING、接收端RTIP和RRING差分信号进行波形测量,波形图如图6、图7所示。

图6 发送端(TTIP和TRING)波形图

图7 接收端(RTIP和RRING)波形图

4.2 电磁兼容测试

按照同样的试验方法,对系统进行了电快速瞬变、浪涌抗扰度、静电放电抗扰度、阻尼振荡磁场、辐射发射、传导发射、振动、冲击和高低温等试验,并对测试结果进行分析论证。

以上实验结果表明,光纤通道里的误码数和丢帧数并没有发生变化,而且装置无机械损坏现象,重新上电后功能正常。测试结果满足试验要求,系统工作稳定。

结 语

[1] 王芊,金华锋,石铁洪,等.用于差动保护的E1速率通信接口[J].电力系统自动化,2003,27(7):55-57.

[2] 任亮.光纤通信在电力系统继电保护中的应用[J].中国新技术新产品,2010(21):141.

[3] 程晓东.光线保护接口技术[J].供用电,2007,24(4):28-30.

[4] 李峥峰,杨曙年,喻道远,等.继电保护中光纤通信技术应用[J].电力自动化设备,2007,27(2):75-79.

[5] 田新成,尹秀艳.一种处理调度自动化E1通道通信异常的方法[J].电力系统通信,2012,33(7):66-69.

[6] 钟鸿锐.基于FPGA的E1误码测试技术研究[D].西安:西安电子科技大学,2010.

江燕良(工程师),主要研究方向为变电站二次设备硬件平台开发;田晓鹏(工程师),主要研究方向为电力系统继电保护和电力通信。

FPGA Application Scheme Design of Digital Interface Devices

Jiang Yanliang1,Tian Xiaopeng2

(1.Xuji Electrical Technology Center,Xuchang 461000,China;2.Xuchang Power Supply Company)

In view of the optical fiber current differential protection face technical problems such as time synchronization and error checking,a digital interface device FPGA implementation scheme is proposed.The scheme takes the efficiency of information transmission as the breakthrough point,from the transmission way and the type of transform,which reduces the information transmission of the intermediate links,and improves the reliability of information transmission.At the same time,the use of E1 chip to convert the information coding and transmission improves the information transmission broadband,and solves the problem of the error calibration accuracy.

optical differential protection;SDH system;FPGA;E1 chip

TM774;TN913.7

A

�士然

2017-04-28)