基于CMOS工艺的自动增益控制电路研究

2017-08-30梁娟

梁 娟

(新疆工业职业技术学院 能源与电气工程系,乌鲁木齐 830022)

基于CMOS工艺的自动增益控制电路研究

梁 娟

(新疆工业职业技术学院 能源与电气工程系,乌鲁木齐 830022)

在无线接收机中,天线接收的信号强度往往变化很大,自动增益控制环路(automatic gain control,AGC)根据这个信号强度来动态调节控制放大器的增益,向后级基带电路(如ADC)提供幅度恒定的信号,使得接受到的不同强度信号均能被正确接收和解调;为了达到通过识别接收机接收信号的强度动态调节放大器的增益,以实现输出信号幅度恒定的目的,文章基于TSMC90nm CMOS工艺着重论述了针对70 MHz中频信号的AGC电路设计过程,详细设计了AGC各模块电路,并从提高线性度、降低直流失调和提高稳定性等方面对电路进行了优化,主要介绍AGC芯片的版图设计并进行了后仿,给出了整个AGC系统的工作特性和各项指标;在电路设计过程中,针对线性度、输出信号幅度、增益控制范围等进行改进与优化,得到符合设计指标的电路结构;最后对AGC环路的性能进行仿真验证,得到该AGC在满足输出信号幅度和线性度的基础上达到了30 dB的动态范围,满足了接收机系统的要求。

CMOS;自动增益控制;可变增益放大器;dB线性;1 dB压缩点

0 引言

科学技术的发展日新月异,在过去十几年中,以手机等无线设备终端为代表的无线通信产品的快速普及和更新换代使得我们的工作方式和生活方式都发生了巨大而深刻的变化。在无线接收机中,由于信道是非理想的且处于不断变化中,天线从外部接收到的信号强度也是变化的。为了保证良好的接收效果,在接收机中通常使用自动增益控制,自动增益控制(AGC)系统可以用于混频前的射频放大级,但主要是应用于中频放大级。本文以无线接收机为背景,设计了一款增益动态范围为30 dB的AGC电路,论述了其基本原理和设计方法,并对其进行了仿真验证。

1 自动增益控制电路设计方案

本文希望设计一款可以应用于70 MHz中频的增益连续可调的放大器,这就要求我们应选择模拟型AGC环路且3 dB带宽包含70 MHz。接收机对本级增益动态范围要求是大于30 dB,考虑到单级VGA实现30 dB动态范围比较极限,并且要剔除增益误差较大和失真严重的增益区间段,为保证设计裕量,应至少使用两级VGA结构。但级联级数也不易过多,否则会增加电路设计难度,同时带来级间失调等问题,综合考虑本文采用两级级联的吉尔伯特单元的形式。

由于后级ADC精度及动态范围的限制,AGC输出差分信号幅度应到达250~450 mV,同时较大的输出信号幅度也有利于提高峰值检测器的检测精度,然而下混频后的信号幅度(功率)较小,通常VGA的增益的绝对值并不是很大,甚至包含负增益,所以需要一个固定增益级(Fix Gain Amplifier)来抬高AGC的整体增益的绝对值。固定增益级同时也起到一个缓冲器(Buffer)的作用,不论是后级ADC的输入阻抗还是测试时作为AGC负载的电路板走线和测试仪器,它们通常可以等效为一个较大的容性负载,固定增益级的加入使得整个AGC可以适用于不同的负载阻抗而不会影响VGA的频率特性,降低了VGA的设计难度,增强了AGC的可移植性,给其它部分的设计带来了更多裕度。

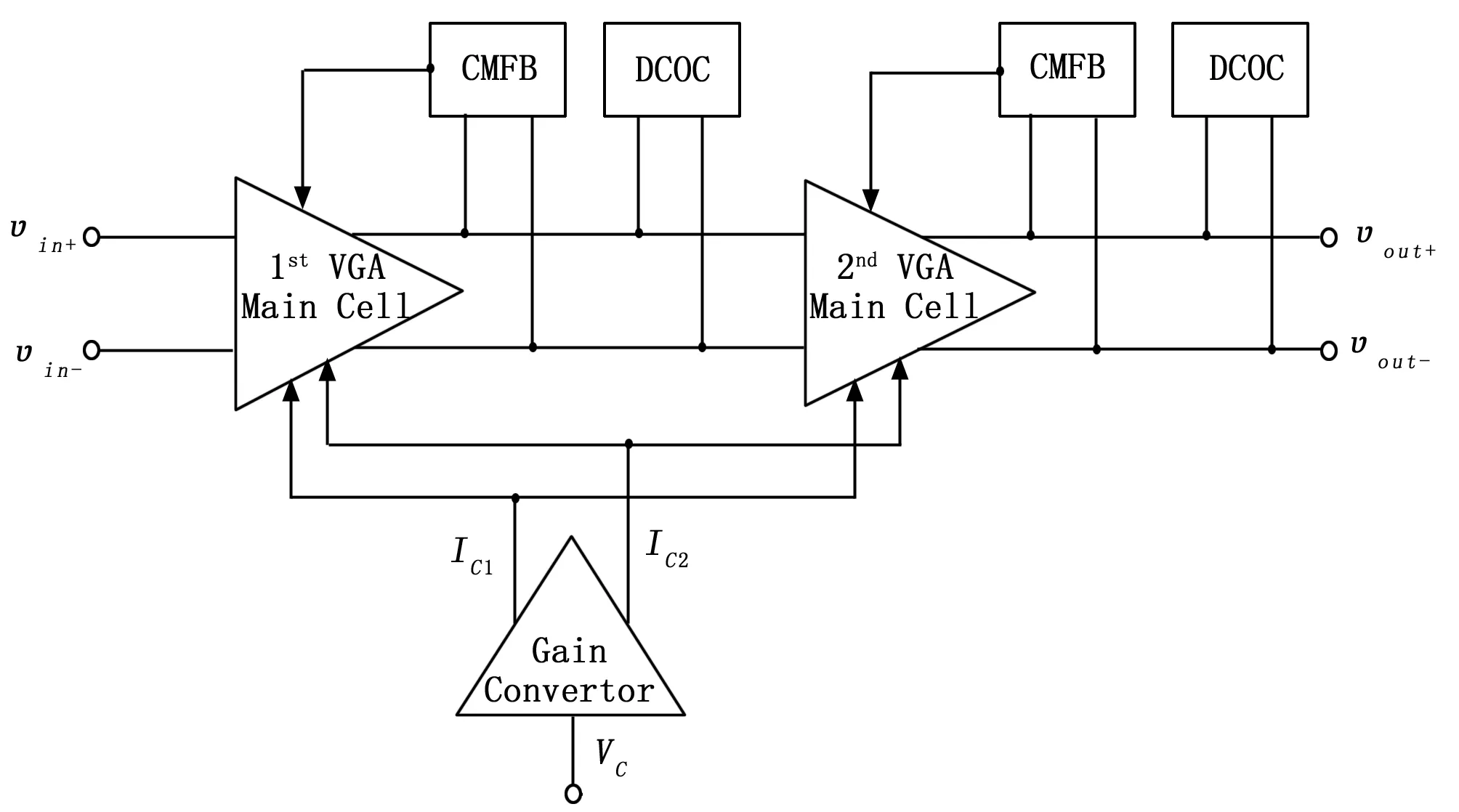

由于输入到输出,信号经过了两级VGA和一个固定增益级,所以级间失调是一个很大的问题,为此本设计将在VGA中加入直流失调消除电路。整个AGC方案如图1所示。

图1 AGC整体结构框图

无线接收机系统对本文所设计的中频AGC系统的性能指标要求如表1所示。

表1 AGC系统性能要求

2 自动增益控制电路基本模块设计

2.1 可变增益放大器(VGA)设计与仿真

两级VGA整体电路框图如图2所示,控制电压CV经增益特性控制电路产生电流IC1和IC2,控制两级VGA的主体增益级,产生dB线性的控制特性,每级VGA包含一个共模负反馈电路和直流消除电路来稳定电路的静态工作点并减小直流失调的影响。

图2 两级VGA电路框图

图3是不同控制电压下两级VGA的幅频特性仿真,由于引入了直流失调消除电路,所以幅频特性整体呈现一个带通的形式,由于米勒效应的影响,不同增益下电路带宽不同,图中曲线从下到上对应的依次为0到1.2 V,从图中可以看出当增益达到最大值时,电路的3 dB带宽最小,最小带宽为21.2~166.0 MHz。

图3 不同控制电压下两级VGA的幅频特性仿真

通常情况下,增益越大电路对失调越敏感,所以在最高增益下,我们对加入失调消除电路前后进行Monte Carlo仿真,如图4所示。设置差分输出端OP和ON的直流电平的差值作为随机变量,统计100次的仿真结果,图中“mu”代表可以随机变量的均值,“sd”表示其标准差,标准差表征了失调电压偏离均值(理论值为0)的程度,即失调的严重程度。

图4 加入DCOC电路前后Monte Carlo仿真

由于VGA的输入输出阻抗和负载(接固定增益级输入管的栅端)均为容性的,所以通常考察的是信号电压的传递情况而不是功率,为了方便仿真和换算,不妨设置一个功率源作为VGA的输入,内阻为差分100欧姆,输出端口设置125 fF的电容负载,去模拟寄生电容的情况,对VGA进行线性度仿真。

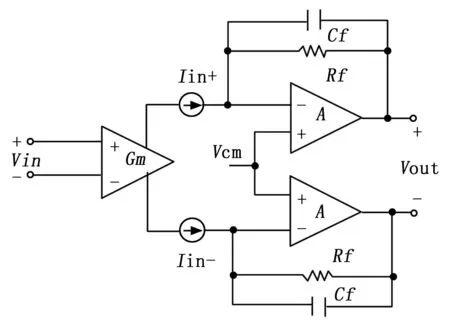

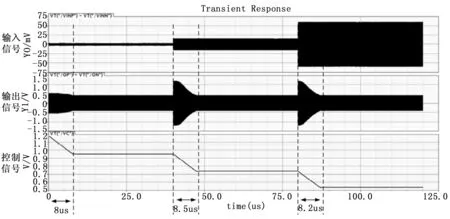

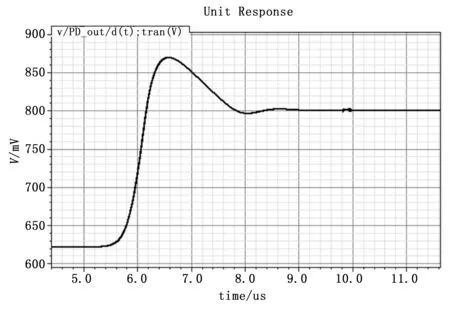

图5给出了电路输入和输出1 dB压缩点随控制电压变化的情况,从图中可以看出两级VGA的dB线性增益范围为-29.5~15 dB,输入P1dB随增益的增大先变好后变差,与上一小节的讨论相符。我们以输入P1dB最好的情况对应的增益为中心,取30 dB的增益范围并保证dB线性良好的区域,即当0.42 继续考察输出P1dB的情况,由于输入和输出阻抗都是容性的,所以输入、输出P1dB的具体数值不具备参考意义,这里我们只关心它的变化情况。我们粗略地认为输出幅度的限制等价于输入幅度的限制乘以其对应的增益,所以输出P1dB随着增益的增加呈现出一种先增加后稳定的情况,我们从输入P1dB的角度确定的增益范围落在了输出P1dB较高的部分,因此从输出P1dB的角度看这个增益范围也是合适的。输出P1dB最差的情况对应的输入P1dB为-16.8 dBm,对应的差分输入幅度为65 mV,此时两级VGA的增益为-15 dB。也就是说在我们所选取的增益区间内,两级VGA增益为-15 dB时,输出P1dB最小。 图5 输入和输出P1dB随增益变化情况仿真 图中最优区域是指在满足dB线性的条件下,选取的线性度最优的30 dB增益动态范围。总结VGA的各项性能指标如表2所示。 表2 VGA性能参数总结 2.2 固定增益级设计与仿真 在线性度不被VGA限制的前提,固定增益级的线性度性能非常重要,对于多级结构的放大器来说,越是后级电路对线性度的要求就越高,输出级只有采用高摆幅的电路结构,才能使得在电源电压的条件下,输出幅度达到450mV也不会发生严重失真。 为保证整个前向通路幅频特性与VGA大致保持一致,固定增益级带宽应高于VGA的带宽,而后级的ADC电路是可以看作一个很大的容性负载,在保证增益的前提下做到100 MHz以上的带宽是不容易的,这需要很小的输出阻抗,很高的摆率和很强的带载能力。为满足以上这些要求,固定增益级采用如图6结构。输入跨导级主要用于为后级电路提供电流,电流流经反馈回路时产生输出电压。在图6中,共模输入视作VCM交流地,第二级运放输入端虚短,则有: VOUT=IIN+·Zf-IIN-·Zf=Gm·VIN·Zf (1) 所以整个固定增益级的增益为: Aυ=Gm·Zf (2) 其中:Gm为输入级等效跨导,它经过了线性化处理,Zf是反馈网络的等效阻抗,所以说该电路线性度是很高的。 图6 固定增益级电路结构 输入跨导级采用全差分结构,能够较好抑制共模噪声,引入了源极负反馈,使得增益是mg的弱函数,提高了线性度,相较于伪差分结构,它噪声性能更好,但牺牲了电压裕度,使得线性度不能无限制提高,同时源极负反馈会降低输入级的增益,这需要仔细地折衷考虑。 电流源作负载的差动对增益较高,要求PMOS负载的饱和电流之和与n型电流源相平衡是不现实的,需要用共模反馈来确定共模电压。在稍后的输出级讨论中可以知道,由于驱动较大容性负载,固定增益级的输出阻抗很小,所以采用电阻分压器提取输出级的输出共模电平,与参考电平比较后生成偏置电压反馈到输入跨导级M3和M4的栅极是合适的,因为电阻分压器的电阻值不需要很大就可以很容易得比输出阻抗大的多,从而避免开环增益的降低,同时避免占据很大面积造成对衬底产生很大寄生电容。 输出级采用电压-电流反馈运算放大器,前馈放大器采用两级结构以获得较高的开环增益,从而使闭环增益稳定,提高了线性度。输出级电路的第二级通过调节适当的偏置使其工作在A类,避免因晶体管的突然截止导致失真,采用推挽式结构以获得较高的输出电压摆幅。 固定增益级的幅频特性中,当差分负载为3 pF(后级ADC所要求的负载)时,直流增益26.12 dB,3 dB带宽可达444 MHz。 2.3 峰值检测器(Peak Detector)设计与仿真 AGC环路也是一种自动控制,这种“自动”有赖于对信号强度的实时检测与判断,有的通过检测信号的包络,有的通过检测信号的功率,检测信号强度的不同方式对应了不同的检测机制。对于GSM信号,它的包络不含调制信息,所以检测信号的包络就能反映信号强度的衰减状况,采用包络检波器是最合适的;但对于CDMA、QAM等幅度调制比较严重的调制方式,它的包络所含的信息很可能会进入环路产生不该有的增益调节,所以均方根检测更加合适。平方律检测器检测的是信号的功率,而对数检测器反映的是输出信号电压的对数。检测方式的选择取决于信号的调制方式和系统的应用环境。 包络检波是最常用的检测方式,当信号瞬时电位增加时,电路正向导通为电容充电,而在电位减小时,电路反向截止,电容无法放电,这样电容上的电压就反映了信号的峰值。一个典型的峰值检测电路如图7所示。 图7 峰值检测电路 3.1 版图设计考量 为保证电路失配、噪声及寄生参数影响等尽可能小,使电路更加可靠,版图设计应注意以下方面。 1)信号线要尽量短,优先选择上层金属以减少寄生电阻的影响,并根据寄生电容的影响来考虑决定金属的宽度。重要的信号线应使用接固定点位的金属进行隔离保护,使噪声的电场线终止于地线而不是信号线。差分信号的走线一定要严格对称,尽量减少走线的拐角。 2)在重要的模块(如VGA输入对管)加入Guard Ring进行保护,以避免噪声干扰。同时大量的衬底接触可以有效防止栓锁效应。 3)差分晶体管应尽可能使用插指、共质心等匹配技术减小器件失配,同时应加入足够的Dummy管,防止刻蚀和离子注入不均匀。 4)直流电压与电流偏置要加足够多的去耦电容,或做成RC低通滤波的形式;电源和地之间,电流镜的共栅点等均应加入足够去耦电容,减小噪声和抖动的影响,遵循的原则是充分利用版图的空隙尽可能多地添加,这也有利于最终密度的填充。 5)电源线要在整个版图中均匀分布并尽量使用顶层较宽的金属,使各模块电路供电均匀,减小电源线上的压降。版图要用金属铺地,缩小版图各点间地的电位差。 6)输入输出信号线应与高速PAD连接以减小PAD上寄生电容的影响。在条件允许的情况下可虑使用多个电源PAD,使供电更均匀并减小bonding线的等效电感(可看作多个电感并联)。 7)在后仿过程中严格对比前仿各个节电的直流电平,保证后仿的静态工作点和版图的差分性能,并据此对版图进行修改。 3.2 AGC 系统仿真 3.2.1 AGC开环特性仿真 当开关S断开时,AGC处于开环状态,人为改变控制电压CV对前向通路的增益和线性度进行仿真,仿真结果如图所示。可以看出AGC的dB线性动态范围是-3.6~41 dB,输入P1dB范围是-36.7~-15.0 dBm,对应差分幅度为6.6~79.5 mV,输出P1dB范围是-26.7~0.68 dBm,对应差分幅度为56.9~1 331.5 mV;满足输出功率压缩1 dB时对应的差分幅度大于450 mV的增益范围是11~41 dB,即该AGC有30 dB的动态范围满足线性度的要求。 一般而言放大器的增益越大直流失调越严重,所以我们对比加入直流失调消除电路前后的前向通路在最高增益处的直流失调的情况。可以看出在未加入直流失调消除电路时,失调已经使电路无法处于正常工作的状态了,而加入DCOC后,该AGC很好的抑制了直流失调的影响,最差情况下的输出失调仅为58 mV。 值得注意的是,仿真中的失调主要来源与固定增益级,对于AGC本身来说,固定增益级已经是整个信号通路的最后一级,本文着重处理了VGA与固定增益级级间的失调,使其不至于造成AGC的输出失真,而固定增益级产生的失调可以交由下级电路进行失调的消除和矫正。由于直流失调消除电路对低频的抑制作用,整个AGC的前向通路呈现带通的特性,当增益最高时,带宽最小为20.8~155 MHz。 3.2.2 AGC闭环特性仿真 将图中的开关S闭合,控制端VC悬空,AGC环路闭合。设置AGC的输入信号0~40 μs时差分幅度为4 mV,40~80 μs差分幅度为16 mV,80~120 μs差分幅度为64 mV,观察AGC的输出和控制信号的变化,如图8所示。 图8 AGC瞬态仿真 从图中可以看出对于不同幅度的输入信号,AGC的输出均能保持在差分幅度420 mV左右,从输入信号发生跳变到输出信号幅度稳定所需的时间大致相同为8 us左右。 为进一步观测AGC的环路特性,设置Vref为从0到800 mV的阶跃信号r(t)=Au(t),观察峰值检测器输出电平d(t)的变化,如图9所示。从阶跃响应中可以看出该系统的阻尼系数是比较合理的,在响应时间和稳定性上做了较好的折衷。 图9 AGC阶跃响应仿真 在无线接收机系统中,自动增益控制电路(AGC)是一个非常重要的部分,它通过检测信号强度自动的调节可变增益放大器(VGA)的增益,从而使输出保持相对恒定,有利于对天线接收到的大动态范围的信号进行处理。本文设计实现了一种适用于70 MHz中频信号的自动增益控制电路,在选定了AGC的具体结构之后,给出了AGC电路的整体设计方案,对电路级设计起宏观指导作用。 根据系统仿真中的系统指标要求逐一对具体的模块电路进行设计,同时对AGC中的各个模块设计做了详细的分析与仿真。从增益、线性度、直流失调、稳定性等方面对电路做了优化。基于电路设计中得到的具体参数完成版图绘制,总结了版图设计中的一些关键点,最后提取版图的寄生参数对AGC电路做了整体仿真,最终该AGC在满足输出信号幅度和线性度的基础上达到了30 dB的动态范围,满足了接收机系统的要求。 [1] 周永强.无线定位系统中自动增益控制电路的设计与研究[J].现代电子技术,2016,39(23):157-160. [2] 曹 煜,唐小宏,李晨雨.基于数模混合技术的高中频快速AGC电路设计[J].微电子学与计算机,2016,33(1):47-51. [3] 周三文,卢满宏,黄建国.放大器饱和对AGC的影响分析[J].计算机测量与控制,2013,21(7):1895-1898. [4] 张良浩,谢红云,赵彦晓,等.采用PIN二极管反馈的射频可变增益放大器[J].电子学报,2016,44(1):206-210. [5] 张 艳,韩 敏.应用于低功耗模拟前端的可变增益放大器[J].电子器件,2016,39(5):1076-1081. [6] 李怀良,庹先国,朱丽丽,等.中低频宽动态范围AGC放大器设计[J].电测与仪表,2013,50(2):96-99. [7] 余国义,张 乐,崔先慧,等.用于CMOS图像传感器的AGC放大器设计[J].中国科技论文,2013,8(1):10-13. [8] 李登科,时永鹏.一种基于TMS320C6414的自动增益控制技术[J].国外电子测量技术,2013,32(1):66-70. [9] 赖小强,李双田.数字闭环自动增益控制系统设计与实现[J].网络新媒体技术,2013,2(3):40-45. Research on Automatic Gain Control Circuit based on CMOS Process Liang Juan (Department of Energy and Electrical Engineering&XinJiang Industrial Vocational and Technical College,Urumqi 830022,China) In the wireless receiver, antenna receiving signal strength tend to vary greatly, automatic gain control loop (Automatic Gain Control, AGC) according to the signal strength to dynamically control the gain of the amplifier, backward level baseband circuit (such as ADC) to provide a constant amplitude signal, the different intensity of signal can be received correctly and demodulation. In order to achieve the dynamic adjustment of the amplifier strength of the signal received by the receiver gain recognition, in order to achieve the output signal amplitude is constant, this paper focuses on the TSMC90nm CMOS process for AGC circuit design process of 70 MHz intermediate frequency signal based on the detailed design of the AGC circuit of each module, and in order to improve the linearity, reduce the DC offset and improve the stability. To optimize the circuit layout design, mainly introduces the AGC chip and the imitation, and gives the characteristics and indexes of AGC system. In the circuit design process, the linearity, the output signal amplitude and the gain control range are improved and optimized. Finally, the performance of the AGC loop is verified by simulation, and the dynamic range of the AGC is achieved on the basis of the output signal amplitude and linearity, which meets the requirements of the 30 dB system. CMOS; AGC; VGA; dB-linear; outputP1dB 2017-03-13; 2017-03-31。 梁 娟(1982-),女,甘肃人,研究生,新疆工业职业技术学院,电气讲师,主要从事电气自动化、电子信息方向的研究。 1671-4598(2017)07-0264-05 10.16526/j.cnki.11-4762/tp.2017.07.066 TM417 A

3 版图设计和系统仿真

4 结论