高速图像模拟源的研究与实现

2017-08-30姚远程秦明伟

唐 瑞,姚远程,秦明伟

(1.西南科技大学信息工程学院,四川 绵阳 621010;2.特殊环境机器人技术四川省重点实验室,四川 绵阳 621010)

高速图像模拟源的研究与实现

唐 瑞1,2,姚远程1,2,秦明伟1,2

(1.西南科技大学信息工程学院,四川 绵阳 621010;2.特殊环境机器人技术四川省重点实验室,四川 绵阳 621010)

针对视觉测量系统的研发与验证问题,设计了一种具有高稳定性、高传输能力、高抗干扰能力的图像模拟源。设计的新型图像模拟源可以根据不同的应用场景输出符合相应要求的图像数据,且用户可以自主选择不同的分辨率与帧率进行图像格式输出。采用PCI Express 3.0总线标准协议,实现了图像数据源从上位机PC到FPGA板间的高速传输。其中,配置参数信息通过直接内存访问(DMA)从模式的寄存器通道下发,大容量图像数据源通过DMA主模式的高速数据通道下发;设计了多个控制器,完成了SDRAM DDR3缓存图像数据的工作,最终输出了符合Camera Link标准协议的图像数据。板级测试表明,上位机与FPGA板间图像数据传输的同步时钟达250 MHz,位宽达256 bit;最终模拟源输出图像数据的同步时钟为80 MHz,帧率达60 fps,且还有很大的提升潜力。图像数据输出满足Camera Link标准,验证了所设计模拟源的正确性,其有助于各种不同的视觉测量系统研发工作,具有广泛的应用价值。

视觉测量; 图像模拟源; FPGA; 上位机; 直接内存访问; 控制器; 相机标准链路

0 引言

随着视觉测量技术在理论与实际应用中的飞速发展,其应用范围已扩展到测量与检验、自动识别、机器人研究与控制等领域[1]。通常情况下,正在研发阶段的视觉测量系统是不会直接连到真实高速图像源进行测试的。这是因为一般高速图像源的分辨率以及帧率是不变的,在图像传输速度上也有固定标准,且高速图像源不能实现每次只传输一帧图像进行验证。针对此问题,研发了一种新的高速图像模拟源,用来模拟真实的图像数据,以测试新的视觉测量系统。

1 高速图像模拟源

基于高速图像模拟源,用户可自定义分辨率以及帧率,产生服从视觉测量系统要求的图像数据源用于测试。用户可以选择已有的图像数据(例如图片)作为数据源发送。视觉测量系统可将最终采集到的图像数据和图像源进行对比,判断是否正确,从而给整个视觉测量系统验证带来很大便利。

该图像模拟源能模拟多种分辨率、帧率,并按照Camera Link标准协议高速输出图像数据,模拟测试多种情况下视觉测量系统的工作状态,从而保证新系统接入真实高速图像源时能够正常、有效、规范地运行。高速图像模拟源可以应用于多个研究领域,其最大的特性就是可以根据不同视觉测量系统的要求来模拟数据源,且图像数据源是确定的。这对整个系统的研制工作具有重大意义。

2 系统设计方案

系统设计方案主要包括以下4个方面。

(1)基于PCI Express 3.0多层协议标准,实现上位机PC与FPGA板卡间的数据通信。图像数据源从PC高速传输至FPGA板卡上缓存,内含直接内存访问(direct memory access,DMA)双通道通信:分辨率、帧率等参数的通过DMA从模式32 bit的寄存器通道下发给FPGA板卡;图像数据通过主模式256 bit数据通道下发,同步时钟达到250 MHz。

(2)研究Camera Link标准,掌握其协议输出数据特点及方式;实现Camera Link数据最终输出标准,输出4组信号,分别为帧有效信号(frame valid,FVAL)、行有效信号(line valid,LVAL)、图像数据(image data,DATA)以及时钟(clock,CLK)信号。其中,图像数据分为Port_A、Port_B、Port_C、Port_D,共4路输出。

(3)研发多个控制器,互相调度,配合使用,完成图像源在FPGA板卡上的缓存并输出符合视觉测量系统要求的图像数据源。主要设计实现包含若干小控制器的两大主控制器:①设计完成的图像数据缓存主控制器,使用SDRAM DDR3高速缓存由上位机传输来的图像数据;②研发的读取数据主控制器,按照用户初始化设置分辨率、帧率图像源格式,以Camera Link标准协议输出。

(4)设计用户控制界面,完成上位机软件部分的开发。系统提供图像分辨率(包含1 728 ppi×2 352 ppi,5 120 ppi×5 120 ppi等格式)、帧率(包含60 fps和80 fps等大小)和图片来源这3个参数,由用户自由配置,通道数固定设置为两通道;同时,用户可选择单幅图像循环或多幅的传输模式,并可选择图像来源。

2.1 PC与FPGA的高速通信

当前,PCI Express是最新一代的总线标准接口。它将全面取代现有的PCI和AGP总线标准,为今后总线技术的发展提供统一标准,PCI Express属于高速串行点对点双通道高带宽传输[2]。每一代的PCI Express都有多种规格(1X、2X、4X、8X、16X),对应不同的通道数。PCI Express最新一代接口是PCI Express 3.0,在最高的16X版本中,其比特率可达到8 GB/s,提高了数据保护性能,改善了数据传输效率,能至少满足将来一段时间内各种高速设备的要求。

2.1.1 PCI Express LogiCore的生成调用

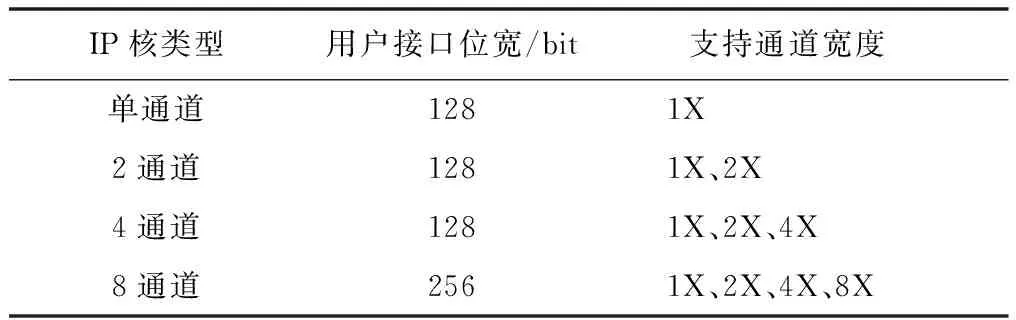

Xilinx公司为其FPGA提供了一种可以生成PCI Express IP内嵌硬核的解决方案。Virtex-7系列FPGA的PCI Express IP核实现了PCI Express 3.0协议,并向下兼容。该IP核配置不同时,IP核与用户接口位宽、所支持的通道宽度之间的关系如表1所示。其中,IP核速率均为2.5 Gb/s或5.0 Gb/s。

表1 IP核类型与用户接口位宽、支持通道宽度的关系

PCI Express 3.0 IP核使用Packet(数据包)在各模块间进行通信。数据发送要相应经过物理层、数据链路层、事务层,且通过每一层都要打包,并添加必要的数据信息(如验证信息)[3]。在接收端,每一层的接收模块都会对接收到的数据包进行解析,去除在对应层上添加的信息,然后发往下一层。这样,设计者就可以在接收端的事务层看到发送端事务层的有效数据。此设计采用的软件是Vivado 2016.3,芯片为Virtex7系列的XC7V690T,封装型号为fft1761,速度等级选为-2。配置PCI Express IP Core完成后,生成Integrated Block for PCI-Express模块。该模块完全符合PCI Express的分层结构,分为物理层,链路层和事务层。

该IP核模块包括物理接口(PL)、事务接口(TRN)、配置接口(CFG)、外部传输接口(PCI EXP)和系统接口(SYS)。该模块遵循PCI Express 3.0多层协议标准,完成了物理层、数据链路层和部分数据层的通信功能。用户在使用时该IP核时主要的注意事项是:按照PCI Express协议,设计好各控制和状态端口的电平。

PCI Express 3.0总线有2种总线读写方式,可编程的输入/输出(programmed input/output,PIO)方式读写由软件对寄存器进行直接寻址来完成,这种操作消耗CPU资源。若使用PIO方式进行大容量的数据读写操作,需要CPU频繁发起读写请求,使CPU的资源占有率非常高。因此,PIO操作不适用于大数据量的高速板间通信。通常采用PIO方式,对FPGA的寄存器进行读写控制以及参数配置。

DMA是一种高速的数据传输方式,主要用于大数据量、成批交换数据的高速场合。在该模式下,CPU只需向DMA授权,然后由DMA控制器负责发起数据传输。一般情况下,数据传输完成后,通过中断信息反馈到CPU,这样在整个数据传输的过程中并不需要CPU参与。与PIO方式相比,DMA大大减轻了CPU资源占用率。

2.1.2 DMA Engine设计

DMA Engine设计需要解决2个关键问题:①完全、准确接收任何高速设备输出的数据;②减少整个高速系统传输过程中对CPU的干扰。针对这2个问题,在接口处设计了FIFO作为缓存,以避免数据的丢失。在进行DMA传输时,应尽量使数据量大一些,减少中断产生的次数[4]。在FPGA中,DMA引擎与PCIeIPCore、Tx Engine、RxEngine配合完成数据DMA模式的传输。

PCI Express系统逻辑整体设计框图如图1所示。下面将研究DMA Engine的实现过程。

图1 PCI Express系统逻辑整体设计框图

在PCI Express接口设计中,DMA Engine起到主控作用,在模块中主要包含2个方面:①DMA控制的相关寄存器的定义;②DMA相关操作的控制中心。

DMA的相关寄存器,承担着FPGA板卡和计算机之间的信息交互功能。本文将DMA寄存器映射到BAR1空间中。而BAR0空间用来定义PCI Express总线域地址,根复合体 Root Complex负责处理内存地址到PCI Express总线地址之间的转换。计算机需要操作BAR0空间的数据时,可以通过操作BAR0空间对应内存地址中的数据;设计中涉及的调试模式识别结果也是通过写BAR0空间的寄存器进行传递的。只要系统启动,BIOS就会监测设备所连的外设,而且按照配置空间头中BAR空间的大小分配地址空间[5]。

本文中FPGA板卡使用Bus Master DMA的方式完成数据的交互[6]。DMA传输启动前,需要对BAR1中的DMA相关寄存器进行配置,例如软件复位、使能DMA中断相关位、确定DMA传输的地址和数据量大小[7];然后可以启动DMA,当要求的数据量发送完毕后,DMA中断发生,进入中断处理程序,转存接收的数据,DMA传输任务完成。

2.1.3 上位机软件研发

系统软件架构主要包括用户交互界面、后台存储、后台算法以及PCI Express驱动4个模块内容。每个模块具体完成的任务如下。

①用户交互界面:为用户提供一个可视化窗口和交互的平台,可显示户参数配置及当前频环境信息、历史数据等信息。

②后台算法:包括前文中改进的频谱分配和频谱决策算法,是优化决策的核心部分。

③后台存储:包括通信数据存储、决策案例存储、用户行为等各类数据存储。决策成功的案例会存入历史记录表中,供后续决策过程参考[8]。

④PCI Express总线驱动:驱动PCI Express总线,使其PC端可使用,并按系统要求工作。

2.2 FPGA主板控制模块设计

2.2.1 DDR3图像数据缓存研究与实现

使用DDR3,将由上位机传输来的图像数据全部缓存。由于DDR3的控制逻辑复杂,为了缩短工程人员的开发周期,开发人员只需要通过IP核选择内存芯片,并设置控制器的相关参数,便可自动生成设计所需的RTL文件、用户约束文件以及网表文件[9]。用户通过更改一些接口,即可生成测试工程,并进行DDR3读写测试,设计将控制器的系统时钟设置为800 MHz。

控制器由系统时钟和复位模块、用户接口模块、MIG IP核生成的控制器接口模块组成。用户接口是用户控制DDR3的直接操作端口,需由用户根据工程的数据量大小、数据位宽、数据速率、缓存深度等参数自行设计。用户接口设计包括写数据、读数据以及核控制模块。考虑到DDR3只包含一套地址结构,因此读、写不能同时进行。用户接口框图如图2所示。

图2 用户接口框图

本设计采用读写数据通道分开的设计思想,对DDR3进行时分操作。根据工程中数据量的大小和DDR3的容量大小计算读写的时间,并按照这个时间产生外部切换信号,由外部切换信号来控制DDR3的读写;根据切换信号,分别将读写的命令、地址和数据发送给控制模块;在控制模块内部通过FIFO缓存的方式完成数据的跨时钟域处理,确保数据的完整性,以避免亚稳态的产生[10]。

2.2.2 图像读取控制器设计

数据由上位机传输到FPGA板卡中的DDR3缓存之后,由图像读取控制器按照用户初始化设置以及Camera Link协议稳定读出,再按要求输出,完成设计要求。

本课题中,图像读取控制器设计包含2个内核:分频器与异步FIFO。分频器产生模拟图像源80 MHz同步时钟,可以从PCI Express或者DDR3的用户时钟分频得到。异步FIFO完成时钟域的转换,从FIFO输入端的200 MHz时钟域转换至FIFO输入端的80 MHz时钟域,且异步FIFO还能起到临时缓存图像数据的作用。

例如模拟输出分辨率为(1 728×2 352)ppi的图像源,控制器最终输出的是FVAL、LVAL、DATA以及CLK(80 MHz)这4组信号,这满足Camera link接口协议;图像帧率满足60 fps,有严格的等待时间控制器,保证了相机帧率。

3 系统测试与分析

3.1 硬件测试

在整个系统设计完成之后,需要对系统进行下板实际测试,确保图像模拟源能高速、稳定、有效地工作。连接Xilinx’s Virtex-7 XC7V690T FPGA板卡,在Vivado 2016.3平台进行实际测试。测试内容如下:①基于PCI Express 3.0多层协议标准,测试上位机与FPGA板间通信情况,包括下发的数据测试和数据有效信号测试;②测试DDR3是否正确缓存数据,以及读出数据控制器是否正常读出数据;③测试模拟源Camera Link最终输出标准,是否有效输出FVAL、LVAL、DATA以及CLK信号这4组信号。

3.2 结果分析

本设计采用PCI Express 3.0 支持8X通道,用户下传数据端口dma_rd_data位宽256 bit,同步时钟250 MHz,下传数据有效信号dma_rd_valid。为方便测试,模拟源测试数据发送为从0累加、位宽为32 bit的叠加数据。数据从上位机下发至FPGA板卡,经过多个控制器互相配合,使图像数据缓存在DDR3中,然后进入异步FIFO,最终按照Camera Link标准协议输出。运行系统后,由上位机软件触发开始模拟图像源,Vivado提供了FPGA片上调试工具ILA,可以捕获和显示实时传输信号。

由实际测试结果可知,从上位机下传的数据信号dma_ra_data确实是从0累加的位宽为32 bit的数据,dma_ra_data位宽是256 bit,一次时钟包含8个测试数据;dma_rd_valid在dma_ra_data有数据下传时是高位,其余时间为低位,为正确的下传数据有效信号。数据经过DDR3缓存进入异步FIFO待控制器读出,最终的模拟源标准输出数据从起始位00 000 000依次累加,而32 bit的输出数据data又按照4路输出分为Port_A、Port_B、Port_C、Port_D。每个数据口输出8 bit数据,Port_A为高8 bit,Port_D为低8 bit。从异步FIFO读出的数据是64 bit位宽,按照逻辑控制器分为两次输出,从而完成图像源单次32 bit输出。

FVAL在一帧图像数据传输中一直为高,LVAL对应每一行的图像数据有效位。当输出分辨率为(1 728×2 352)ppi时,图像数据一共1 728行。进行每一行传输时,LVAL有效;在行与行的间隙时,LVAL无效,证明没有传输有效图像数据,但此时FVAL信号依旧有效,因为一直是在一帧图像传输期间。只有在FVAL与LVAL同时有效时,数据信号才是有效的图像数据。图像源输出同步时钟80 MHz,帧率为60 fps。经分析,输出信号完全满足Camera Link标准协议,证明此高速模拟源功能测试正常。

4 结束语

基于PCI Express 3.0多层协议标准,完成了上位机PC与FPGA板间数据通信,设计了多个控制器,实现了图像源在FPGA板卡上的缓存以及符合Camera Link标准协议的图像数据输出。通过Virtex-7 XC7V690T板级测试,证明了该图像模拟源能高速、稳定、有效地工作,能输出满足协议标准的图像数据,数据同步时钟为80 MHz,帧率达到60 fps。此高速图像模拟源适用于视觉测量系统的研发,输出的是确定图像源,降低了外界干扰,提高了成本效益,能更方便地测试采集到的图像数据是否正确。

[1] 申春龙,余乐,张红彬,等.基于PCI总线的瞬态延迟脉冲发生器[J].自动化仪表,2017,38(3):55-57.

[2] 严振杰,俞磊,周鹏成. AP1000无线通信系统电磁兼容性试验设计[J].自动化仪表,2017,38(2):82-85.

[3] 董旭明,李志斌.计算机视觉在并联机器人运动学标定中的应用[J].自动化仪表,2016,37(5):16-19.

[4] 王学东.基于PCI-E总线的高速数据传输与存储的系统设计[D].北京:北京邮电大学,2015.

[5] 付慧琳,刘芳,邓友燕.C++与Matlab混合编程模式的研究与实现[J].电子科技,2015,27(11):73-75.

[6] 王聪,王彬,薛洁,等.基于PCIe总线协议的设备驱动开发[J].信息技术,2015,22(3):32-35.

[7] 李晃.高速数据传输测试系统的设计与研究[D].西安:西安电子科技大学,2015.

[8] ORLIC V,DUKIC M.Algorithm for automatic modulation classificationin multipath channel based on sixth-order cumulants[J]. TELSIKS,2014,13(12):423-426.

[9] AVCI E,AVCI D.The performance comparison of discrete wavelet neura lnetwork and idscrete waveleta daptive net work based fuzzy inference system for digital modulation recognition[J].Expert Systems with Applications,2008,35(1-2):90-101.

[10]朱伟杰.基于FPGA的高速数据传输平台构建——应用于WiGig芯片测试系统[D].成都:电子科技大学,2014.

Research and Implementation of High-Speed Image Simulation Resource

TANG Rui1,2,YAO Yuancheng1,2,QIN Mingwei1,2

(1.School of Information Engineering,Southwest University of Science and Technology,Mianyang 621010,China;2.Robot Technology Used for Special Environment Key Laboratory,Mianyang 621010,China)

Aming at the probelm of the development and verification of vision measurement system,an image simulation resource with high stability,high transmission capacity and high anti-interference capability has been designed. According to different application scenarios,the image simulation resource output simage data that meet the corresponding requirements,and the user can choose the image format such as resolution and frame rate for output.The PCI Express 3.0 bus standard protocol is used to realize the high-speed transmission of image source from PC to FPGA. The configuration parameters are transmitted through register channel of direct memory access(DMA) slave mode,and the large capacity image data source is transmitted through the high-speed data channel of DMA master mode. Multiple controllers are designed to complete the cache of image data in SDRAM DDR3,and output image data in accordance with Camera Link protocol standard. The result of FPGA board-level test shows that the synchronization clock for image data transmission between PC and FPGA reaches 250 MHz,the bit width is 256 bit,the synchronization clock for image simulation resource output is 80 MHz,the frame rate is up to 60 fps,and there is still potential for improvement as well.The data format meets the standard of Camera Link and this proves the correctness of this image simulation resource,which will contribute to the development of a variety of visual measurement systems with extensive applicationvalue.

Vision measurement; Image simulation resource; FPGA; Host computer; Direct memory access(DMA); Controller; Camera standard link

国家重大科学仪器设备开发项目(2016YFF0104003)

唐瑞(1994—),男,在读硕士研究生,主要从事FPGA高速并行信号处理方向的研究。E-mail:tangrui_w@foxmail.com。 姚远程(通信作者),男,学士,教授,主要从事雷达无线电方向的研究。E-mail:yaoyuancheng@swust.edu.cn。

TH7;TP332

A

10.16086/j.cnki.issn1000-0380.201708010

修改稿收到日期:2017-06-25