基于AD5724的数模转换电路设计

2017-08-21张儒

张儒

【摘 要】数模转换电路在仪器信号模拟中起重要的作用,本文介绍了DAC芯片AD5724的工作原理以及工作方式设置,并在此基础上阐述了基于AD5724和FPGA的测井仪器信号模拟的实现方法,同时给出了硬件电路的电路图。通过多次试验,表明该电路工作稳定可靠,取得了良好效果。

【关键词】AD5724;数模转换;FPGA

【Abstract】DAC circuit plays an important role in the signal simulation, this paper introduces the setting of working principle of the DAC chip AD5724 and the way of work, and on the basis of the implementation method of logging signal AD5724 and FPGA based on the simulation,and gives the circuit diagram of the hardware circuit.Through many tests,it is proved that the circuit is stable and reliable,and has achieved good results.

【Key words】AD5724;DAC;FPGA

0 引言

测井系统信号模拟装置,用来产生各类的测井仪器信号。国内的测井仪器快速发展,在初始研发的过程中,没有考虑到测井仪器自检问题。在测井时,由于各种因素的影响,仪器可能发生损坏。在地面系统和仪器无法建立通讯时,所以无法预知地面系统是否正常工作。出现问题后,严重影响测井作业。鉴于此,测井系统信号模拟装置的研究具有现实意义。通过模拟井下仪器,与地面系统建立通讯。测试地面系统时,只需和模拟装置相连接,而不必再连接仪器串,可以方便地面系统的维修和调试。

仪器信号主要分为模拟类仪器和数字类仪器,本文主要介绍模拟类仪器信号。本文采用FPGA和DAC配合的方式,产生模拟类仪器信号AC-CCL、MMD、TENSION、SP。对于DAC的选择,主要考虑以下几方面的因素:转换精度,转换时间,器件价格,功耗等。由于设计的系统对于精度,速度的要求比较高,所以在设计中D/A芯片采用美国 Analog 公司的AD5724。AD5724为四通道、12位、串行输入、单极性/双极性、电压输出型DAC。

1 AD5724介绍

AD5724是四通道、12位、串行输入、电压输出数模转换器,采用+4.5V至+16.5V单电源或±4.5V至±16.5V双电源供电。标称满量程输出范围可通过软件选择,选项有+5V、+10V、+10.8V、±5V、±10V和±10.8V。同时还内置输出放大器、基准电压缓冲器以及专有上电/省电控制电路。这些器件可保证单调性,最大积分非线性(INL)误差为±16LSB,噪声很低,最大建立时间为10μs。AD5724采用串行接口,能够以最高30 MHz的时钟速率工作,并且与微控制器接口标准兼容。利用双缓冲,所有DAC可实现同时更新。对于单极性输出,输入编码方式为标准二进制。利用异步清零功能,可将所有DAC寄存器清零至用户可选的零电平或中量程输出。器件均采用24引脚TSSOP封装,额定温度范围为-40°C至+85°C工业温度范围。

AD5724内置一个上电复位电路,确保DAC寄存器上电成功。上电时,输出通过一个低阻抗电路被拉低到0V。DAC架构由一个电阻串DAC和一个输出放大器构成。基准电压输入先缓冲起来,然后再施加于DAC。电阻串是一串电阻,各电阻的值为R。载入DAC寄存器的编码决定抽取电阻串上哪一个节点的电压,以馈入输出放大器。抽取电压的方法是将连接电阻串与放大器的开关之一闭合。由于是一串电阻,因此可以保证单调性。

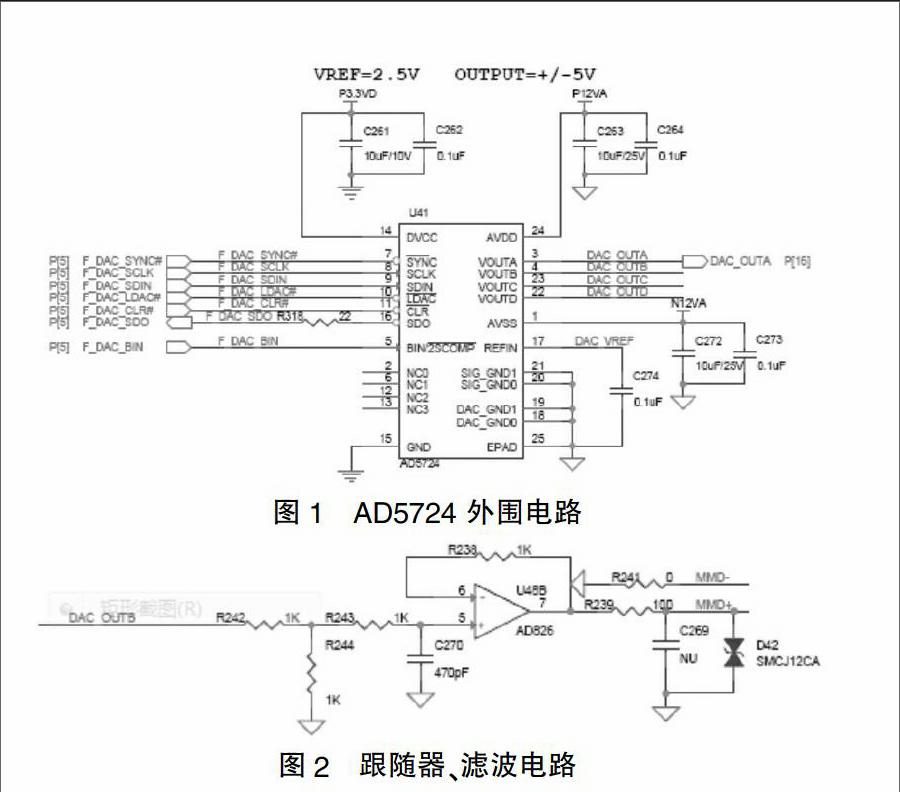

2 AD5724外围电路

AD5724的参考电压为2.5V由电压芯片AD780产生。AD780是一种超高精度带隙基准电压源,利用5.0V输入提供2.5V输出。它具有低初始误差、低温度漂移和低输出噪声特性,并能驱动任意大小的电容,因此AD780非常适合用于增强高分辨率DAC的性能。AD5724的输出为±5V。图1是AD5724的外围电路。

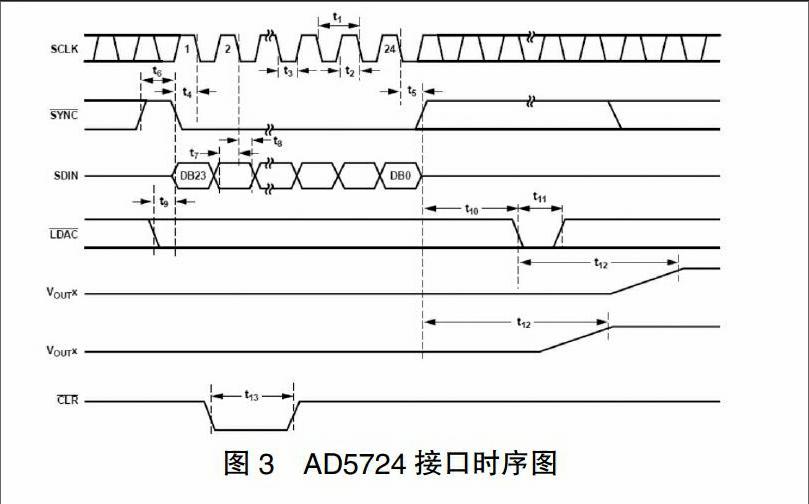

AD5724输出四路信号AC-CCL、MMD、TENSION、SP。输出信号经过跟随器驱动输出,中间加入滤波和分压电阻方便调试使用,见图2。

图1 AD5724 外围电路

图2 跟随器、滤波电路

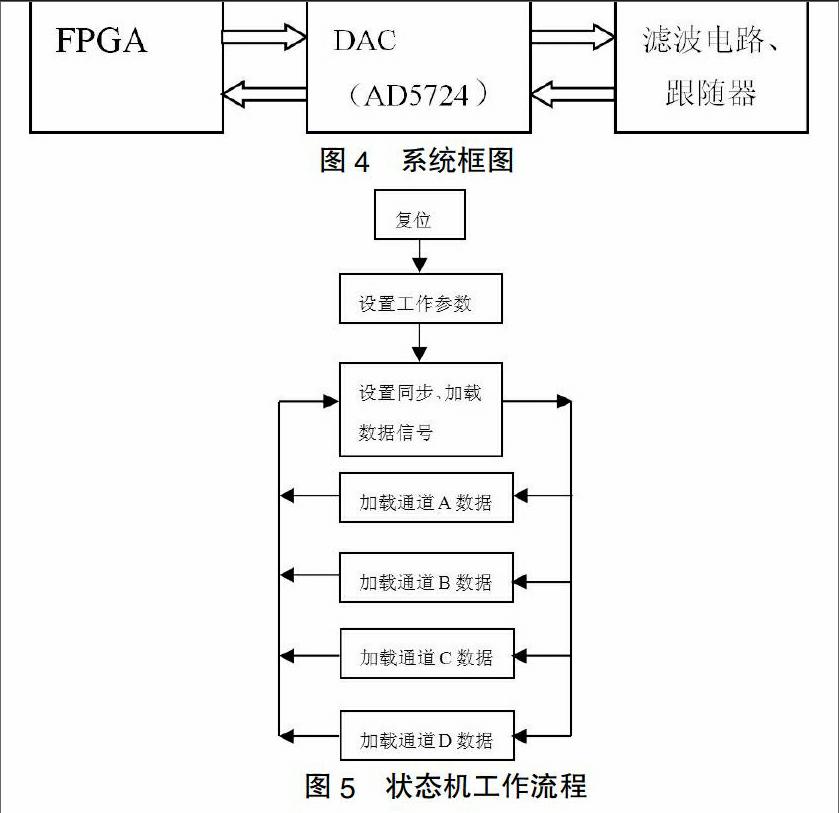

3 AD5724逻辑时序控制

AD5724接口时序如图3所示。SCLK是串行时钟输入。数据SDIN在SCLK的下降沿逐个输入移位寄存器。工作时钟速率最高达30MHz。SYNC低电平输入有效。这是串行接口的帧同步信号。当SYNC处于低电平时,数据在SCLK下降沿传输。数据在SYNC的上升沿锁存。SDIN为串行数据输入,数据必须在SCLK的下降沿有效。LDAC为加载DAC逻辑输入,用于更新DAC寄存器和模拟输出。当永久接为低电平时,在SYNC的上升沿更新所寻址的DAC寄存器。如果LDAC在写入周期保持高电平,DAC输入寄存器会更新,但输出直到LDAC的下降沿才会更新输出。在此模式下,所有模拟输出都可以在LDAC的下降沿同时更新。LDAC引脚不能悬空。Vout输出DAC转换后的模拟信号。

图3 AD5724接口时序图

4 DAC软件设计

在仪器信号模拟中,實现高精度的数据模拟过程,需要用FPGA的使序控制来配合AD5724工作。整个系统的系统框图如图4所示。

图4 系统框图

图5 状态机工作流程

AD5724的采样逻辑时序由FPGA控制,AD5724工作的同步信号SYNC、加载信号LDAC、时钟信号SCLK、数据信号SDIN、清零信号CLR均由FPGA设置。FPGA中,利用状态机设置控制信号。具体控制流程见图5。复位完成后,设置AD5724的输出极性、输出范围、通道数等工作参数,写入到各控制寄存器;然后4个通道轮流加载数据,写入到控制寄存器,依次循环。本设计中,FPGA采用ALTERA的Cyclone?誖III FPGA系列,最大可用IO个数为182个,拥有10320个逻辑单元。控制DA芯片输出四路信号;DAC控制模块,用于控制DAC输出4路模拟信号;A通道输出ACC-CL信号,B通道输出MMD信号,C通道输出TENSION信号,D通道输出SP电平。

5 结论

本系统基于FPGA和DAC,产生模拟类仪器信号。本系统与测井地面系统连接,通过地面系统的软件界面,可以检测通讯状态。通过实践证明,本系统为地面系统的测试和检修提供了有效且可靠的手段。

AD5724能够满足应用的要求,还提供了多个通道的模拟信号,减少器件的数量,大大提高了系统设计的灵活性,多种工作方式可以满足不同应用的 需求。通过多次测试表明,本系统可以在测井仪器测试中稳定应用,并且达到了现场的测试要求。

【参考文献】

[1]夏宇闻.Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2003(7):125-136

[2]王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2005(9):218-245.

[3]Analog公司.AD5724数据手册,2007.

[责任编辑:田吉捷]