基于FPGA边缘检测算法的设计

2017-08-08金大超冷建伟

金大超,冷建伟

(天津理工大学 自动化学院,天津 300384)

基于FPGA边缘检测算法的设计

金大超,冷建伟

(天津理工大学 自动化学院,天津 300384)

在现场可编程门阵快速发展的背景下,列针对目前的数字图像处理的数据处理量大和处理速度慢等问题,提出了一种基于FPGA的实时图像边缘检测算法的实现方案,对sobel边缘检测在modelsim和FPGA硬件平台上进行了综合的仿真与验证,获得了相对较好的边缘检测效果,能够为以后实时监控系统中的减少数据处理量和提高处理速度提供保障。

sobel;实时图像;边缘检测;FPGA

边缘检测是图像处理、计算机视觉中的重要内容和基础,在卫星和军事领域中的图像监控、识别跟踪的重要前提环节,是图像识别和跟踪的重要依据,在一些重要的领域,传统的软件实现方法速度较慢,丢帧现象普遍,很难满足速度、精度的要求[1-2]。现场可编程门阵列(FPGA)由于其开发周期短、并行运算的处理能力,在图像处理领域得到了快速发展[3],通过FPGA的硬件逻辑电路对实时图像的预处理可以以及图像处理中的并行优势提高图像处理的速度,满足系对图像和数据处理的实时要求。

1 sobel边缘检测算法

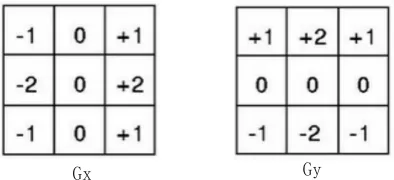

边缘检测实现的基本原理就是检测图像的特征发生变化的位置所在,通常图像的边缘类型有很多种,常见的可以概括为以下的三种基本类型:第一种就是图像的阶梯型的边缘,图像的灰度值从低跳跃到高;第二种是图像的屋顶型的边缘,其图像的灰度值从低逐渐变化到高,后在渐渐的减小;第三种是图像的线性的边缘,其图像具有脉冲跳跃的灰度变化。这三种边缘信息都有一个边缘灰度值变化的共同特点。索贝尔算子(sobel operator)主要被我们用于边缘检测算法实现上,它属于一种离散性的差分算子,通过sobel算子,可以计算出图像亮度函数的灰度近似值,然后通过灰度值的变化来检测到图像的边缘位置。由于对噪声的平滑处理作用,能够为图像处理提供相对比较准确的边缘信息[4]。在对图像进行边缘检测是过程中,通过对图像上的每一个像素点逐一的进行sobel算子,都会生成相对应的灰度矢量和法矢量。Sobel边缘检测算子在运算上通常要使用两个算子,包括水平算子和垂直算子在内的两个方向上的算子,如图1所示。

这两个方向算子由两组3X3的矩阵组成,包括横向和纵向,然后将两个方向算子分别同平面像素做卷积,进而可以得到我们所需要的横向和纵向的亮度差分近似值。

图1 索贝尔算子

2 图像处理中FPGA的优势

图像处理中的数据具有数据量大、要求速度高的一些基本特点,日常生活中的常规软件系统在速度和数据量方面越发显得吃力,而FPGA(Field Programmable Gate Array)即现场可编程门阵列,具有硬件并行处理能力和可执行流水任务方面的优势,对速度的要求完全能够满足,能够达到几百兆赫兹的时钟速度,适用于图像处理领域,能够精确快速的完成图像处理任务[5-8]。

流水任务中每一个大的任务都会按照时序会被分割成几个复杂程度相对的子任务,每一个子任务在流水线上的不同位置会被同时进行执行,这样系统的整个任务的处理速度就会获得很大的提升,从而减少数据操作等待的时间,所以可以在很大程度上提高系统资源的使用率[9-12]。

3 sobel边缘检测的VHDL的实现

3.1 sobel边缘检测的设计流程

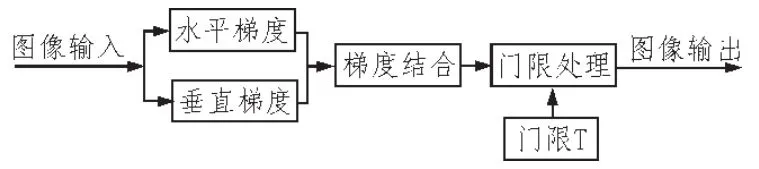

Sobel边缘检测算子使用垂直算子和水平算子[7],原理是分别用这两个方向算子对图像进行卷积运算,得到两个矩阵,再求这两个矩阵对应位置的两个数的均方跟,得到的矩阵就是灰度图像矩阵中各个像素点的梯度值[13-15],然后根据我们输入的门限值进行对比,当得到的梯度值大于输入的门限值时,则规定该点的灰度值为255,反之则为0,sobel边缘检测框图如图2所示。

图2 sobel算子边缘检测框图

3.2 sobel边缘检测中3X3矩阵的产生

像素阵列的HDL实现:由于水平算子和垂直算子,我们实现卷积首先要实现3X3的像素阵列,通常应用3种方法实现:RAM存储、FIFO存储、Shift_RAM存储。这里我们应用3个Shift_RAM的移位存储来实现3X3像素阵列。调用Shift_RAM的宏定义模块,其原理图如图3所示。

图3 Shift_RAM的原理图

这里我们定义8Bit,640个数据每行,同时寄存两行,选择时钟使能端口clken,通过以下方法实现8Bit宽度的3X3像素阵列功能:首先,应该将输入信号通过像素使能时钟打一拍,以便同步,这样才能保证数据与Shift_RAM输出的数据保持同步。接着,例化并输入所需的三行数据,在经过Shift_RAM移位存储后,这样就得到了row0_data、row1_data、row2_data的数据用于实现矩阵。

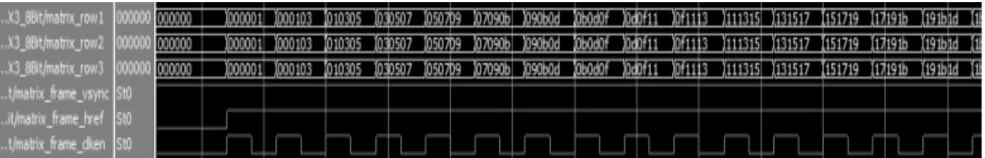

由于从Shift_RAM存储的过程中消耗了一个时钟周期,所以应该将3X3读取使能时钟进行一个clock时钟的偏移,此时根据read_frame_href与read_frame_clken信号,直接读取3X3像素阵列。得到的3X3像素阵列的modelsim仿真如图4所示。

图4 3X3像素阵列

由于Shift_RAM存储过程与3X3阵列的生成个消耗一个时钟,我们需要将行场信号、像素使能读取信号移动2个clock时钟,这样就使行场、使能与数据时钟保持一致,仿真如图5所示。

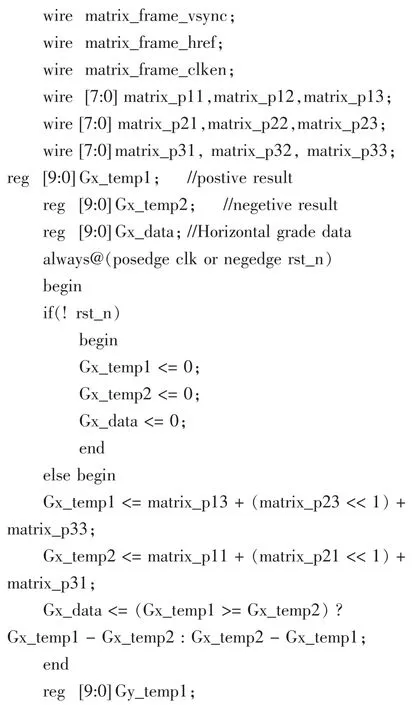

3.3 sobel算法的HDL实现

为了实现FPGA的加速运算功能,发挥其并行流水运算的优势,将sobel边缘检测算法实现具体可以分为如下几个步骤:1)计算Gx与Gy与模板每行的乘积。2)求得3X3模板运算后的Gx与Gy,然后求得Gx2+Gy2的平方根(通过调用Altera下的LPM中的平方根IP核实现)。3)根据与外部输入的阈值大小比较,实现边缘检测。最后边缘检测的modelsim仿真图如图6所示。

图5 行场、使能与数据时序的一致

图6 边缘检测的modelsim仿真

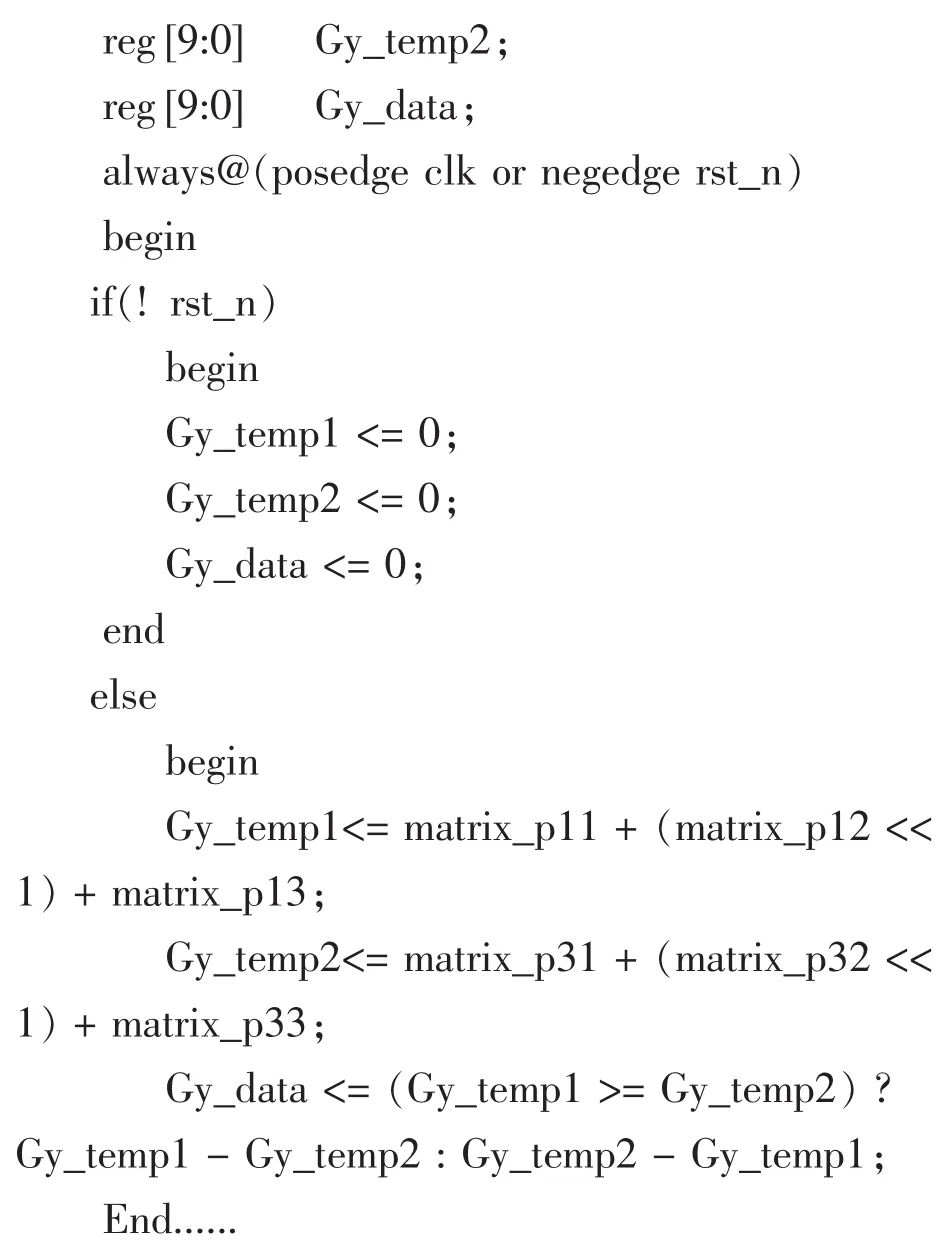

3.4 边缘检测算法的部分代码展示

4 板级测试

完成了边缘检测模块的HDL实现之后,将算法下载到FPGA中,在Altera cyclone IV板级平台上测试,得到实验数据经过逻辑分析仪,经过Matlab的转换,得到的实验结果如图7,从modelsim仿真结果和板级实验得到的图像分析,验证了使用FPGA能够比较顺利的完成图像处理中的边缘检测任务。

图7 边缘检测实验效果图

5 结 论

针对目前在数字图像处理领域的速度不足等诸多问题,提出一种使用硬件逻辑电路(FPGA)芯片实现Sobel边缘检测具有重要的使用价值。由于现场可编程门阵列在数据并行结构和流水线结构中具有其自身的优势,通过FPGA的特点,我们将算法的并行性进行了实现,可以大幅提高Sobel边缘检测速度。通过在FPGA的平台上的验证,FPGA的流水线和并行结构,可以使图像处理中的大数据重复性操作,速度要求高等方面提高效率,可以达到实时要求,而且占用片上资源较少,在FPGA平台上较好的实现了边缘检测算法。

[1]杨新华,寇为刚.基于FPGA的Sobel算子图像边缘检测算法 [J].仪表技术与传感器,2013,31(1):24-30.

[2]黄智伟.王彦.FPGA系统设计与实践[M].北京:电子工业出版社,2005.

[3]Cotte R I,Justes D R,Nanita S C,et al.Analysis of gaseous toxic industrial compounds and chemical warfare agent stimulants by atmospheric pressure ionization mass spectrometry [J]. Analyst,2006,131(4):579-589.

[4]TSAI M Y,YOST M G,WU C F.Line profile reconstruction:validation and comparison of reconstruction methods [J]. Atmos Environ,2001,35:4791-4799.

[5]杜文萍,王静宇,蒋立军,等.带通采样在高分辨率图像声呐中的应用 [J].计算机工程与应用,2008(12):228-231.

[6]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[7]端瑞玲,李庆祥,李玉和.图像边缘检测方法研究综述[J].光学技术,2005,31(3):415-419.

[8]艾扬利,杨兵.基于FPGA的sobel算子并行计算研究[J].现代电子技术,2005,28(9):50-51.

[9]李明,赵勋杰,毛伟民.Sobel边缘检测的FPGA实现[J].现代电子技术,2009(16):23-30.

[10]官鑫,王黎,高晓蓉,王泽勇.图像边缘检测Sobel算法的FPGA仿真与实现[J].现代电子技术,2009(8):28-40.

[11]陈辉.图像边缘检测技术的研究[D].哈尔滨:哈尔滨工程大学,2012.

[12]陈珂.基于典型边缘检测算法的数字图像处理系统的模块电路设计与FPGA实现[D].北京:北京交通大学,2012.

[13]邓蕊.植物根系图像的边缘检测方法的研究与实现[D].重庆:重庆大学,2015.

[14]张皓.基于FPGA的图像处理加速器研究[D].武汉:武汉工程大学,2015.

[15]陈士豪.基于图像处理技术分析的织物疵点检测系统设计[D].西安:西安工程大学,2015.

Design of edge detection algorithm based on FPGA

JIN Da-chao,LENG Jian-wei

(Tianjin University of Technology Institute of Automation,Tianjin 300384,China)

In the field can be programmed gate array of rapid development under the background,in view of the current digital image processing of data processing Liang Dahe processing speed is slow problem,and put forward a realization scheme based on FPGA real time image edge detection algorithm,the Sobel edge detection in Modelsim and FPGA hardware platform of the integrated simulation and verification,relatively good edge detection effect,for real-time monitoring system to reduce the amount of data processing and improve the processing speed to provide protection.

sobel;real time image;edge detection;FPGA

TN492

:A

:1674-6236(2017)13-0159-04

2016-06-27稿件编号:201606208

金大超(1990—),男,河北唐山人,硕士。研究方向:基于FPGA的图像采集与处理。