一种基于椭圆拟合的三相电压不平衡条件下的锁相环

2017-08-08史旺旺严建鹏

史旺旺,严建鹏

(扬州大学水利与能源动力工程学院,扬州225009)

一种基于椭圆拟合的三相电压不平衡条件下的锁相环

史旺旺,严建鹏

(扬州大学水利与能源动力工程学院,扬州225009)

针对传统的三相电网相角检测方法在电网频率波动及故障情况下存在的不足,提出了一种新型数字锁相环设计方法。所提出的锁相环通过递推最小二乘法椭圆拟合辨识出椭圆参数,利用锁相环产生不对称的正弦余弦输出,消除了电网不平衡状态下的鉴相二倍频分量;在此基础上对锁相环输出信号进行移相和正序分量的提取,从而实现90°移相与电网频率无关;推导了不对称幅值和相位与椭圆参数的关系,设计了递推最小二乘法,最后给出了仿真和实验结果。仿真和实验结果验证了本方案的有效性。

数字锁相环;椭圆拟合;递推最小二乘法;不平衡电压

在光伏发电和风力发电等新能源并网发电系统、无功补偿装置 SVG(static var generator)、不间断电源 UPS(uninterruptible power supply)等场合中需要利用电网正序电压提供同步信号,数字锁相环具有滤波和保持与电网电压同步的能力,在上述方面得到了广泛使用。

电网平衡时锁相环的常用技术是基于旋转坐标系法,计算锁相环输入输出信号相位差的正弦值,经PI调节后实现相位跟踪[1-2]。三相系统不平衡时乘法鉴相器除能生成相位差信号外,伴随二倍频信号。目前的研究主要表现在调节参数的设计和二倍频信号的滤波算法上。三相系统中的锁相环在考虑电网不平衡、畸变等不对称情况下,通常采用其正序分量进行锁相控制[3-6]。针对提取的正、负序分量,需要设计专门滤除负序分量的滤波器或自适应观测器[7-8]。

文献[9]研究了单相信号经过DFT产生正交输出因频率变化而使得输出幅值不相等问题,采用椭圆拟合进行了幅值补偿;文献[10]研究了频率变化时单相锁相环通过延时T/4周期产生正交输出的相位误差问题,采用椭圆拟合进行了相位补偿。文献[9-10]的研究工作仅适用于单相锁相环,不适合考虑频率变化的三相不平衡时三相锁相环。

在前述工作的基础上,本文研究了基于椭圆拟合的三相不平衡时考虑频率变化的三相数字锁相环。三相不平衡时经静止坐标变换后,两相电压信号既不正交、幅值也不相等,本文利用椭圆拟合方法同时辨识幅度和相位,利用锁相环产生不对称的正弦、余弦输出,消除了电网不平衡状态下的鉴相二倍频分量;在提取正序分量时考虑了频率变化,通过在锁相环输出端进行90°移相,可以实现移相与电网频率无关。本文推导了不对称幅值和相位与椭圆参数的关系,设计了递推最小二乘法,最后给出了仿真和实验结果。

1 不平衡状态下的椭圆方程

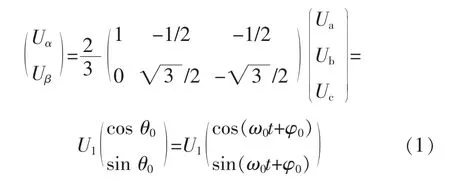

三相系统中首先将三相电压转换到两相正交的静止αβ坐标系下,获得电网平衡时电压信号的正弦、余弦分量,其转换方程为

式中:Ua、Ub、Uc分别为系统三相电压;Uα、Uβ为 αβ坐标系下的电压分量;θ0、ω0、φ0分别为 αβ 坐标系下电网电压相位角、频率和初相位;U1为电压幅值。此时Uα、Uβ在平面内的轨迹为圆。当三相系统不平衡时Uα、Uβ在平面中的轨迹为椭圆,其经过αβ变换后的电压方程为

式中:x为α轴分量;y为β轴分量;Uc和Us分别为α、β轴分量的幅值,一般情况下不相等,它们反映了电压幅值的不对称程度;φ为相位不对称程度。

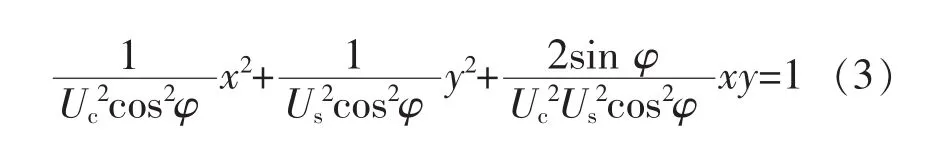

将式(2)中的时间t消除后得到的椭圆方程为

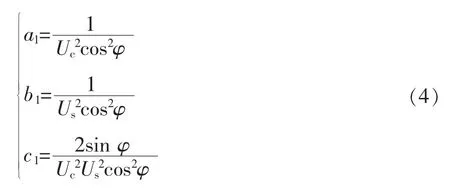

令

则得到中心点位于坐标原点的标准椭圆方程为

当通过辨识得到椭圆参数 a1、b1、c1后,由式(4)得

由式(6)求得 φ 后,可由式(4)求得 Uc和 Us。

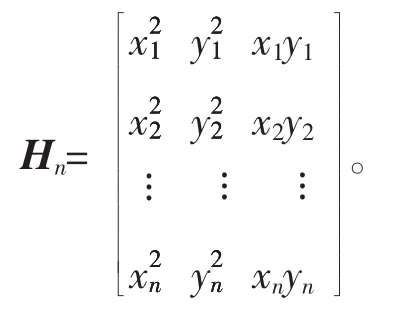

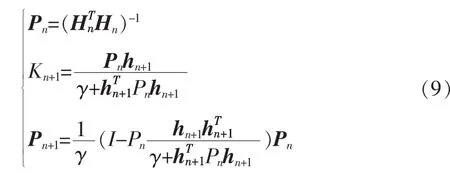

2 递推最小二乘法椭圆拟合

最小二乘法是曲线拟合中的常用方法,本文中椭圆方程有3个未知数,因此测量点数n应大于等于 3。设 n 个测量点分别为 xi、yi,i=1,2,...,n,应满足式(5),用矩阵表示为

其中:Zn=[1,1,…,1]T;λ=[a1,b1,c1]T;

由经典最小二乘法公式可求出λ为

为动态跟踪时变的椭圆参数并减少实时计算工作量,本文采用带遗忘因子的递推最小二乘法。定义:

λn的初始值对收敛速度的影响较大,为提高λn的收敛速度,本文在初始的1/4周期内,将该时间内的采样值利用式(8)求出λ,作为式(10)的初始值。遗忘因子γ对响应速度和滤波性能影响较大,当γ数值大时响应速度慢,对电网电压的谐波不敏感;当γ数值小时,则响应速度快,谐波对参数的影响较大[11],具体计算时应折中选择。

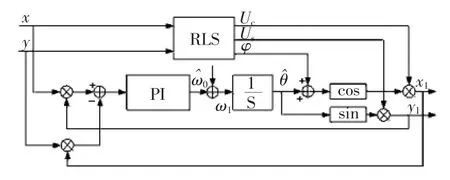

3 非对称输出锁相环

电网不平衡状态下锁相环鉴相输出中存在的二倍频分量对锁相环性能影响大[1],但如果能准确辨识出静止坐标系下的不平衡电压的幅值和相位差,则采用非对称输出锁相环,可以消除二倍频分量。设锁相环α轴输出分量为x1,β轴输出分量为y1,即

鉴相器输出定义为

式中,θ为锁相环输入信号相位,θ=ω0t+φ0。由式(12)看出在椭圆拟合准确时鉴相器无二倍频分量,不平衡输出仅影响鉴相器的幅值,此值可由PI调节补偿。因此如果使锁相环输出的信号幅值和输入信号相同,则由式(12)得到的鉴相器输出为纯粹的相位差信号,这样应将辨识参数加入到经典的锁相环中,形成所谓的不对称输出锁相环。锁相环框图见图1,图中RLS为递推最小二乘法椭圆拟合模块,为初始角频率,100 π。

这样电网电压不平衡,锁相环输出α、β轴分量与电网电压的α、β轴分量相同。电网电压可由正序分量、负序分量、零序分量3部分合成。三相不平衡电压经过αβ坐标变换后,零序分量经过αβ坐标变换后为0,变换后将正序分量和负序分量分离,将分离出的正序分量输入到常规平衡状态下的锁相环中,达到锁相环输出正序分量的目的。正、负序分量的数学表达式为

图1 基于椭圆拟合的锁相环框图Fig.1 Block diagram of DPLL based on ellipse fitting

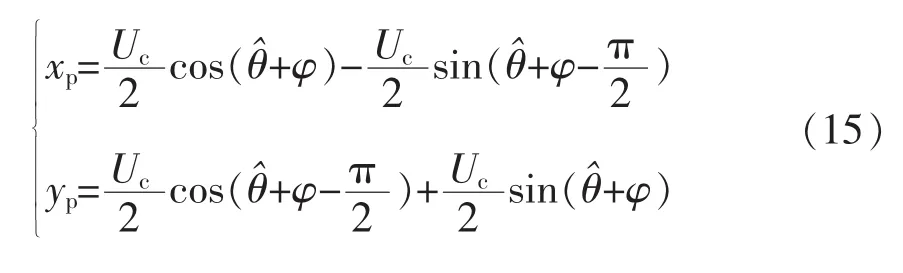

式中:Up、Un为正、负序分量的幅值;θp、θn为正负序分量初相位。利用正、负序分量的相位特征,可得到正序分量的表达式为

其中:xp、yp为正序分量在αβ轴上的幅值。

T/4延时方法是一种比较简单且常用的方法,但该方法只能在频率不变时才能得到精确的结果,考虑电网频率变化时该方法存在误差。正序分量提取的T/4延时方法的本质是900移相,由于采样时间序列中没有明显的相位信息,只能通过延时方法实现,延时移相与频率有关。为此本文提出了改进算法,不对称输出锁相环的输出信号与输入信号相比除滤出谐波外,还与输入的不对称信号同相位,且锁相环容易实现直接移相,这样将式(14)的延时转换为真正的900移相,实现了与频率无关的任意相位的移相。式(14)将变为

4 仿真和实验结果

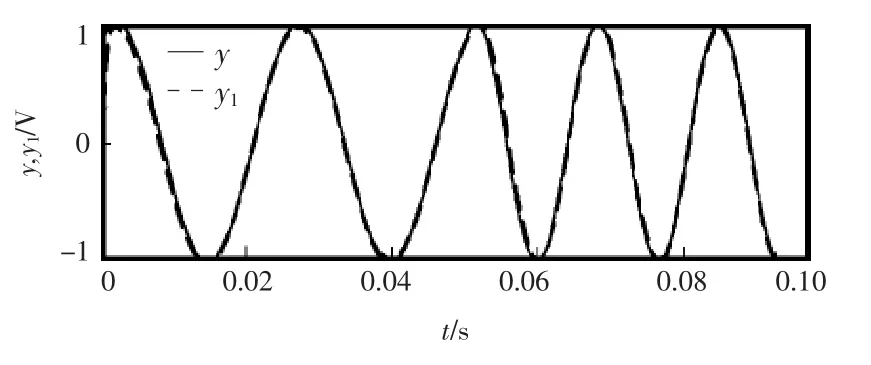

本文使用Matlab对三相锁相环进行了仿真。为验证对谐波的滤波性能,在电网电压中加入了50%的4次谐波,图2为αβ坐标系的输入电压轨迹,图3为锁相环输入输出波形,其中y为输入电压波形,y1为锁相环输出波形。由图3可见在一个周期内锁相环即可实现对输入的跟踪锁定,同时也可使得输出图形中的谐波被滤除。

图2 不平衡时输入电压轨迹Fig.2 Path of input voltage under unbalance condition

图3 输入电压包含谐波时的仿真波形Fig.3 Simulation waveforms of input voltage under the condition of voltage harmonics

为验证频率变化时的相位跟踪能力,在0.05 s时输入信号的频率从40 Hz突变到60 Hz,得到频率突变时的锁相环输出曲线,如图4所示。由图可以看出40~60 Hz的频率变化,锁相环可以实现锁定相位。

图4 频率突变时的电压波形Fig.4 Voltage waveforms with frequency mutation

当三相电网电压相位突变时刻,电压相位提前了π/2,该锁相环输出电压如图5所示,由图可见,锁相环可以在0.5个周期内锁定相位。

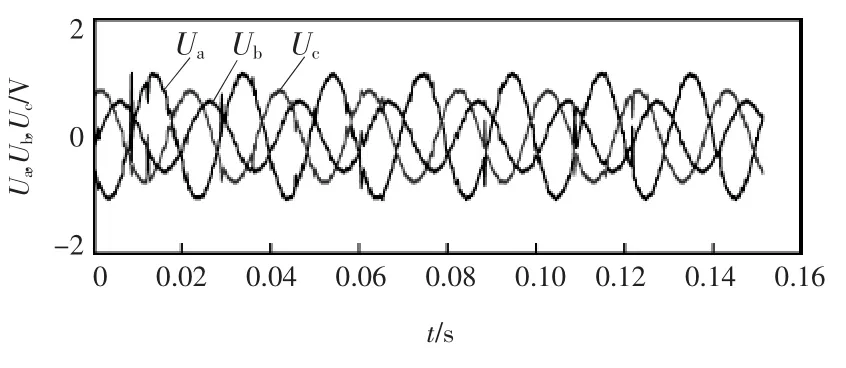

为验证不平衡下的控制效果,进行了实验测试,实验系统采用TI公司F28335DSP芯片,当输入电压不平衡时 (AB相线电压是BC相线电压的2倍),实测的电压波形见图6,可见实测波形不光滑且存在干扰脉冲。锁相环输出电压波形见图7。锁相环能输出三相对称信号,同时消除了实际采样时产生的干扰。

图5 相位突变时的电压波形Fig.5 Voltage woreforms with phase mutation

图6 三相不平衡时的输入电压曲线Fig.6 Input curves under unbalance condition

图7 三相不平衡时的锁相环输出电压曲线Fig.7 Output Voltage curves under unbalance condition

5 结语

针对三相电网电压尤其是畸变电压条件下锁相精确难度增加的问题,本文提出了基于椭圆拟合的非对称输出锁相环,在电网不平衡状态下表现出较好的性能,尤其是在电网频率变化大的场合。本文采用锁相环的不对称输出,消除了不平衡时的鉴相器输出中含有的二倍频分量,因而对低通滤波的要求较低;实现正、负序分量分离时用相位延时取代T/4延时,频率变化大实现无误差的正、负序分量分离;采用递推最小二乘法虽减少了部分工作量,但该方法仍然具有较大的工作量。

[1]吉正华,韦芬卿,杨海英.基于dq变换的三相软件锁相环设计[J].电力自动化设备, 2011,31(4):104-107.

Ji Zhenghua,Wei Fenqing,Yang Haiying.Three-phase software phase-locked loop based on dq reference frame[J].Electric Power Automation Equipment,2011,31(4):104-107(in Chinese).

[2]Suul J A,Ljokelsoy K,Undeland T.Design,tuning and testing of a flexible PLL for grid synchronization of threephase power converters[C].EPE'09.13th European Conference,2009:1-10.

[3]陈传梅,汤雨,谢少军,等.三相不平衡条件下基于可变采样周期的锁相环研究[J].电源学报, 2012,10(4):34-38.

Chen Chuanmei,Tang Yu,Xie Shaojun,et al.Study on variable sampling period PLL under distorted three-phase systems[J].Journal of Power Supply,2012,10(4):34-38(in Chinese).

[4]田桂珍,王生铁,林百娟,等.电压不平衡条件下改进型锁相环的设计与实现[J].电力电子技术,2010,44(4):85-89.

Tian Guizhen,Wang Shengtie,Lin Baijuan,et al.Design and realization of improved phase locked loop under unbalanced grid voltage[J].Power Electronics,2010,44(4):85-89(in Chinese).

[5]章勇高,高彦丽,刘焕,等.三相不平衡时的PWM整流器锁相环设计[J].华东交通大学学报,2011,28(5):14-17.

Zhang Yonggao,Gao Yanli,Liu Huan,et al.A design of soft phase lock loop in three-phase PWM rectifier under unbalance power grid[J].Journal of East China Jiaotong University,2011, 28(5):14-17(in Chinese).

[6]霍现旭,胡书举,许洪华.电网不平衡下基于自适应观测器的锁相环研究[J].电力系统保护与控制,2013,41(8):120-125.

Huo Xianxu,Hu Shuju,Xu Honghua.Phase-locked loop algorithm based on adaptive observer under unbalanced grid voltage condition[J].Power System Protection and Control,2013,41(8):120-125 (in Chinese).

[7]胡应占,郭素娜.适用于电网不平衡时的广义积分器锁相环设计[J].电力系统保护与控制,2014,42(6):148-154.

Hu Yingzhan,Guo Suna.Design of generalized integrator phase locked loop for unbalanced grid[J].Power System Protection and Control,2014,42(6):148-154(in Chinese).

[8]Sun Xiangdong,Zhang Qi,Ren Biying,et al.A novel digital phase-locked loop for distributed grid-connected power generation systems under unbalanced and distorted utility conditions[C].2010 2nd IEEE International Symposium on Power Electronics for Distributed Generation Systems,2010:813-817.

[9]杜佳玮,杨鹏,史旺旺.考虑频率变化的基于DFT单相数字锁相环的椭圆拟合方法[J].电力系统保护与控制,2015,43(10):85-90.

Du Jiawei,Yang Peng,Shi Wangwang.A novel singlephase digital phase-locked loop based on DFT considering frequency variation[J].Power System Protection and Control,2015,43(10):85-90(in Chinese).

[10]周敏杰,史旺旺.一种适用于频率变化的单相数字锁相环[J].电气传动,2014,44(11):77-79.

Zhou Minjie,Shi Wangwang.Novel single-phase digital phase locked loop considering frequency variation[J].Electric Drive,2014,44(11):77-79(in Chinese).

[11]吴旭光.系统建模和参数估计[M].北京:机械工业出版社,2002.

A Novel Digital Phase-locked Loop Under Three-phase Unbalance Voltages Based on Ellipse Fitting Method

SHI Wangwang,YAN Jianpeng

(School of Hydraulic Energy and Power Engineering,Yangzhou University,Yangzhou 225009,China)

Considering when the grid voltage is distorted and unbalanced,the dynamic behavior of classical phaselocked loop system becomes dissatisfactory,a novel digital phase-locked loop(DPLL) is put forward.In the new DPLL presented,the ellipse parameters are identified by recursive least square method and asymmetric output of DPLL produced by identified parameters,which makes the second harmonic eliminated in unbalanced voltage condition,and then 90 degree phase shift and positive sequence are produced from DPLL output signals and are not influenced by grid frequency variation.The relationship between ellipse parameters and unbalanced voltage is derived and RLS method is designed in the paper,simulation and experiment results validate the theoretical analysis.

digital phase-locked loop;ellipse fitting;recursive least square method;unbalanced voltage

史旺旺

史旺旺 (1969-),男,通信作者,博士,副教授,研究方向:光伏发电与直驱风力发电系统,E-mail:yzdxsww@163.com。

10.13234/j.issn.2095-2805.2017.4.60

TM933

A

2015-11-16

江苏省高校自然科学研究资助项目(14KJB4700 10)

Project Supported by Natural Science in Colleges and Universities in Jiangsu Province(14KJB470010)

严建鹏(1992-),男,硕士,研究方向:电力电子与电力传动,E-mail:1541787 151@qq.com。