ISCP-D2PSK调制在突发通信中的应用

2017-07-16李寅博

李寅博

【摘要】 根据符号内连续相位二进制差分相移键控(ISCP-D2PSK)调制解调原理,设计了一种基于FPGA的数字实现电路,并加入了多种扩频方式。调制端使用ROM存储基带信号,由选择逻辑控制其输出。解调端将收到的基带信号作归一化处理,并进行信号到达检测,最后由一个可变换不同解扩系数的解扩解调单元处理得到解调数据。该电路设计实现方便、占用硬件资源较少,用FPGA实现后的测试结果验证了设计的正确性,并将其应用在了某高速运动平台间的突发通信中。

【关键词】 ISCP-D2PSK 连续相位 扩频 FPGA实现

一、引言

符号内连续相位二进制差分相移键控(ISCP-D2PSK)调制解调方法是在信号调制中,不同的比特信息由符号内相位变化的累积量表示,接收端则通过积累一个符号内的相位变化累积量来实现信号解调,和码元符号的绝对相位无关。此调制方式的符号间相位为连续变化,使信号有良好的功率谱,信号为准恒包络,解调时可以避免初相、多普勒频移等引起的符号间相位变化对信号解调的影响[1]。

在某些高速运动平台间的突发通信中,多普勒频移大、通信帧短、速率要求高、硬件资源紧张,如果用相干解调的方式,导频信号会占用较多的帧长,降低有效通信速率,且实現复杂。

本文则将ISCP-D2PSK调制解调方法应用在了某高速运动平台间的突发通信中,用FPGA实现了其数字调制和解调,发挥了其优点,并加入了不同的扩频方式。最后对其进行了解调性能测试,结果表明与理论基本一致。

二、ISCP-D2PSK调制解调基本原理

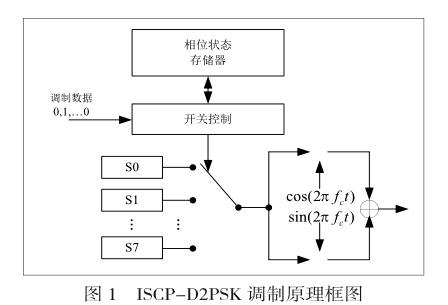

ISCP-D2PSK调制原理如图1所示,基带信号由信号选择逻辑根据输入比特符号和当前相位状态在基带信号集合中选择一个基带I、Q信号作为调制信号输出,同时更新相位状态存储器中的状态值。然后将I、Q信号进行正交调制得到中频信号。

图1输入比特数据、基带信号和状态转移的关系如表1所示,表中项目为“输出基带信号/输入比特”。

表1 基带信号选择逻辑关系

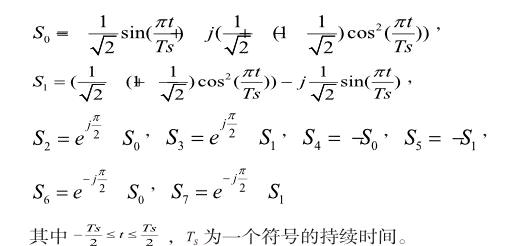

基带信号集合中包含了8种复信号分别表示如下:

在解调时,对接收到的基带信号,在一个符号持续时间内计算相位变化的累积量,并和标准相位变化累积量作比较,计算接收符号对应每一种可能发送比特的概率,选取概率最大的发送比特为当前接收信号的解码信息输出。

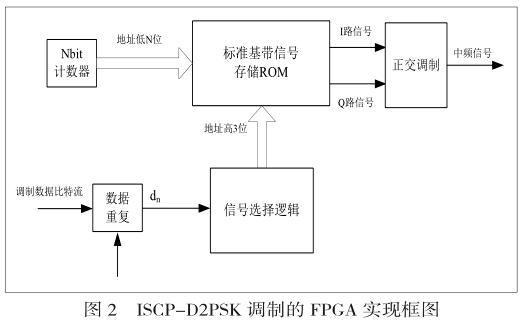

基带信号集中的信号只有两种不同的标准相位变化累积量,和不同的发送比特信息形成一一对应,其关系如表2所示,根据概率值即可选取出发送的比特信息。

表2 发送比特和相位变化累积量的对应关系

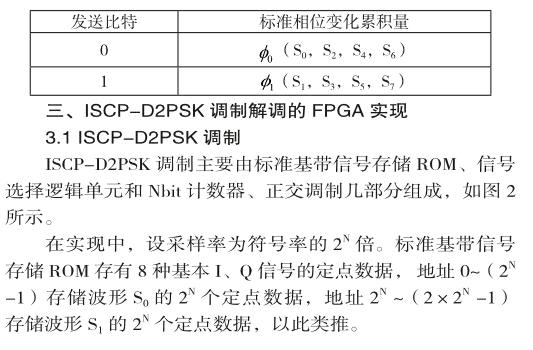

信号选择逻辑根据输入数据比特流按表1的关系生成基本I、Q信号选择值i,i按符号率进行更新,并用其控制标准基带信号存储ROM的高3位地址。

Nbit计数器按采样率进行自加,用其计数值控制标准基带信号存储ROM的低N位地址,即可将所选的一种基本I、Q信号的定点数据按顺序输出。最后将I、Q信号进行正交调制,输出中频信号。

本设计包括了多种扩频方式,因此在前端对数据比特流进行了是否重复的处理。不扩频将数据原样调制,扩频则将数据重复调制。

3.2 ISCP-D2PSK解调

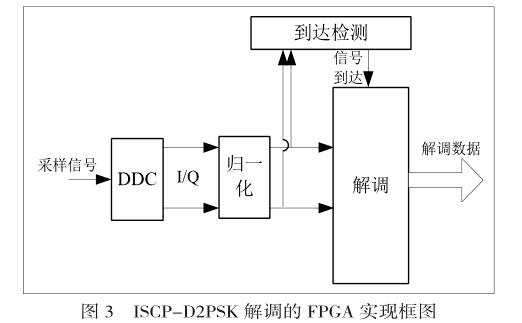

ISCP-D2PSK的解调器主要由数字下变频(DDC)、归一化、到达检测、解调几个单元组成,如图3所示。

解调器首先将按符号率M倍采样的数字信号通过DDC得到基带I、Q数据,之后对I、Q数据进行归一化处理。归一化后的数据首先在到达检测单元进行计算,当检测到信号到来时,开始对数据进行ISCP-D2PSK解调。DDC按通用的数字下变频实现方法设计[2],下面重点介绍其他几个单元的实现。

3.2.1归一化单元

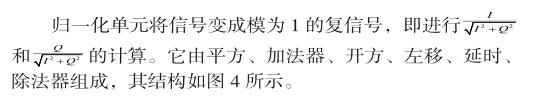

对采样数据的归一化处理是为了消除信号幅度受噪声的影响,只保留噪声对相位的干扰,同时也可以扩大解调的动态范围。

首先,将I、Q路信号进行数学运算,得到每个符号段的相位变化累积量,将结果与本地序列做相关,当没有接收到正确信号时,相关值较小,当有信号到达时,相关值出现峰值。因此可以利用相关峰的变化来确定符号的开始,给出信号到达指示,开始信号解调。

3.2.3解调单元

解调单元主要实现对数据的解扩解调,由扩频系数控制不同的解扩解调,如图6所示。

设采样率为符号率的M倍,将I、Q路的采样数据分别用m×M个移位寄存器存储。按解调原理中描述的方法,对每个符号的采样数据进行一级运算即可得到不扩频的解调数据,对每两个符号的采样数据进行两级运算即可得到2倍扩频的解调数据,以此类推,对每m个符号的采样数据进行n级运算即可得到m倍扩频的解调数据(其中,2(n-1)=m)。

在实现中,将几种扩频系数的解调单元融合到一起,由扩频系数控制取不同计算位置的数据,即可分别得到不同扩频系数的解调数据。如此,节省了硬件资源,方便了多种解扩解调的自适应变换。

四、解调性能测试结果

按以上的方法在Xilinx的FPGA芯片上实现了ISCPD2PSK的调制解调算法,占用了较少的FPGA资源。

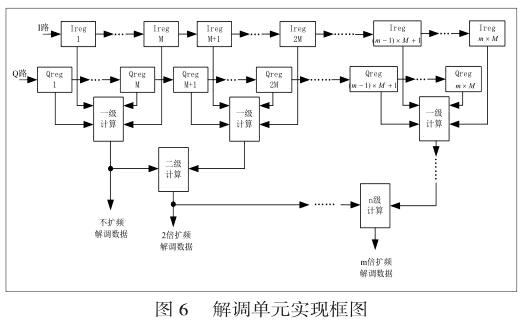

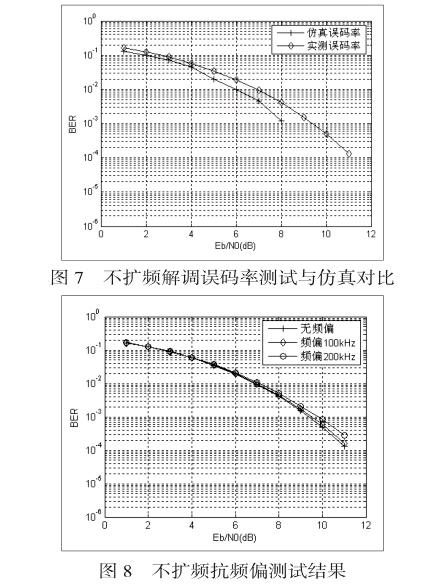

我们对实现后的解调性能进行了测试,图7给出了不扩频方式的解调误码率性能与仿真结果的对比。可以看出实测性能比仿真稍有下降,这是因为FPGA定点计算的损失和硬件底噪的影响。图8给出了不扩频方式的抗频偏性能测试结果,可以看出频偏在200kHz以内,对解调性能基本无影响。

五、结论

本文用FPGA实现了ISCP-D2PSK调制解调算法,并加入了多种扩频方式。调制设计简单,资源占用很少。解调设计时将不同扩频系数的解扩解调在一个解调单元里实现,方便不同扩频系数的自适应解扩解调变换,进一步节省了FPGA资源。测试结果验证了FPGA设计的正确性,并将其应用在了某高速运动平台间的突发通信中。

参 考 文 献

[1] 张剑. 符号内连续相位差分相移键控调制方法[J]. 电讯技术,2010,50(8):63-66.

[2] 陈洁,林伟,黄世震. WCDMA 直放站数字下变频的FPGA 实现[J]. 计算机与数字工程, 2011,259(5):153-156.

[3] 曹志刚,钱亚生. 现代通信原理[M]. 清华大学出版社,2000.

[4] 王金明. 数字系统设计与Verilog HDL[M]. 电子工业出版社, 2009