基于FPGA的多通道行波高速采集录波系统设计

2017-07-06赵玉灿陈玉林李权伟

赵玉灿, 李 彦, 陈玉林, 李权伟, 孙 浩

(南京南瑞继保电气有限公司,江苏 南京 211102)

基于FPGA的多通道行波高速采集录波系统设计

赵玉灿, 李 彦, 陈玉林, 李权伟, 孙 浩

(南京南瑞继保电气有限公司,江苏 南京 211102)

设计了一种基于FPGA的多通道行波高速采集及录波系统,利用FPGA片内双端口RAM及片外大容量DDR构成分布式两级录波缓存,搭配DSP嵌入式处理器,可实现集中式行波测距装置多通道行波信号的高速采集、连续暂态录波、长过程录波功能。该系统所采用的分级缓存机制,解耦了信号采集的“高速率”与数据缓存的“大容量”应用需求,既实现多路行波数据的实时高速采集、连续暂态录波所需的高数据吞吐率,又具备大容量缓存空间用于故障测距算法离线分析与录波数据转储,很好地满足了电力行业输电线路行波测距相关的技术规范要求。

高速采集;多通道;分布式两级录波缓存;连续暂态录波

0 引言

电力系统中输电线路发生故障时,在故障点会产生奇异突变的行波信号,对行波信号进行计算分析,运用故障测距算法[1-4],可快速定位故障点位置。由于行波信号频带较宽,以及对故障测距的精度要求,行波信号的采集要求较高的采样率和采样精度;行波测距装置还需能接入多条线路,且能实现连续暂态录波。因此,行波信号的采集具有采样率高、模拟通道多的特点,进而要求行波数据的缓存吞吐率高、容量大。传统的单通道、低采样率的采集及缓存系统已无法满足上述需求[5]。在基于FPGA的架构中[6],若仅使用FPGA片内双端口RAM存储资源,通过“冻结-解冻”的触发录波模式[7],虽然能实现数据的高吞吐率,但受限于FPGA内部紧张的RAM资源,在缓存容量上无法满足要求。而若采用FPGA搭配片外SDRAM的形式,单纯将SDRAM作为波形数据缓存区,虽然满足了大容量的需求,却因SDRAM的读写端口不能同时操作,无法在高速行波采集的同时实现高数据吞吐率的波形缓存数据搬移,存在录波死区的情况。如文献[8]无法在不中断数据采集的情况下实现连续暂态录波,文献[9]仅在出现故障时进行行波高速采样,无法对发生故障时刻之前的波形进行录波。

本文提出的分布式两级录波缓存结构,结合了FPGA内部双端口RAM的高数据吞吐率与片外DDR大容量的特点,采用分级缓存机制,有效地解决了上述问题,很好地满足了多通道行波高速采集及录波缓存的性能需求和技术规范[10,11]。

1 硬件系统结构

该行波采集及录波缓存系统采用嵌入式硬件平台设计[12,13],硬件上由前端行波数据采集电路、FPGA器件、嵌入式处理器DSP、大容量高速存储器DDR组成。系统结构如图1所示。该系统可实现多条线路的故障测距和录波功能,FPGA是行波采集和录波子系统的核心,实现行波数据的采集和录波缓存控制功能,包括驱动前端行波数据采集电路、维护两级录波缓存读写指针、响应DSP的录波指令、控制行波数据流等。DSP处理器负责故障测距功能,包括录波启动计算、下发单次或连续录波触发命令、录波数据分析、输出故障测距结果、故障波形转储等[14]。

图1 多通道行波采集与录波硬件系统结构Fig.1 System hardware architecture

由图1可知,FPGA与DSP通过高速串行总线PCIe进行行波波形数据的传输[15],其中FPGA作为PCIe总线的端节点,DSP的PCIe控制器作为根节点。DDR存储器则通过DSP的外设DDR控制器和PCIe控制器与FPGA进行数据交换,形成点对点高速通信链路。

2 分布式两级录波缓存

系统采用的两级录波缓存均为循环缓存结构,数据地址由循环计数器产生,最新数据覆盖最旧的数据,形成首尾相连的环状缓存区,如图2所示。

图2 循环缓存结构Fig.2 Loop cache structure

第一级录波缓存区位于FPGA内部,由片内双口RAM实现。RAM的其中一个端口负责高速行波数据的持续写入,另一个端口在录波触发时进行突发式数据推送。该级缓存的特点是数据吞吐量大,速度快,数据的读写可并行处理,在录波时能维持采集数据的高速、不间断写入,不存在录波死区。该级录波缓存用以缓存高速采样产生的数据流,在录波触发命令到来时,数据推送控制器将指定时间区间内的行波数据迅速搬移至第二级缓存区内。

第二级录波缓存区位于FPGA片外的DDR存储器内,与第一级缓存通过高速串行总线PCIe相连,仅在录波触发时,缓存来自前级缓存的波形数据块。该级缓存的特点是容量大,一般为数百兆甚至1 GB,有效地弥补了前级缓存容量小无法存储足够多暂态录波数据块的缺点。大容量的缓存区可使DSP对录波数据进行离线分析,尤其是在突发式连续暂态录波时,大大减轻了DSP计算性能和外部数据存储速率的压力,提供了充足的时间用以分析处理、存储搬移等。

3 系统工作原理

系统的工作原理逻辑框图如图3所示。FPGA产生前端行波数据采集电路中多路选择器和高速ADC芯片的驱动时序,接收ADC芯片输出的采样数据。预处理单元将原始的采样数据进行必要的时序及码值校准处理,并贴上采样时标,由于对每个采样点均贴上时标将大大增加数据传输和缓存的负担,且存在时标信息冗余,故本系统仅记录每组数据首个通道的采样时刻,在后端数据分析时,采用文献[16,17]所提供的通道延迟高精度时标获取方法,恢复并校准每个通道的采样时刻。

图3 系统工作原理框图Fig.3 System working principle diagram

预处理后的数据,一路经缓存控制器写入第一级缓存区,缓存控制器产生第一级缓存区数据写地址;另一路经过下采样降频至较低等效采样率,实时输出至录波触发启动单元,用以启动计算。启动单元在故障发生后约几毫秒内即完成启动判断,根据应用需求输出单次或多次录波触发信号。

推送控制器收到录波触发命令信号时,根据整定的录波时长定值,计算第一级缓存区读地址,以及第二级缓存区写地址,将本次录波命令所指定的时间区间内的暂态波形数据通过高速串行总线PCIe和DDR控制器写入第二级录波缓存区内。PCIe数据帧TLP报文中含有数据的目的地址信息,该地址由FPGA内的推送控制器产生。存储于第二级录波缓存区内的暂态录波数据块,可供DSP进行故障测距计算和波形数据转储。

两级录波缓存均由FPGA进行时序协调管理。其中首级缓存区的读写由FPGA直接控制,次级缓存区的写入则由FPGA间接控制。FPGA进行数据采集和缓存的流程图如图4所示。该流程图包含2个独立的进程,行波数据的采集进程和录波缓存进程。前者管理第一级录波缓存区的写入,不受录波触发影响,写指针始终逐次增一循环写入实时采样值,避免在连续触发录波时产生录波死区;后者管理前级缓存区的读取和后级缓存区的写入,仅在收到触发命令时启动,完成本次录波数据推送后继续等待下次录波命令。

图4 行波采集及录波流程图Fig.4 Traveling wave acquisition and recording flow chart

由于启动判断输出录波触发命令相对于输电线路发生故障时刻的滞后性,为了完整的记录故障时刻的行波信息,需要将录波触发时刻前一段时间内的波形也记录下来,定义录波触发时刻前后需要录波的波形时长分别为tpre和tpost,当数据源产生数据的速率小于数据发送速率时,tpost时长的波形数据可实时发送无需缓存,因此第一级录波缓存区容量的下限由tpre决定,而tpre又与录波启动判断延时直接相关,鉴于首级录波缓存的容量限制,本系统要求录波启动单元有较高的启动响应速度。

启动单元可以发出单次录波触发命令,也能以较小的时间间隔发送连续的触发命令。当连续触发录波周期间隔等于tpre与tpost之和时,即可实现长过程录波功能。

4 系统验证

本例按照文中的系统结构和方法,实现了10条线路30个电流通道的行波采集与录波系统,该系统的行波数据采集速率为512 Mb/s,首级录波缓存的读写并发速率各为2.56 Gb/s,首级录波缓存与次级录波缓存的数据通路采用PCIe Gen2规范,理论通信速率高达5 Gb/s,有效数据载荷带宽达4 Gb/s,DDR存储容量为256 MB,线路故障时录波启动判断延时低于4 ms,每条线路单次录波时长最高可以达8 ms。

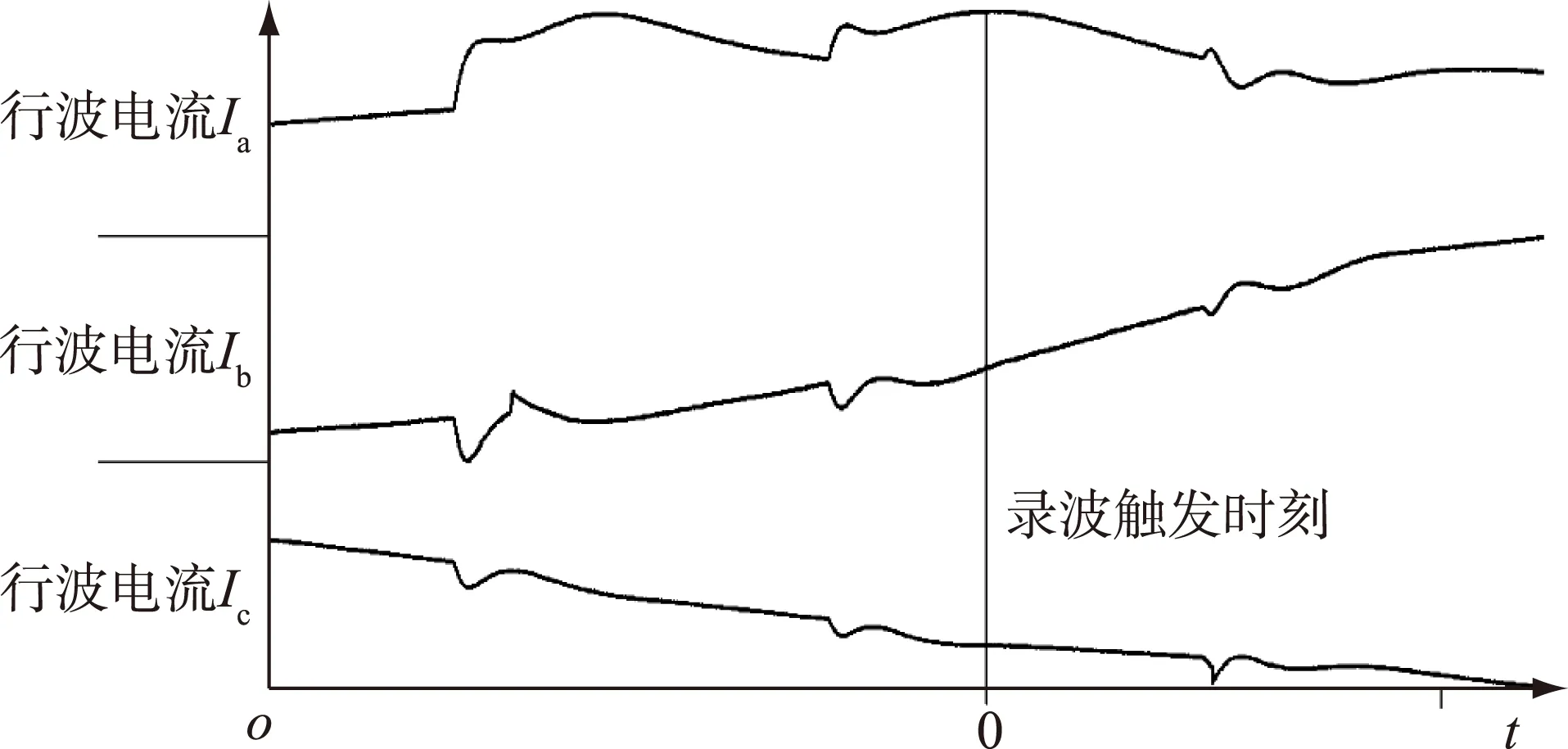

图5为从本例系统中截取的某条线路的三相行波电流波形数据。录波总时长为5 ms,横坐标0时刻对应为录波启动时刻,该时刻滞后故障发生时刻约1.896 ms。录波触发时刻前录波时长tpre为2 ms,包含了线路故障发生时刻前后波形突变的完整信息,为测距算法提高测距精度提供了完备、可靠的数据基础。

图5 单条线路行波波形图Fig.5 Single line traveling wave waveform

运行本例系统的行波故障测距装置已在工程现场投入使用,故障点测距精度为±300 m,可实现所有线路的无死区录波。该集中式行波测距装置针对接入10条线路的应用需求仍具有较大的性能裕量,理论上还可实现更多线路的行波高速采集和录波缓存,满足更高、更广的工程应用需求。

5 结语

本文提出并实现了一种输电线路故障行波采集与录波系统,以FPGA为核心,协调统筹前端高速采集电路时序与后端波形缓存管理逻辑,采用分布式的两级录波缓存结构,利用FPGA片内RAM的高效读写性能与片外DDR大容量存储的特点,形成速率与容量(时间与空间)的优势互补,很好地满足了电力行业标准中输电线路行波故障测距的技术指标和较高的系统性能裕度,也增强了对需要接入更多行波通道的应用场景的兼容性和扩展性。

[1] 王 忠,刘 奎,陆金凤,等. 一种自动识别伪根的双端故障测距快速精确算法[J]. 江苏电机工程,2016,35(6):36-41. WANG Zhong,LIU Kui,LU Jinfeng,et al. Fast and accuracy algorithm for dual-terminal fault location with automatic false root identification for HV transmission line [J]. Jiangsu Electrical Engineering,2016,35(6):36-41.

[2] 吴浩然,李 澄. 采用不同步数据的故障测距新原理研究[J]. 江苏电机工程,2016,35(6):73-76. WU Haoran,LI Cheng.Research on novel fault location principle with asynchronous Data [J]. Jiangsu Electrical Engineering,2016,35(6):73-76.

[3] 徐丙垠,李 京,陈 平,等. 现代行波测距技术及其应用[J]. 电力系统自动化,2001,25(23):62-65. XU Bingyin,LI Jing,CHEN Ping,et al. Modern fault location techniques based on fault generated travelling waves and their applications [J]. Automation of Electric Power Systems,2001,25(23):62-65.

[4] 覃 剑,葛维春,邱金辉,等. 影响输电线路行波故障测距精度的主要因素分析[J]. 电网技术,2007,31(2):28-35. QIN Jian,GE Weichun,QIU Jinhui,et al. Analysis on main influencing factors for transmission lines fault location precision based on traveling wave [J]. Power System Technology,2007,31(2):28-35.

[5] 黄 飞,周书民,汪志成,等. 行波测距用数据采集系统的设计[J]. 科学技术与工程,2012,12(31):8226-8228. HUANG Fei,ZHOU Shumin,WANG Zhicheng,et al. Data acquisition system design for traveling wave fault location [J]. Science Technology and Engineering, 2012,12(31):8226-8228.

[6] 章勇勤,艾 勇,邓德祥,等. 基于FPGA的超高速数据采集与处理系统[J]. 数据采集与处理,2009,24(2):238-242. ZHANG Yongqin,AI Yong,DENG Dexiang,et al. Ultra-high speed data acquisition and processing system based on FPGA [J]. Journal of Data Acquisition & Processing,2009,24(2):238-242.

[7] 罗 杰. 一种基于双端口RAM的高速数据采集系统设计[J]. 微电子学与计算机,2001,18(6):52-54. LUO Jie.A design for high-speed data acquisition system based on double-port RAM [J]. Microelectronics & Computer,2001,18(6):52-54.

[8] 郑秀玉,李晓明,丁坚勇,等. 行波故障定位系统中数据采集卡的设计与实现[J]. 电网技术,2008,32(5):46-50. ZHENG Xiuyu,LI Xiaoming,DING Jianyong,et al. Design and implementation of data sampling card for traveling wave fault location system [J]. Power System Technology,2008,32(5):46-50.

[9] 夏俊峰,樊亚东,李 静,等. 行波故障测距系统中高速数据采集卡的开发与应用[J]. 电力自动化设备,2006,26(1):48-51. XIA Junfeng,FAN Yadong,LI Jing,et al. Development of high-speed data acquisition system for traveling-wave fault locating system [J]. Electric Power Automation Equipment,2006,26(1):48-51.

[10] DL/T 357—2010 输电线路行波故障测距装置技术条件[S]. DL/T 357—2010 Specification for transmission line fault location equipment based on traveling wave[S].

[11] Q/CSG 110031—2012 南方电网故障录波器及行波测距装置技术规范[S]. Q/CSG 110031—2012 Technical specification for fault recorder and travelling wave fault location device of CSG [S].

[12] 仲 伟,李亚锋. 面向中低压系统保护的嵌入式软硬件平台设计[J]. 江苏电机工程,2010,29(4):4-7,11.

ZHONG Wei,LI Yafeng.The design of the software and hardware platform for medium-low voltage relay protection [J]. Jiangsu Electrical Engineering,2010,29(4):4-7,11.

[13] 牟晓勇,黄益庄,李志康,等. 嵌入式双速暂态信号同步录波装置[J]. 电力系统自动化,2003,27(20):92-94. MOU Xiaoyong,HUANG Yizhuang,LI Zhikang,et al. An embedded dual-speed synchronous acquisition recorder for transient signal [J]. Automation of Electric Power System,2003,27(20):92-94.

[14] 沈 刚,薛海平,吕 冰,等. 直流控制保护故障录波采集及远传研究与应用[J]. 江苏电机工程,2013,32(3):16-18,22. SHEN Gang,XUE Haiping,LYU Bing,et al. Research and application of TFR acquisition and remote transmission in HVDC control and protection system [J]. Jiangsu Electrical Engineering,2013,32(3):16-18,22.

[15] 王 伟,傅其祥. 基于PCIe总线的超高速信号采集卡的设计[J]. 电子设计工程,2010,18(5):43-45. WANG Wei,FU Qixiang. Design of ultra-high speed data acquisition card based on PCIe bus [J]. Electronic Design Engineering,2010,18(5):43-45.

[16] 陈玉林,陈允平,龚庆武,等. 电缆故障在线测距中高速同步采集卡精确时标获取方法[J]. 电力自动化设备,2006,26(10):35-38. CHEN Yulin,CHEN Yunping,GONG Qingwu,et al. Acquisition of precise time in synchronized high speed sampling unit for on-line cable fault locating [J]. Electric Power Automation Equipment,2006,26(10):35-38.

[17] 陈 靖,张承学.高速数据采集系统中精确时标的CPLD实现方法[J]. 继电器,2004,32(2):30-33. CHEN Jing,ZHANG Chengxue.A method of realizing precise time label in high-speed data acquisition system[J]. Relay,2004,32(2):30-33.

程师,从事电力系统继电保护装置的研究与开发工作;

李权伟(1985—),男,广东中山人,工程师,从事电力系统继电保护及控制硬件平台的研究与开发工作;

孙 浩(1987—),男,安徽淮北人,工程师,从事电力系统继电保护及控制软件平台的研究与开发工作。

(编辑 徐林菊)

High Speed Acquisition and Recording System Design for Multi-channelTraveling Wave Based on FPGA

ZHAO Yucan, LI Yan, CHEN Yulin, LI Quanwei, SUN Hao

(NR Electric Co., Ltd, Nanjing 211102, China)

A high-speed acquisition and recording system for multi-channel traveling wave based on FPGA is designed, which can implement high speed acquisition, continuous transient recording and long process recording of multi-channel traveling wave signal for centralized traveling wave distance measuring devices, utilizing FPGA dual ports RAM and off-chip high capacity DDR to construct distributed two-stage recording buffers, combined with DSP embedded processors. The hierarchical caching mechanism adopted by the system decouples the “high rate” of signal acquisition and the “large capacity” application requirement of data caching. It realizes the real-time high-speed data acquisition of multi-channel traveling wave and high data throughput required by continuous transient recording. And it also has a large capacity cache space for fault location algorithm off-line analysis and recording data dump, which meet the technical specification requirements related to traveling wave fault location for transmission lines of power industry.

high speed acquisition; multi-channel; distributed two-stage recording buffers; continuous transient recording

2017-01-08;

2017-03-01

TP274+.2

A

2096-3203(2017)03-0067-05

赵玉灿

赵玉灿(1985—),男,江苏南京人,工程师,从事变电站自动化及继电保护系统可编程逻辑研发工作;

李 彦(1979—),男,江苏无锡人,高级工程师,从事变电站自动化系统、智能变电站系统研发工作;

陈玉林(1980—),男,湖北武汉人,高级工