适于低延迟通信数据链抗干扰传输架构

2017-07-06李其虎叶海军

李其虎,叶海军

(中国电子科学研究院,北京 100041)

工程与应用

适于低延迟通信数据链抗干扰传输架构

李其虎,叶海军

(中国电子科学研究院,北京 100041)

为满足通信数据链对抗信道误码干扰能力以及低延迟传输特性的需求,设计并实现了一种满足高速信号实时处理要求的低延迟通信数据链数据抗干扰传输架构。通过深入分析算法数学原理,采用全并行流水架构设计,利用深度流水线切割结构中较长组合逻辑路径,在适当增加少量存储器资源开销基础上,大幅度提高了系统工作频率。实验结果表明本文所设计的架构硬件资源消耗少,延迟低,速度快,最高可以实现超过400MPSP处理样本的数据吞吐量,系统实际运算值与理论值完全一致,具有高可靠性。

通信数据链;低延迟;架构设计;并行化;FPGA

0 引 言

随着现代航空航天科学技术的飞速发展,当今空(天)基信息系统的物理环境变得越来越复杂,空间电磁环境变得越来越恶劣,从而使得军事战术通信系统面临日益复杂的战场通信电磁环境挑战。特别是在对无人飞行器进行“人在回路”的精确控制时,传统连接空地/空空数据链通信系统,基于直扩、跳频、多载波调制等技术[1-3],使得通信数据链虽具备一定的低截获与抗干扰能力,但难以很好地满足当前军事战术通信系统对数据链低延时、抗干扰能力的需求。为提高通信数据链系统中数据可靠性传输的能力,国内外诸多学者与工程技术人员在此方面做了大量理论研究与工程实现。文献[4]中提到的空-时编码无冲突跳频技术(STC-CFFH)较好地解决了传统跳频编码抗干扰能力差,同时有效的提高了频带利用率。文献[5]在信源级利用数字喷泉码作为前向纠错编码应用于跳频通信系统中,以提高了其抗干扰能力。此外,许多工程技术人员基于ARQ机制以及不等差错保护等技术提高了数据传输的可靠性[6-8]。但上述理论及其工程实现,都没有很好地兼顾通信系统对的低延迟特性的需求,难以满足对飞行器的“人在回路”控制需求。此外,相关文献中还提出采用自适应天线波束形成技术通过改变阵列天线方向图[9-10],在干扰方向上形成零陷或较低的天线增益,从而实现抑制干扰与信号加强目的。但该技术使用环境受限,成熟度不够,还有较多关键技术有待解决。

本文通过深入分析算法中数据流在每个环节中的状态,基于静态时序分析方法,在FPGA中采用深度切割原算法中较长路径,在适当增加少量存储资源的基础上,有效减少寄存器到寄存器端的路径延迟。系统采用全并行流水化设计,大幅度提高了整个算法的硬件工作频率。通过在FPGA中实现的架构设计实验结果表明,本文所设计的架构性能可靠、资源占有率低、数据延迟不超过一帧组帧数据量,很好地满足了工程应用中基于该架构的高速信号处理技术需求。文章后续章节安排如下:第一节介绍本文架构设计算法理论依据;第二节为硬件实现中的流水线优化与架构设计;第三节为硬件仿真实现;第四节为全文结语。

1 架构设计理论基础

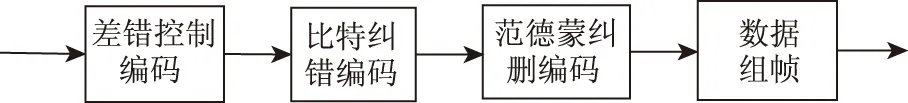

文中系统硬件架构所依据算法理论基础涉及到三种数学编码理论方式,分别为差错控制编码,比特纠错编码以及范德蒙纠删编码[11]。图1为本文架构设计算法的流程框图。为便于硬件的无反馈实现,三种编码理论都采用了适用硬件实现的快速算法进行优化设计。

图1 算法流程框图

系统设计选择的差错控制编码为八比特循环冗余校验编码,以检验每帧数据是否出错,校验结果值置于每帧数据尾部。八比特循环冗余校验编码生成多项式为Gcrc8=x8+x7+x4+x3+x+1。计算时对每个二进制数左移八位,再除以八位循环冗余校验生成多项式。由于对一个二进制数按字节表可表示为:

(1)

对(1)整体左移八位再除以生成多项式,则可表示为:

(2)

上式余数即为所求的循环冗余校验值,为了快速计算出循环冗余校验值,设:

(3)

(4)

其中Qn、Qn-1为整数,rn、rn-1为8比特二进制余数。将(4)带入(2)并联立(3),经化简与迭代计算后整理可得:

(5)

r0即为所求最终八比特循环冗余校验码。为了避免由于循环冗余校验码出错而使得编码增益下降,当八位循环冗余校验码结束后,在其后加入了(12,4)循环冗余编码的一比特纠错码。出错模式多项式G(x)=10011,校验位高4位进行补0处理。基于范德蒙矩阵的纠删编码作为本文架构设计的重要组成部分,其数学原理可简要描述如下。设数据矩阵为Dk×m,k为帧数,m为每帧数据所包含的字节数。对Dk×m进行范德蒙纠删编码后数据值可表示为矩阵En×m,则有:

(6)

(7)

(8)

ai,1为范德蒙变换矩阵经过初等变换后数据值。由于范德蒙纠删编码是在GF(28)伽罗华域上的运算。因此为减少硬件运算计算量,在硬件实现时,通过事先设计好两个编码表,将αi向量对应的十进制数,以及十进制数所对应的幂指数次数存储起来,在编译码时只需要查询这两个编码表即可,从而实现了大幅度减少编译码中的数据计算量。

2 系统架构设计与工作原理

2.1 系统架构设计策略

本文系统架构基于自顶向下设计原则,采用模块化设计思路,每个模块充分借鉴流水化设计与并行处理技术,从而使得系统的数据吞吐率得以提高,减少处理延迟。

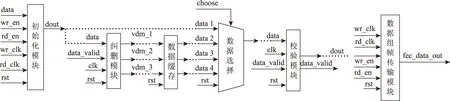

图2为本文系统硬件架构顶层设计示意图。系统架构主要由四分部模块构成,分别为初始化模块、纠删模块、校验模块和数据组帧传输模块。

图2 系统顶层架构设计示意图

2.2 系统工作原理

数据data从前端输入该系统时首先进入初始化模块。系统初始化模块设计主要目的有两点,一是割断输入数据对输出数据的影响;二是保证有足够一帧数据输入至后端模块。由于前端输入原始数据不能保证时刻都有数据流产生,而传输链路上必须时刻都必须有数据(即使传输的是空帧—无效数据)被传输以保持链路通常,因此当有效数据被送进初始化模块中时,系统首先会判断输入的有效数据是否达一帧数据量长度。当初始化模块中的长度达到一帧长度时,则该模块读使能信号rd_en启动,输出信号dout就会有数据产生。产生的数据被一分为二,并分别进入纠删模块和数据选择器。数据进入纠删模块是为了产生纠删数据帧,以便在接收端对错误数据进行恢复。以(20,17)纠删编码为例,必须经过17帧有效数据后,才会产生三行纠删帧。由于每帧纠删数据产生时是相互独立,互不干扰,且计算方式完全一致,因此硬件设计时,仅需对同一计算模块例化三次即可在经过17帧有效数据后,同时产生三帧纠删数据(即图2中的vdm_1,vdm_2,vdm_3)。由于三帧纠删数据与原始数据dout都需要经过校验模块,以确定在接收端判定该帧数据是否有错误。因此原始码流数据和纠删帧都同时存在,故需在纠删模块和数据选择器之间插入了一个数据缓存模块。数据缓存模块为缓存纠删模块输出的纠删帧数据值。一旦当前压缩码流完成数据校验后,choose信号立即启动相继选择vdm_1,vdm_2,vdm_3,并分别进入校验模块。

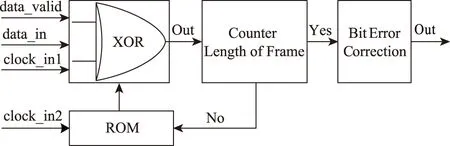

图3 数据校验模块流程图

图3为数据校验模块数据流程图。数据信号、有效信号以及时钟信号会同时进入数据校验模块最前端的异或端。异或端根据ROM存储器中提供的数据和输入数据进行计算,数据输出后进行帧长计数,从而判断进入数据校验模块的有效数据是否已经达到一帧长度。如果没有达到,则继续将得到的数据作为地址输入到ROM存储器输入端。ROM存储器中存储的是0~255共256个八比特数据的循环校验值。ROM存储器根据输入端输入的地址值,会在下一个时钟周期内输出该地址对应的循环冗余编码值。由于ROM存储器输出数据存在延时,为保证时序的对应,本文所设计数据校验模块需要2个时钟频率。ROM存储器的时钟应是编码器输入数据时钟频率的2倍。当帧长计数器达到250个字节时,八比特循环冗余码将会被送入到比特纠错编码器中,比特纠错编码器的原理与循环冗余编码器原理一致。

由于循环冗余校编码器只有在达到某一定固定字节帧长时,校验码才会输出,因此在没有校验码输出时,数据将会被直接被输出至该系统架构的最后一个数据组织传输模块。当计算器达到一帧长度时,数据校验模块会将循环校验码和纠错编码值加入到一帧数据末端再输入至数据组帧传输模块。

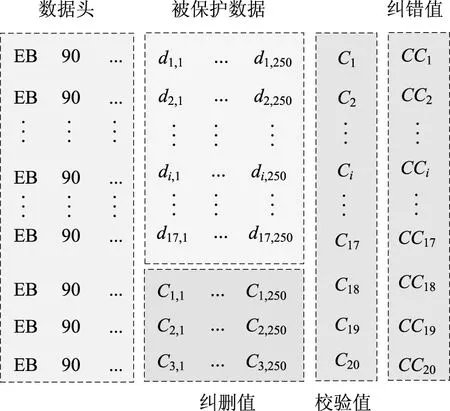

图4 帧结构示意图

数据组帧传输模块作用是对原始数据帧和纠删帧进行组帧。组帧目的是为了便于在接收端能够正确解析出接收到数据的各种类型,以便于解码纠错。系统架构采用图4所示的帧结构示意图对数据进行分装组帧。链路数据组帧采用帧—包数据构成方式进行,当数据完成组帧后,所有组帧完成数据将会被进一步送入到下一处理单元并与遥测信号一起完成进一步的组帧。

鉴于该系统架构牵涉到处理单元较多,系统设计较为复杂,为提高所设计系统架构工作时钟频率,根据硬件时序电路系统设计规则可知,设计的时序系统的最高工作频率取决于时序电路中关键路径的长度。时序电路的关键路径长度是指时序电路中存在多个寄存器到寄存器的路径,其中最长路径延迟的路径被称之为关键路径。因此在关键路径中插入寄存器的流水线结构可以有效切割关键路径,从而可以提高整个时序电路的最高稳定工作频率。由于系统架构采用模块化设计,各个模块之间都插入有一定量的数据存储单元,分析可知影响整个系统最高工作频率的是各个主要模块中的关键路径长度。因此在对各个模块设计时,都采用了静态时序分析方法对每个模块的实现结构进行分析,在较长的关键路径中,依据切分前向割集的原则,在分割线相交的路线上插入寄存器,从而提高单个模块的系统工作频率。在整个时序电路设计完成后,为使所设计的电路输出结果符合理论计算值,在整个时序电路设计完成后,需要调整各个模块的控制信号,以确保数据延迟与模块控制信号完全对齐。架构设计时为便于对所有模块进行统一控制,全系统架构采用同步复位模式进行处理。

3 设计仿真与结果分析

3.1 算法性能仿真

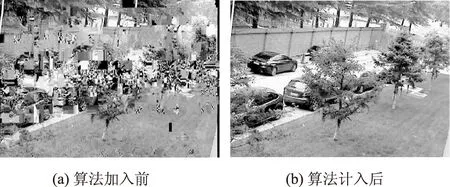

实验首先为验证本文架构设计所依据的算法的抗信道误码干扰效果,将经过H.264 highprofile级编码后的视频码流送入链路误码为1x10-5信道,通过在终端解码后视频恢复效果比较加入本文抗误码算法效果。图5为本文算法的抗信道误码干扰效果对比图。图5中左图为没有加入上述抗误码措施视频恢复质量,右图为加入上述抗误码措施视频恢复质量。

图5 抗信道误码效果对比

实验结果表明本文系统设计所采用的算法理论可有效改善链路通信质量。统计结果显示,该设计架构所采用的理论算法,可以实现将链路误码从1×10-5降低到1×10-8,能够很好的满足通信链路对低误码率性能要求。

3.2 系统架构设计验证与分析

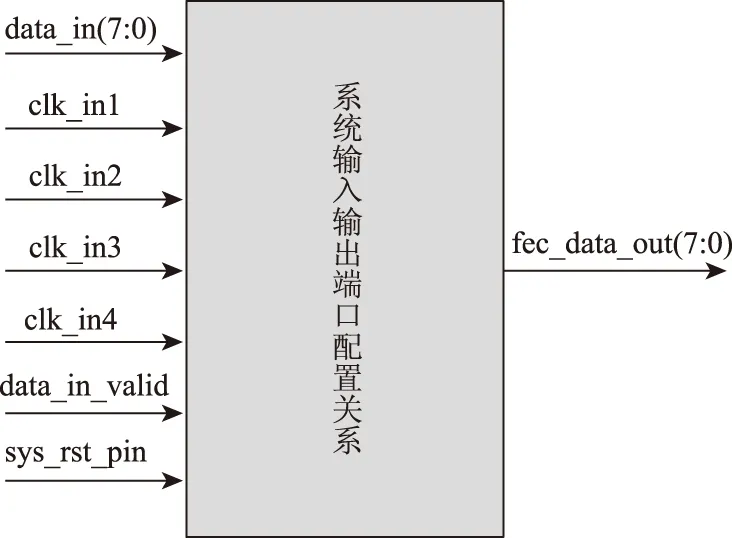

为验证工程应用时本文所设计的流水线并行化硬件架构数据处理速度以及处理后数据的正确性。实验采用在Xilinx公司的XILINX-XC5VSX50T器件中,基于ISE10.3开发环境,利用硬件描述语言,采用上述系统组成架构与流水线优化设计准则,完成了整个系统整体结构设计。结构采用模块化设计,便于层次化设计,并可以通过配置实现任意帧长和任意数据量的数据包结构。系统硬件设计外围接口如图6所示。

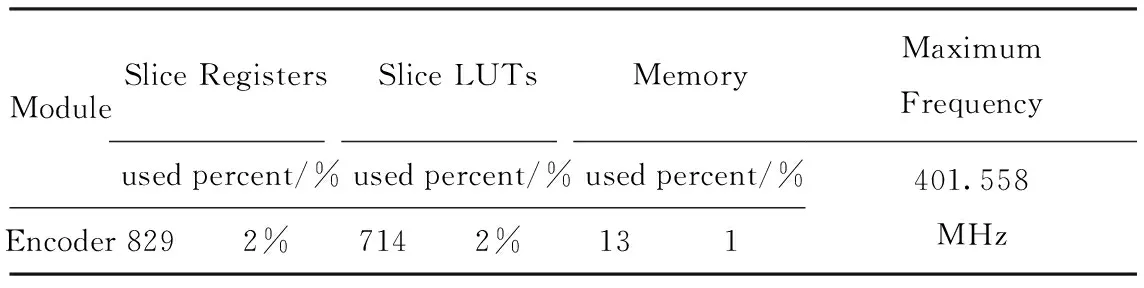

表1 系统硬件资源消耗

图6 架构设计外围接口

仿真实验通过在器件内部设计了一个模拟数据发生器,用于模拟载荷数据产生。模拟输入数据信号为data_in,clk_in1表示输入信号data_in的输入时钟,clk_in2表示读初始化模块时钟,fec_data_out表示为输出数据信号,clk_in3表示系统内部处理时钟,clk_in4表示输出信号fec_data_out读时钟,data_in_valid表示输入信号data_in是否有效,sys_rst_pin表示系统复位信号。表1为本文系统架构在XILINX- XC5VSX50T器件中的硬件资源消耗,从表中可以看出器件各个资源消耗比例最多不超过该器件资源的2%,且综合后系统工作频率最高可达401.558MHz。

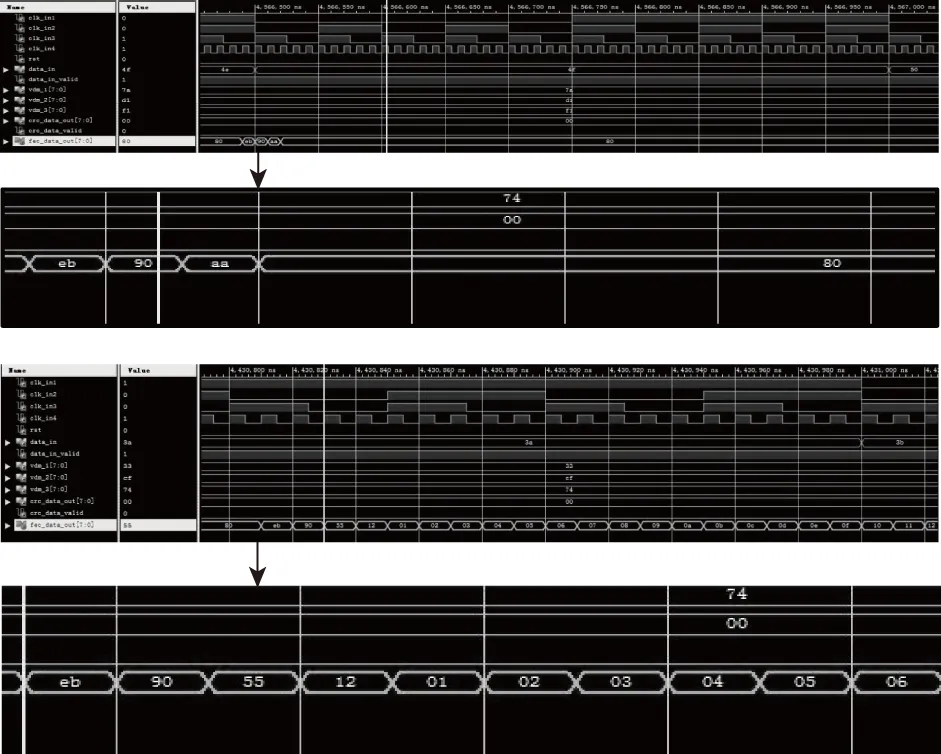

图7为数据输入输出时序仿真示意图。传输数据无效时,状态标识位显示aa,无效数据皆被赋于值80。数据有效时,状态标识为显示55,从图中可以看出,且帧计数为和传输数据都与理论计算值完全一致。

图7 时序仿真示意图

实验结果表明本文所设计的硬件架构系统实际运行得到计算值与理论值完全一致,可靠性高,硬件资源消耗低,且数据从输入到输出不超过一帧数据时钟周期的延时,因而很好地满足了通信数据链对数据低延迟传输特性的需求。

4 结 语

针对通信数据链链路对抗信道误码能力的需求,同时为满足数据链通信链路对通信数据链低延迟传输特性的要求,以范德蒙纠删编码联合八比特循环冗余编码与一比特纠错技术为基础理论,设计了一种满足低延迟高速信号实时处理需求的抗信道误码干扰硬件系统架构,并基于硬件描述语言在可编程逻辑器件中加以实现。文章在介绍架构设计前首先对范德蒙纠删编码、循环冗余编码以及一比特纠错编码的数学原理进行了简要介绍,推导了如何在硬件中快速实现上述编码算法,同时为使的通信接收端能够正确解析接收到的数据,对被传输数据与编码值进行了特定格式的分装打包。文中结合所设计的架构,系统地阐述了所设计的硬件架构工作原理,并对其进行了系统验证与分析。所描述的系统硬件架构遵循顶层规划设计原则,采用模块化、全流水并行化设计思路,具备延迟小、速度快、易集成,性能可靠,且系统架构硬件资源消耗低等优点。实际工程应用表明本文所设计实现的抗信道误码干扰系统架构,可以很好地满足了当前战术通信系统对通信数据链低延时、抗干扰特性的需求。

[1] Branimir R V, Raymond L P. Performance of direct sequence spread spectrum in a fading dispersive channel with jamming [J]. IEEE Journal on Selected Areas in Communications, 1989, 7(4): 561- 568.

[2] Phoel W G. Iterative demodulation and decoding of frequency hopped PSK in partial-band jamming [J]. IEEE Journal on Selected Areas in Communications, 2005, 23(5):1026-1033.

[3] Scholand T, Faber T, Seebers A, et al. Fast frequence hopping OFDM concept[J]. IEEE, 2005, 41(13):748-749.

[4] Lightfoot L, Zhang L, Li T T. Space-time coded collision-free frequency hopping in hostile jamming[C]//Proceedings of IEEE Milcom 2008.San Diego,CA: IEEE, 2008: 1-7.

[5] 高飞,曾宪锋,卜祥元. 数字喷泉技术在跳频通信中抗干扰性能研究[J],北京理工大学学报.2012,32(4):420-424.

[6] Yue G S, Wang X D. Efficient ARQ protocols with anti-jamming coding for cognitive radios[J]. Wireless Communications and Mobile Computing, 2009, 9(11): 1472-1486.

[7] Jeon S Y, ChoD H. An ARQ mechanism considering resource and traffic priorities in cognitive radio systems[J].

IEEE Communications Letters, 2009, 13(7): 504-506.

[8] Tannions R A, Nosratinia A. Cognitive radio protocols based on exploiting hybrid ARQ retransmissions[J]. IEEE Transactions on Wireless Communications, 2010, 9(9): 2833-2841.

[9] Choni YI, Hassan A. Optimal Adaptive antenna arrays forasynchronous communication Systems [J]. IEEE Transactions on Antennas and Propagation, 2012, 60(6):3071-3076.

[10]Hou Y G, Guo W, Jin X G An. ant i- jamming GPS receiver based on sub space decomposit ion method[ C ]// Commu nicati on S of tw are and Netw orks. USA: IEEE, 2009: 9-12.

[11]Mackay David J C. Good error-correcting codes based on very sparse matrices[J]. IEEE Tran on Information Theory,1999, 45(2): 399-431.

Architecture to Anti-jamming Transmission for Low Delay Data Links

LI Qi-hu, YE Hai-jun

(China Academy of Electronics and Information Technology,Beijing 100041,China)

In order to satisfy demand that the communication data link for the ability of the resist interference of channel error and character of low delay communication, a anti-jamming communication architecture has been designed and implemented that could satisfy requirement of high-speed real-time signal processing. Through deep analysis mathematical principles of algorithm, structure has been designed based on full parallel pipelining; and longer combinational logic path has been cutting by the depth line in the structure, and so the system working frequency has been improved greatly based on appropriate cost a small amount of storage resources. The experimental results show that the hardware resource consumption of the architecture is low, with the feature of the low delay, high speed, and more than 400MPSP processing sample of the data throughput has been achieved. The calculated actual results of system are the same with the results of theory completely, with the high reliability of the designed hardware structure.

communication data links; low delay; architecture design; parallelization; FPGA

10.3969/j.issn.1673-5692.2017.03.013

2017-02-27

2017-05-24

TN919.81

A

1673-5692(2017)03-289-06

李其虎(1983—),男,安徽人,博士,高级工程师,主要研究方向为机载通信与侦察系统;

E-mail:gucas07@126.com

叶海军(1979—),男,安徽人,高级工程师,主要研究方向为大型空基信息系统顶层设计。