基于CPLD设计实现逻辑器件的芯片级检测

2017-07-02张玲明俞凯江苏金陵机械制造总厂

■ 张玲明 俞凯/江苏金陵机械制造总厂

1 引言

随着机载电子设备飞行使用时间的增加,部件中所使用的电子元器件性能会逐渐下降甚至损坏,导致飞机航电系统出现故障。鉴于某型计算机中大量使用俄制588系列专用大规模集成电路,可运用复杂可编程逻辑器件作为硬件载体,通过VerilogHDL硬件描述语言完成所需产生的时序信号,实现对俄方芯片的逻辑功能检测。

2 588系列逻辑芯片功能分析

某型计算机的主要功能是根据输入的导航信息,计算飞机的当前位置坐标、航向角等参数,并生成控制信号,以保证飞机的自动控制、半自动控制和人工控制。计算机中的模块有两种工作模式:有源装置具有主动控制和访问并行总线的权力;无源装置相当于外部设备,不具备控制访问总线的权力,可以实现数据访问存储、一次性指令处理和同步串行码交换功能。各装置模块间的通信符合总线并行接口ГОCT11.305.903-80标准,由总线接口芯片588BA1完成16位“地址/数据”总线信号的双向传输和数据奇偶校验功能;处理器、变换器模块的运算功能由逻辑运算器件588BC2和乘法器588BP2实现;对计算机总线访问权的获取和释放由总线仲裁器588BГ1判断;主动装置对无源外设装置的访问由地址选择器588BT1进行译码,并产生相关的控制访问信号。

2.1 588BC2逻辑算术微运算器

作为逻辑算术单元的微运算器芯片,集成电路588BC2用于配合处理器芯片К588ВУ2构建中央处理运算器模块。运算器由通用16位寄存器单元、算术逻辑单元(ALU)、微指令寄存器单元、特殊标志寄存器单元和同步控制访问单元组成,其引脚功能定义如表1所示。

表1 588BC2A引脚功能定义

2.2 588BA1总线接口芯片与588BT1地址选择译码器

集成电路K588BA1又称信号收发器,用于并行总线数据较短距离的双向传输和确认应用。芯片由数据信号放大器、控制单元和奇偶校验形成单元组成。集成电路588BT1由地址译码单元、选择寄存器单元、寄存器读写外设选通控制组成,控制记录的高、低位字节。集成电路588BT1不仅仅是简单地实现地址译码功能,还能形成对外部设备的读写访问控制信号,为处理器对外设的访问控制减轻负担。

2.3 常用集成电路检测方法比较

航空电子产品往往因一片集成电路的损坏导致一部分或几部分电路不能正常工作。针对有故障的电路模块,首先要根据故障现象判断故障的大体部位,然后通过测量把故障的可能部位逐步缩小,最后找到故障所在。修理人员一般采用测引脚电压的方法来判断,但这只能判断出故障的大致部位,而且有的引脚信号有较强的时序或逻辑关系,较难测量与捕捉故障状态。

集成电路常用的检测方法包括在线测量法、非在线测量法和代换法。非在线测量指在集成电路未焊入电路时,分别测量该集成电路与已知正常同型号集成电路各引脚之间的直流电阻并进行对比,以确定其是否正常;在线测量法是利用电压测量法、电阻测量法及电流测量法等,通过在电路上测量集成电路的各引脚电压值、电阻值和电流值是否正常,来判断该集成电路是否损坏;代换法是用已知完好的同型号、同规格集成电路来代换被测集成电路,从而判断出该集成电路是否损坏。由于集成电路的制造工艺和测量仪器的匹配性存在差异等原因,非在线测量法并不精确,只能作为参考;集成电路代换法效果好,但拆卸较麻烦,因此,拆卸前应判断集成电路是否确实损坏并确定损坏程度,避免盲目拆卸。

从上述对比可见,在线测量法、非在线测量法和代换法均存在不足之处,不能可靠、准确地检测和定位集成电路芯片的故障问题。本文采用基于CPLD的可编程逻辑器件,构建一个专用检测电路,实现集成电路芯片的在线自动测试功能。

3 CPLD电路设计实现芯片级检测工作原理

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展来的器件,相对而言规模大、结构复杂,属于大规模集成电路范围,是一种由用户根据各自需要自行构造逻辑功能的数字集成电路。CPLD主要由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。在电路设计阶段首先需要选择合适的CPLD芯片型号,然后根据芯片引脚图和封装,绘制硬件电路板。基于CPLD可编程器件的逻辑检测功能设计是方案成败的关键阶段,设计流程如图1所示,可按以下步骤进行:

1) 利用软件开发工具,采用Verilog或者VHDL等高级语言编写设计;

2) 对设计进行仿真,以验证功能是否正确;

3) 验证是否满足资源占用和时序等物理要求,将设计烧录到CPLD中;

4) 对设计进行仿真,以验证时序是否正确;

5) 程序被烧录至器件中后,进入整个电路的调试、验证阶段。

图1 CPLD设计流程框图

3.1 硬件电路设计

采用Altera的MAX II系列C P L D器件,型号为EPM240T100C5N。该芯片工作电压为3.3V,工作频率最高可达200MHz,传播延时5.9ns,I/O接口兼容LVTTL、CMOS、 PCI等标准。CPLD的通用I/O接口一般通过33Ω电阻,可以直接与TTL、CMOS电平进行耦合,操作使用方便。硬件电路由电源部分、CPLD最小工作系统(即复位/时钟电路)、芯片检测接口和人机交互界面四部分组成。电源部分主要提供CPLD的工作电压,由稳压芯片AMS1117完成二次电源供电,保证输出稳定的3.3V电源。人机交互界面由PC机通信接口RS232和1602液晶字符屏两部分构成。

3.2 基于VerilogHDL语言的软件设计

软件设计使用Altera公司提供的Quartus II集成开发设计工具,支持原理图、VHDL、VerilogHDL和AHDL(Altera Hardware Description Language)等多种硬件描述语言输入形式,内嵌自有的综合器和仿真器,可完成从设计输入到硬件配置的完整PLD设计流程,使得项目开发时间大大缩短。

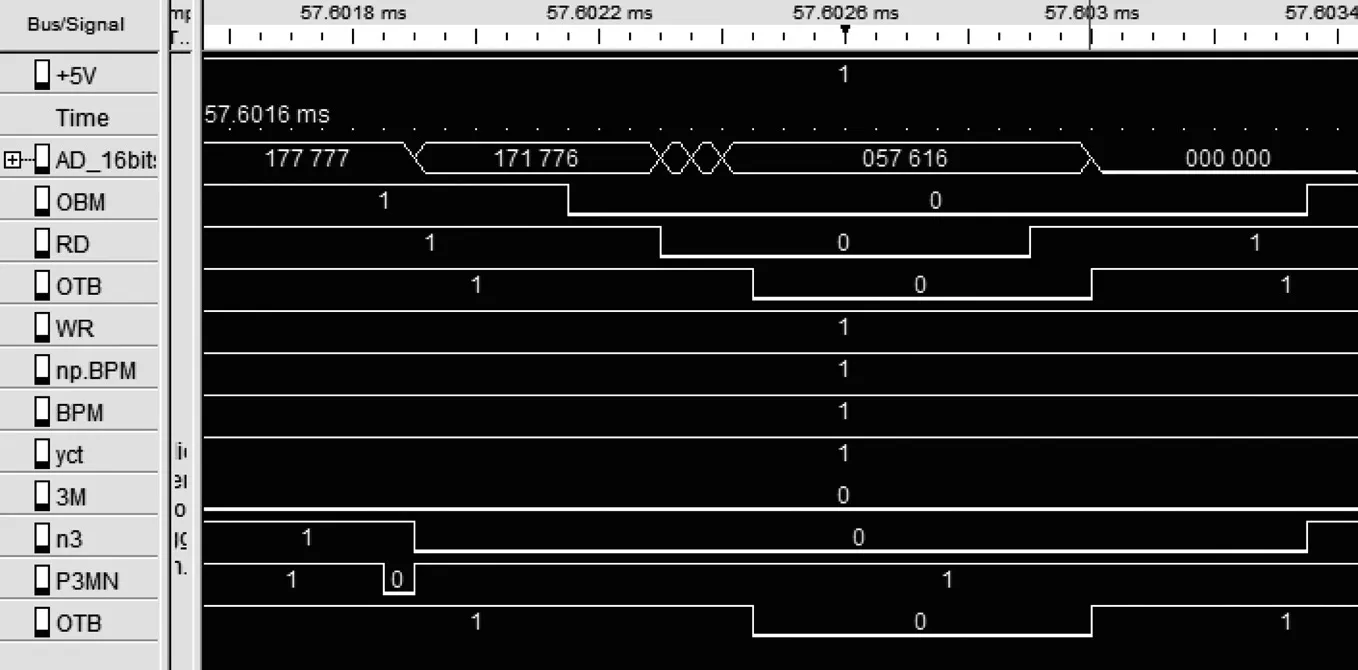

软件程序执行流程:首先,CPLD进行上电复位,初始化检测接口,设置串口通信波特率,液晶显示屏点亮开机画面。紧接着,可编程器件进入等待状态,当有检测芯片请求时,根据所要测试的芯片型号,调用相应的测试逻辑模块;检测出故障时,CPLD控制报警电路响铃,同时将芯片检测的故障信息显示在液晶屏上,并通过串口发送至PC端,完成检测。对588BA1总线接口芯片的检测由interface实体模块程序完成,定义了总线访问的16位地址、数据总线AD_Bus和总线访问控制信号OTB、OBM、RD、WR。总线接口芯片588BA1的检测波形如图2所示,具体软件程序为:

PROCESS(clk_2M)

variable cnt : integer;

BEGIN

--IF(clk_2M'EVENT AND clk_2M='1')THEN

--DOut <= 4660;

--wait for(clk_2M);

beep <= '1';

cnt := 0;

AD_Bus <= "1111111111111101";

OBM <= '0';

RD <= '0';

while RLY = '0' loop

if(cnt > 6000) then

beep <= '0';

exit;

else

cnt := cnt + 1;

end if;

end loop;

if(RLY = '1') then

DOut <= 0;

else

beep <= '1';

delay;

DOut <= CONV_INTEGER(AD_Bus);

end if;

delay;

AD_Bus <= "0111111111111111" ;

delay;delay;delay;delay;

--result <= AD_Bus;

--DOut <= CONV_INTEGER(AD_Bus);

RD <= '1';

delay;delay;

OBM <= '1';

delay;delay;delay;delay;

beep <= '0';

END PROCESS;

图2 总线接口芯片588BA1的检测波形图

4 结论

采用基于CPLD的可编程逻辑器件具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低等特点,同时可以实现较大规模的电路设计,生成严密、准确的时序信号用于实现检测集成电路芯片的逻辑功能,是一种有效、可靠的检测方法。

[1] 阎石.数字电子技术基础[M].北京:人民教育出版社,1981.

[2] 雷绍充,邵志标,梁峰.超大规模集成电路测试[M] .北京:电子工业出版社,2008.

[3] 李学干,苏东庄.计算机系统结构[M] .西安:西安电子科技大学出版社,1991.

[4] 王诚,蔡海宁,吴继华.Altera CPLD/FPGA 设计[M].北京:人民邮电出版社,2011.

[5] 赵艳华,曹丙霞,张睿.基于Quartus II的FPGA/CPLD设计[M].北京:电子工业出版社,2009.