Avalon总线的音频编解码控制器IP核设计

2017-06-27秦玉龙

秦玉龙

(宿迁学院 信息工程学院,宿迁 223800)

Avalon总线的音频编解码控制器IP核设计

秦玉龙

(宿迁学院 信息工程学院,宿迁 223800)

介绍了基于Avalon总线的WM8731音频编解码控制器IP核的设计,包括音频数据访问接口模块和Avalon-MM接口模块等,并利用SOPC技术将其封装成可重用的IP核。自定义IP核的使用,有效降低了该芯片的开发难度,同时也使系统易于扩展和升级,具有较高的灵活性。在Quartus II和ModelSim下使用VHDL语言完成了控制器的设计、仿真以及Nios II系统的构建,并通过SignalTap II逻辑分析仪进行了硬件测试。仿真和测试结果表明,该控制器满足WM8731各项时序要求。

音频编解码;自定义IP核;Avalon总线;Nios II

引 言

随着数字音频技术在语音识别、加密、音效处理等方面的广泛应用,人们对语音信号的采集与处理也提出了更高的要求[1]。传统的音频数据采集与处理系统大多基于单片机或者数字信号处理器(DSP),其具有效率低、灵活性差等缺点[2]。在基于SOPC(System On Programmable Chip,片上可编程系统)的系统中,由于FPGA的可编程性,可以根据实际需要裁减处理器,选择需要的标准外设,定制用户外设,为计算密集型任务开发专用的硬件加速器[3]。因此,SOPC方案具有灵活、高效等优点。

系统采用SOPC技术,定制了基于Avalon总线的WM8731音频编解码控制器IP核,并将其和Nios II处理器、存储器、I/O接口等标准IP核集成在一起,构成用户定制的Nios II处理器系统。在Quartus II 11.0环境下构建了基于Altera公司的EP4CE115F29C7芯片的硬件系统,在Nios II 11.0 SBT for Eclipse环境下进行了驱动程序的设计,对定制的IP核进行了完整的测试。经测试表明,音频数据采集实时性高、输出音频质量好,满足WM8731各项时序要求。

1 系统设计

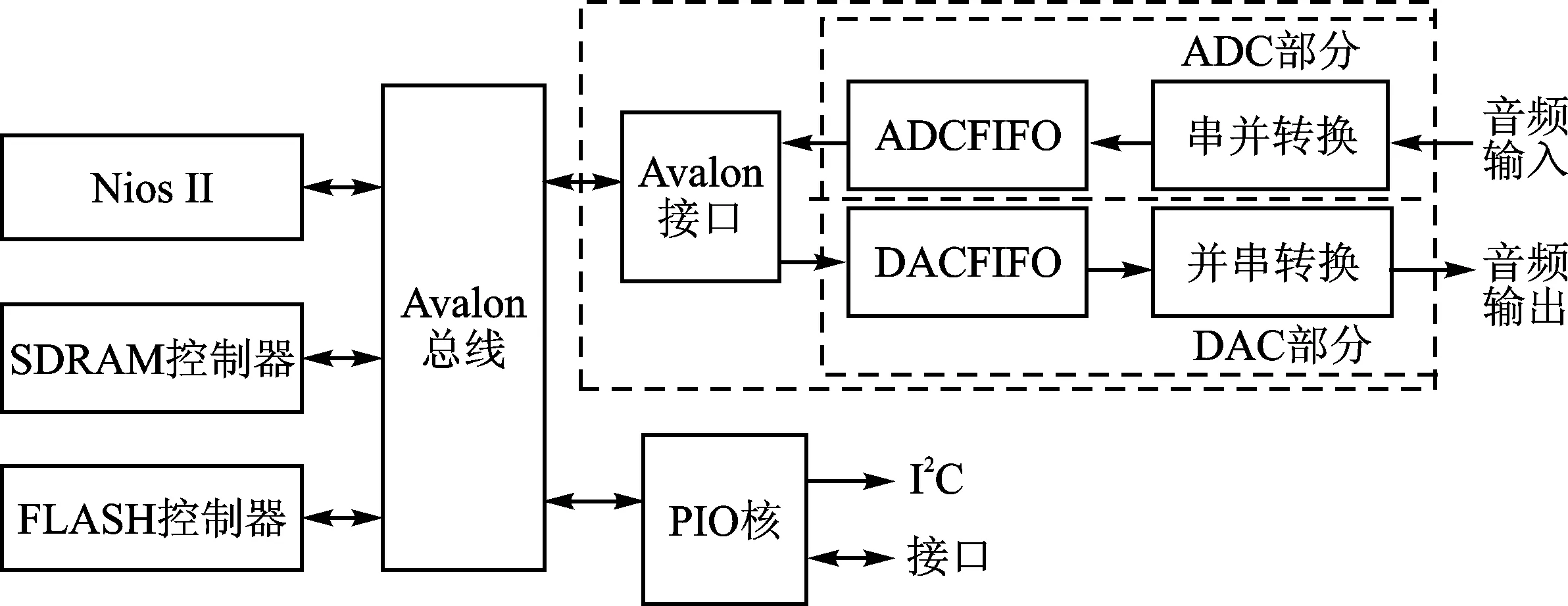

系统主要由Nios II处理器、SDRAM控制器、FLASH控制器、JTAG_UART等标准IP核以及音频编解码控制器IP核构成。系统总体框图如图1所示。

音频编解码控制器IP核由音频数据访问接口和Avalon接口模块组成。音频数据访问接口主要负责音频数据采集(ADC部分)和输出(DAC部分)。Nios II处理器作为整个系统核心,通过I2C接口配置该控制器。I2C接口时序由PIO端口通过软件模拟实现,该部分内容可参考相关文献,本文不再赘述。

图1 系统总体框图

在进行音频数据采集时,首先ADC部分负责将串行音频输入数据转换成并行数据并存入adcfifo,然后Nios II处理器可将adcfifo中的音频数据读取出来并存储到sdram中。在输出音频数据时,首先Nios II处理器将存储在sdram中的音频数据写入dacfifo,然后DAC部分负责从dacfifo中读取音频数据并进行并串转换。

2 音频编解码控制器设计

2.1 WM8731音频接口介绍

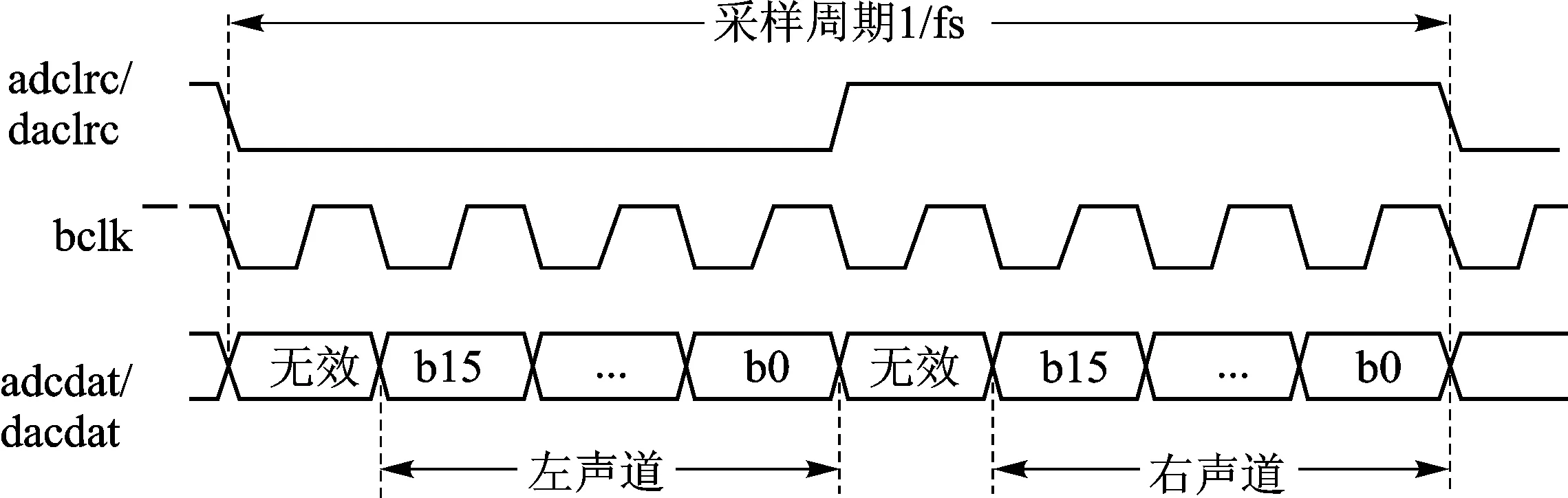

系统采用WM8731音频编解码芯片。WM8731共有4种音频接口模式[4],这些模式指定了时钟信号和串行数据之间的时序关系。在本系统中,数据访问使用I2S模式和16位分辨率。在该模式下,ADC输出的数据流格式如图2所示。有效数据在adclrc发生电平变化后的第2个bclk开始。adclrc作为一个校准时钟,用于指示adcdat是左

图2 I2S模式下ADC/ADC数据时序波形

声道还是右声道数据。当adclrc为低电平时,输出左声道数据;为高电平时,输出右声道数据。bclk作为一个位时钟,在每个时钟的下降沿输出一个新的数据。首先输出的是最高有效位。

DAC输出数据流格式与ADC的类似,但是数据是通过dacdat线从数据访问接口模块输出到WM8731芯片,daclrc作为校准时钟。

2.2 音频数据采集设计

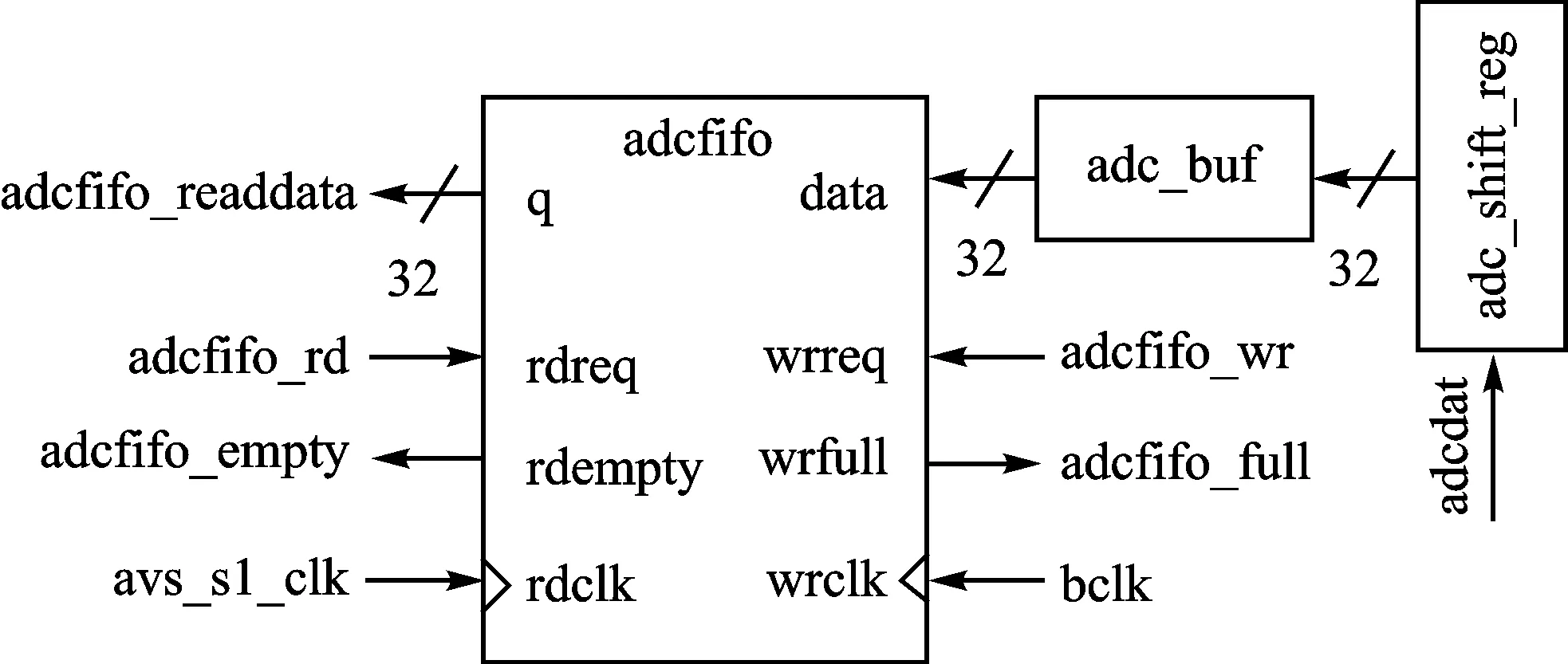

音频数据采集部分的功能框图如图3所示。首先通过移位寄存器adc_shift_reg实现串并转换;然后通过数据缓冲器adc_buf将并行数据写入adcfifo。

图3 音频数据采集功能框图

仿真波形图如图4所示。由图4可见,音频数据的采集是从adclrc信号变化后的第二个bclk时钟上升沿开始的,满足I2S模式下数据流的时序要求。音频数据的串并转换发生在adclrc信号变为0之后的第一个bclk时钟上升沿,将并行数据写入adc_buf寄存器;在该时刻如果adcfifo没有满,则产生一个adcfifo写请求信号,从而在下一个bclk时钟上升沿将数据写入adcfifo。

图4 音频数据采集仿真波形图

2.3 音频数据输出设计

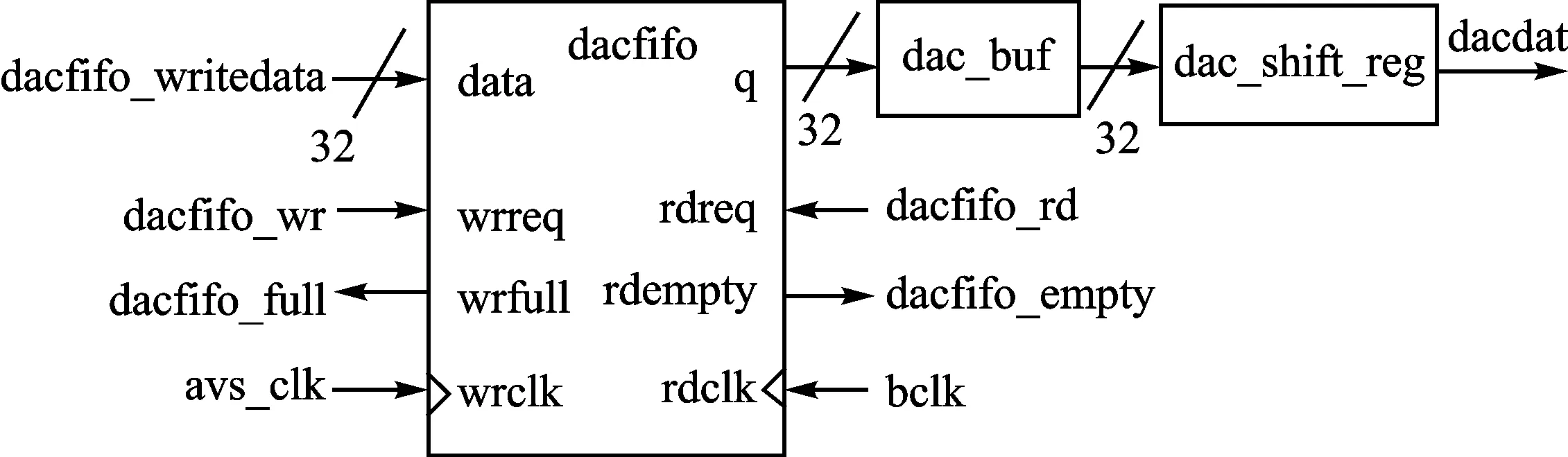

音频数据输出部分的功能框图如图5所示。在dacfifo非空时,通过输出数据缓冲器dac_buf将dacfifo中的数据加载到到移位寄存器,进行并串转换。在进行并串转换时,根据I2S模式下数据流的时序要求,在发送左右声道数据之前需要插入一个时钟周期的空闲周期,然后按照从高位到低位顺序依次输出每一位数据。

图5 音频数据输出功能框图

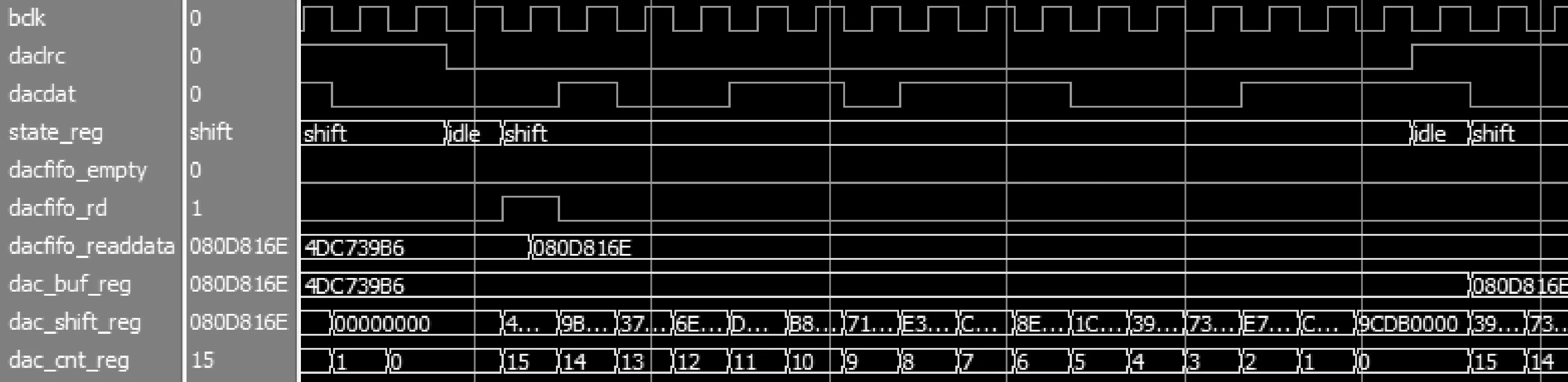

该部分仿真波形如图6所示。当检测到daclrc下降沿且dacfifo非空时,发出dacfifo_rd信号将dacfifo数据读取到q读数据总线上;同时将dac_buf缓冲器中的数据加载到dac_shift_reg移位寄存器中。当检测到daclrc上升沿时,将q读数据总线上的数据读到dac_buf缓冲器中。

图6 音频数据输出仿真波形图

2.4 Avalon接口设计

Avalon总线是Altera公司开发的用于连接Nios II处理器和各种IP核模块的总线技术[3]。为了将控制器集成到Nios II系统中,必须为其封装一个Avalon接口,使其满足Avalon接口规范中定义的信号和时序要求。

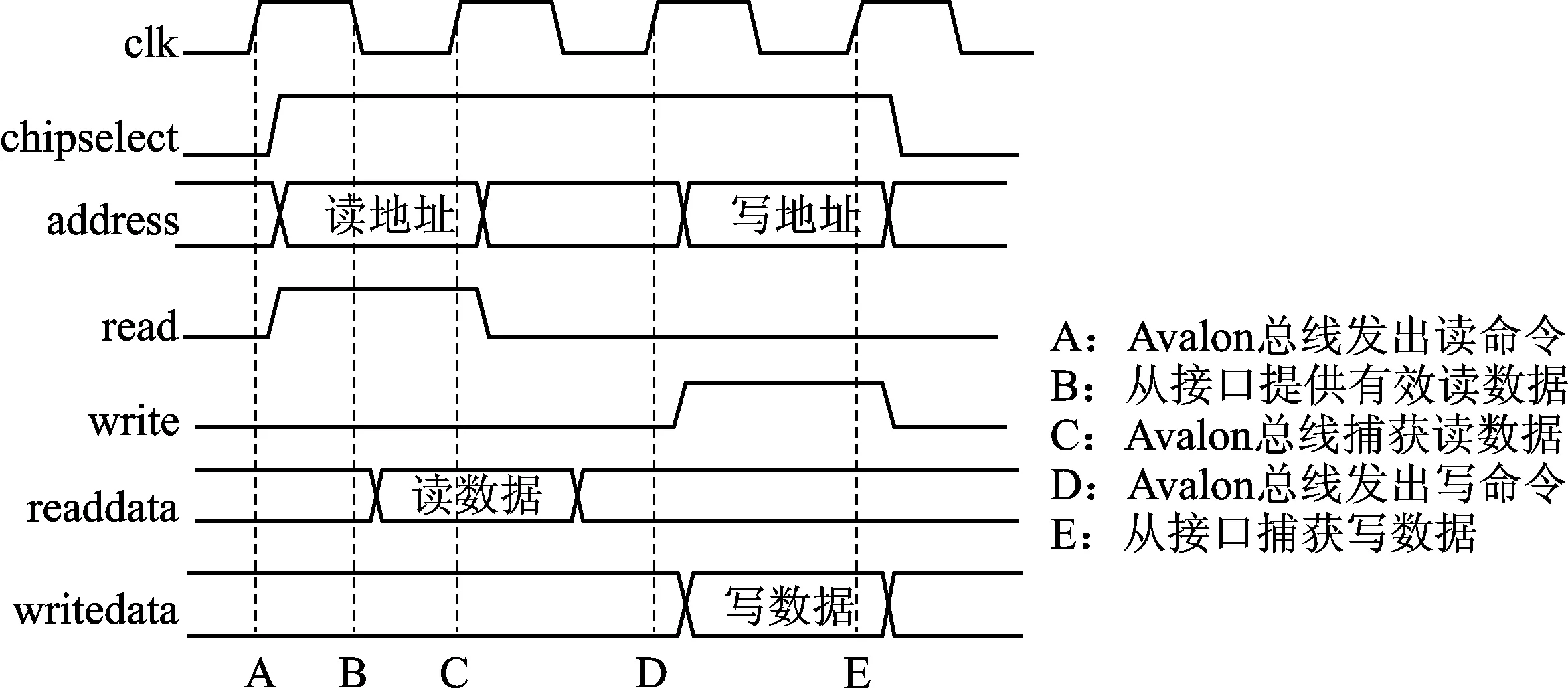

该控制器的Avalon接口主要包括一个Avalon存储器映射(Avalon-MM)从接口、一个导管(Conduit)接口、一个时钟输入接口和一个复位输入接口。从接口包含片选、地址、读写和读写数据等Avalon信号,用于与Nios II处理器交互,导管接口包含连接外部芯片所需的各信号。控制器通过从接口和Nios II处理器之间的交互如下:读取来自于adcfifo的32位音频数据或者adcfifo_empty、dacfifo_full状态信号;将32位音频数据写入dacfifo中;发送清零命令。

数据读/写操作遵循Avalon从接口的基本读/写时序,如图7所示。根据Avalon总线规范要求,读写命令由Avalon总线在时钟的上升沿发出[5]。对于读操作,从接口可在当前时钟的下降沿提供有效数据,从而保证Avalon总线能够在下一个时钟的上升沿读取到有效数据。对于写操作,从接口必须在下一个时钟的上升沿捕获写数据。

图7 Avalon从接口基本读写时序图

3 IP核的创建及测试

图8 音频编解码控制 器IP核框图

在完成音频编解码控制器设计之后,可以通过Qsys系统集成工具来创建一个新的IP核,如图8所示,可以将其集成到Nios II系统中。在设置Avalon-MM从接口s1时,根据上述Avalon接口部分的设计,需要将等待时间设置为0,即从接口s1的读写操作都是在一个时钟周期内完成的。

对该IP核的测试工作可分两个方面:搭建硬件系统平台、编写驱动程序。

硬件系统平台可以在Quartus II环境下搭建,主要由Nios II处理器、SDRAM控制器、FLASH控制器等标准IP核和用户自定义的音频编解码控制器IP核组成。

驱动程序的编写在Nios II SBT for Eclipse环境下完成,驱动程序由I2C驱动和音频数据的访问程序两部分构成,I2C驱动通过PIO端口模拟实现。音频数据访问程序可用于查看FIFO缓存器的状态,输入和输出音频数据,通过以下宏实现[6]:

IORD(audio_base,ADC_DATA_REG);

IORD(audio_base,STATUS_REG);

IOWR(audio_base,DAC_DATA_REG,data);

IOWR(audio_base,CMD_REG,data);

宏定义中各寄存器的含义如表1所列。

测试时通过SignalTap II逻辑分析仪采样到的波形如图9所示。可见,控制器的输入、输出信号均满足WM8731各项时序要求。

Audio Codec Controller IP Core Design Based on Avalon Bus

Qin Yulong

(School of Information Technology,Suqian College,Suqian 223800,China)

In the paper,the design of WM8731 audio codec controller IP core based on the Avalon bus is designed,including the codec data access interface module and the Avalon-MM interface module,which is encapsulated into reusable IP cores using SoPC technology.The use of custom IP core can effectively reduce the difficulty of the development of the chip,and makes the system easy to expand and upgrade,and it has the advantages of high flexibility.The design and simulation of the controller and the construction of Nios II system are completed in Quartus II and ModelSim using VHDL,and the hardware verification is performed using SignalTap II logic analyzer. The simulation and test results show that the controller can meet the timing requirements of WM8731.

audio codec;custom IP Core;Avalon bus;Nios II

TP334.4

A