陶瓷封装电路键合引线冲击应力下的短接判定方法

2017-06-01季振凯徐彦峰卢礼兵

季振凯,徐彦峰,卢礼兵

(中国电子科技集团公司第58研究所,江苏无锡214035)

陶瓷封装电路键合引线冲击应力下的短接判定方法

季振凯,徐彦峰,卢礼兵

(中国电子科技集团公司第58研究所,江苏无锡214035)

高可靠集成电路普遍采用陶瓷封装。但是陶封电路内部的空封结构易导致键合线在受到外界机械冲击后引起相邻键合线短接。因此在设计阶段对键合线的选择、布线布局设计、键合工艺参数优化以及封装后的引线抵抗外界应力的能力显得尤为重要。在高速摄像机摄像和电学判定组合方法的基础上,提出一种改进型的键合线短路判定方法。该方法实时对所有被测CQFP228封装的FPGA电路端口进行判定。试验证明,该方法可以大大提高判定评估准确率,降低判定步骤。

陶瓷封装;键合线;机械冲击;短路

1 引言

相较于商业级和工业级电路,高可靠集成电路对于外界环境和电路本身的稳定性具有更高的要求,目前大部分高可靠集成电路的封装都是陶瓷封装(简称陶封),相较于塑封电路,陶封电路具有以下优点[1]:

·耐湿性好;

·热冲击实验和温度循环实验后不产生引线键合根部损伤,互联可靠性高;

·氧化铝陶瓷外壳与硅芯片的热膨胀系数相差小,抗温变等能力高;

·绝缘性和气密性好,芯片不受周围环境影响,更重要的是其气密性能满足高密封的要求。

陶封电路的空腔内除芯片外不填充其他物体,由于在机载、弹载和箭载环境下,整机的瞬间加速度很大,会对陶封电路造成很大的冲击力。陶封电路的中空结构会导致电路受到冲击后键合线发生振动,如果振幅过大,相邻键合线可能会短接。键合线的短接会导致I/O端口的信号逻辑混乱,影响电路正常工作,继而导致整机功能失效,可能会产生灾难性后果。

为了防止电路受冲击后由于上述问题而导致电路功能失效,在设计过程中在考虑引线直径选择、布线布局设计、键合工艺参数优化的基础上,还要对电路依据整机应用要求进行机械冲击摸底实验,以验证封装设计的合理性和可靠性。

2 基于高速摄像的键合线短接判定方法

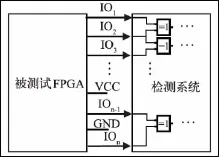

冲击实验的电路安装方式如图1所示,被冲击电路首先被电装在PCB板上并点胶固定,然后将PCB板固定于提供冲击动能的实验装置中,在放置好电路后,每次选择固定装置的X、Y、Z三个方向中的一个方向施加特定加速度的机械冲击[2]。在电路受到机械冲击的同时,进行高速摄像定位和电学判定,判定键合线是否短路。

图1 冲击实验电路安装方式示意图

2.1 高速摄像定位

在对整个固定装置施加一个冲击力的同时,使用高速摄像头捕捉键合线的振动。本次实验选用OLYMPUS型号为i-SPEED 3的高速摄像机,其拍摄的参数设置为10000帧/秒,快门速度设为2,拍摄开盖后的CB228封装芯片内键合线在冲击试验过程中的变化情况。

观察高速摄像的照片,发现在CB228封装的芯片边角上有两根键合线在振动,如图2中圈出的位置。

图2 高速摄像机瞬间拍摄照片

将它们与CB228封装的芯片封装图对照,确认两根键合线对应的引脚为P60、P61,由于高速摄像机拍出的照片属于二维图像,无法确认两根键合线是否真正短接。所以,通过高速摄像完成对疑似短接键合线的定位后,需要把疑似短接键合线所属的两个引脚引出并进行电学判定,以确认是否真正短接。

2.2 电学判定

电学判定的基本原理是在一个管脚I/O1接电源正极,相邻的另一个管脚I/O2接电源负极,在电源正极和I/O1之间串入一个电流敏感放大器,如果这两个I/O管脚对应的键合线发生短接使得回路中的电流发生变化,通过示波器监测电流敏感放大器输出端电压的变化即可判断在冲击试验过程中键合线是否发生了短接。

根据以上原理,将高速摄像定位出的振动键合线相应引脚引出,按照电学判定原理的连接方式连接,相应位置接上电源和示波器,正常情况下电源上显示电流为0 A,示波器上的电压为0 V,电流敏感放大器放大倍数为12;将CB228封装的PCB板固定在冲击试验台上,在X、Y、Z方向上改变冲击加速度和冲击方向,经过反复多次冲击,在试验过程中可以看到如图4所示的实验结果。

图3 电学判定原理图

图4 2000 g加速度冲击电压变化图

从图4中可以看到在冲击试验之前,电流敏感放大器的输出几乎为0 V电平,一旦发生接触碰撞,示波器上的电压会出现由低到高的跳变,高电平的持续时间大约为300 μs,等到碰撞结束,电压又变为几乎0 V电平。此现象说明在2000 g加速度的冲击力下,键合线已经发生了短接。

电路在受到冲击后,在电流敏感放大器的输出端如果存在①电压由低到高跳变、②维持一段时间高电平、③电压再由高到低跳变这3个过程,则说明冲击实验过程中存在短接现象。但是,该方法存在以下几个缺点:

(1)实验过程较为复杂,需要先使用高速摄像机定位,再进行电学判定,确定定位点是否确实短接;

(2)判定效率低,每次仅能同时捕捉几十根键合线,且每次电学判定仅能判定一对键合线;

(3)实验现象难以捕捉,需要不断尝试多次冲击才可能偶尔触发到电压从低到高的试验现象,而且在相同加速度下不是每次都能触发相同的试验现象。

3 基于实时端口判定的键合线短接判定方法

针对以上问题,提出一种新的方法,可以同时判断所有引脚的键合线是否与相邻引脚键合线短接。

基于FPGA电路的键合线短接判定系统基本功能框图如图5所示,整个系统由两部分构成:一部分为受冲击电路,也即被测试的FPGA电路以及使该电路正常工作的外围设备;另一部分为判定系统,该系统由一个或多个FPGA电路构成,且该系统的FPGA电路必须保证不会在受到机械冲击后发生系统功能故障。

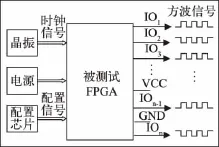

3.1 被测试FPGA电路功能说明

被测试FPGA电路的基本原理框图如图6所示。被测试FPGA电路的所有I/O引脚需连接到判定系统的FPGA电路上,且所有I/O均发出固定频率(本次实验设置成1 MHz)的方波信号,但是相邻两个引脚的方波信号相位相反,若I/O口相邻的引脚为电源或地脚,则顺延到下一引脚直至该引脚为I/O脚,且该引脚与前一引脚发出的方波信号相位相反。如果I/O脚的数量为偶数,则最后一个I/O的相位与第一个I/O的相位相反,不做特殊处理,如果I/O脚的数量为奇数,则最后一个I/O输出恒定高电平,且该引脚需要添加一个330 Ω的上拉电阻。

图5 基于FPGA电路的键合线短接判定系统功能框图

图6 被测试FPGA电路功能框图

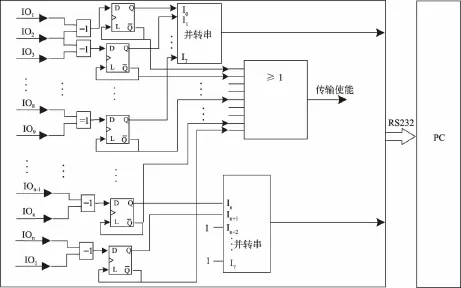

3.2 判定系统功能说明

判定系统的基本功能框图如图7所示,相邻I/O脚的信号进入判定系统的FPGA电路后进行异或逻辑运算,最后一个产生方波的I/O脚信号分别与前一个I/O和第一个I/O脚的信号做异或逻辑运算。由于相邻I/O产生的方波频率相同、相位相反,所以正常情况下相邻I/O做异或逻辑的结果始终为1。

图7 判定系统功能框图

将异或逻辑运算的结果传入一个锁存器中,如果相邻引脚短接,则必定不会产生稳定的方波信号,此时异或逻辑会产生0的运算结果,触发锁存器锁存。此时,锁存器Q输出端恒定输出0。

所有锁存器的端或逻辑运算作为数据传输使能信号,当任意一个锁存器因被测FPGA电路键合线的短接而造成锁存器Q输出端恒定为0时,输出端恒定为1,此时数据传输使能端有效。判定系统将所有锁存器的数据以8个为1组组成1个字节并将该字节数据转换成串行数据以RS232协议的传输形式传送给PC机,若锁存器不满8个则该字节数据高位填充1。

正常情况下,传输到PC机的数据为8’b1111_1111,如果I/O与I/O的键合线短接,则会产生3个连续的0;如果I/O与电源地的键合线短接,则会产生2个连续的0。根据0的个数和0在整个传输数据中的位置,可以推断出被测FPGA电路短接的键合线属于哪两个引脚。

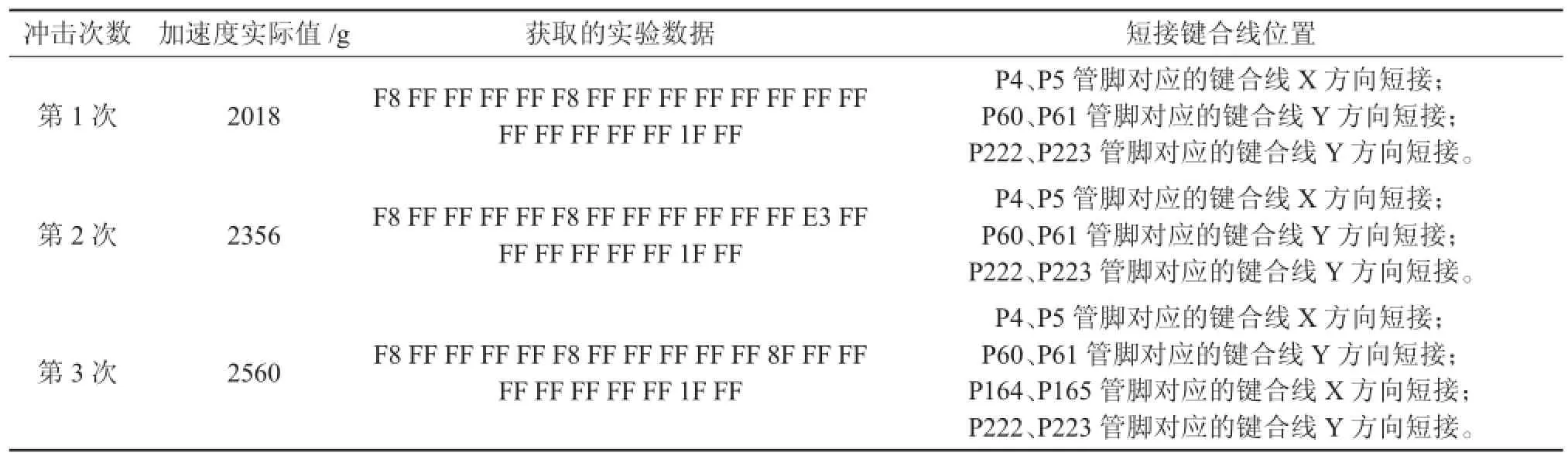

3.3 实验结果

根据以上实验原理重新对CB228封装的芯片进行3次带电冲击实验,由于CB228封装芯片P1和P2脚分别为GND和TMS,定义P3和P4做异或逻辑锁存的数据为向PC机传送的第1个字节的最低位,之后的数据位依次类推。对同一电路分别在X、Y、Z三个方向分别设置2000 g、2300 g和2500 g的加速器,实验获取的数据如表1所示。

表1 3次冲击实验的实验结果

4 结束语

在特定的应用环境下,芯片在受冲击后键合线短接判定是陶封器件可靠性评估中的必备检测项目。实时端口判定的键合线短接判定方法使用FPGA电路对所有信号分组进行逻辑运算并锁存异常数据的键合线,可以准确快速地发现陶封FPGA电路在受到冲击后短接的键合线。

[1]百度百科.SMD陶瓷封装[EB/OL].http://baike.baidu. com/link?url=MKeI0843E5Vg1bHhB3MAAwFZNeyMh AZ rqgMWN6vxbbO4pseHo03DGLfwJi8URqmi2k8Uyr-dmg O_tAaaXnk8Cqzn-BuoFPTW8ywPp-59dAMWhOlzWZxgp SiBMy01iePxwWa5vG9rzo7RaC-g9U1O5a,2017/04/05.

[2]GJB 548 B-2005.微电子器件试验方法和程序[S].

Method of Short-Circuit Determination of Bonded Wire under Shocked Stress in Ceramic Package Circuit

JI Zhenkai,XU Yanfeng,LU Libing

(China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

High-reliability integrated circuits commonly use ceramic package.However,the internal air-sealed structure of ceramic package circuit is liable to cause the bonding wire short-circuit with adjacent bonding wire when suffering externalmechanical shock.Therefore,during the designing,selection of the bonding line,wiring layout design,optimization of bonding process parameters and the package resistance to external stress are particularly important.In the paper,based on the combination of high-speed camera and electrical detection method,an improved type of short circuit detection method is proposed.The method is based on real-time detection of all measured CQFP228 FPGA circuit ports.The test results show that the method greatly improves the accuracy ofdetection and evaluation,and reduces the detection steps.

ceramic package;bonding wire;mechanicalshock;shortcircuit

TN305.94

A

1681-1070(2017)05-0008-04

季振凯(1986—),男,2009年毕业于南京大学电子科学与工程系,2009年6月起就职于中国电子科技集团公司第五十八研究所,从事超大规模集成电路测试应用及可靠性验证的研究工作。

2017-2-15