基于verilog的CRC算法的实现

2017-05-26洪向宇

洪向宇

【摘要】 循环校验码具有良好的误码检测和抗干扰能力,广泛应用于通信系统。本文从CRC原理探究串行算法,利用matlab对CRC串行算法进行仿真,利用Verilog语言实现CRC校验模块,并最终验证设计的正确性。

【关键字】 循环校验码 CRC

一、引言

循环校验码(cyclic redundancy check, CRC)具有良好的误码检测和抗干扰能力,可广泛应用于通信系统的编解码技术,提高通信系统的检错能力。由于CRC为循化冗余检验码,因此CRC能够检出大部分突发长度错误和所有奇数随机错误1。

在通信系统中,CRC编码模块常常作为通信系统的一部分出现的,因此CRC编码模块可使用硬件描述语言进行设计实现,利用可编程逻辑器件实现CRC模块,既满足了模块对校验时钟及速度的需求,也能够直接简便的实现CRC模块的硬件电路。本文基于Verilog语言,利用串行算法实现了16位校验的CRC模块并利用matlab对算法进行验证。

二、CRC串行算法

CRC校验码依据线性编码原理2。对于信源为n位的二进制数据序列,经过算法处理,即输入信源与生成多项式进行模二除法,所得余数生成m位校验码。将m位校验码放在信源序列的后面进行数据传输,接收端以相同算法对接收数据进行校验。收到信源信息,如未发生误码,则接收到的校验位应能够被生成多项式模二整除。算法公式可表示为,

其中,xnD(x)为做n位移位运算的信源序列,g(x)为生成多项式,P(x)|R(x)为模二除法的商和余数。

三、CRC算法的FPGA实现

由于并行插入16bit信源码与串行的16bit信源码序列是等效的,因此CRC串行与并行算法在电路级是等效的3。CRC算法中的模二除法可用硬件电路中的移位寄存器实现。

利用matlab可对算法进行仿真,其中g为生成多项式,input为48bit测试向量,因为本文使用了CRC16校验,因此测试向量需在帧尾补足16个0,变为64bit串行数据。运行代码,生成测试校验码R。

由于需对硬件电路进行时序匹配,因此在verilog语言中分三个模块实现CRC校验,其中初始态idle对输入进行时序的匹配和对齐,shift状态中设计移位寄存器,按照上述的算法实现移位计算,生成的校验位R(X)和din组成輸出,在信道中予以传输。

移位寄存器的代码如下所示。其中g_sequence为生成多项式。

if shift_reg[15] <= shift_reg[14] ^ g_sequence[15];

……

shift_reg[0] <= dout_ram ^ g_sequence[0];

else shift_reg <= {shift_reg[14:0],dout_ram};

值得注意的是,由于硬件电路的时序特点,在开始计算后的71个时钟周期可输出64bit数据,这是由于计算16位CRC码需要64个时钟周期,输出匹配会延迟3个时钟周期。

利用modelsim对verilog代码进行仿真,如图1所示,对比输出的校验码,为R=[1 1 0 0 1 0 1 1 1 0 1 1 1 1 1 0],与matlab代码的输出一致。

四、仿真与验证

一般的 CRC 校验码生成器即可编码又可解码, 编码用于对输入数据计算 CRC 校验码, 解码用于验证接收到的数据是否正确, 其两个过程对于CRC 校验码生成器是一样的4。

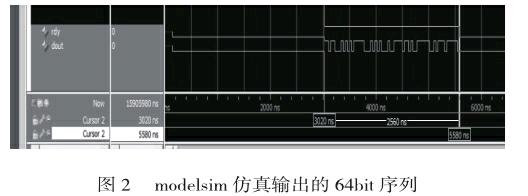

利用modelsim对Verilog代码进行仿真,测试的48bit信源序列通过CRC校验模块输出64bit序列,如图2所示。

将64bit数据导出,导入matlab CRC校验进行验证,其中input为modelsim输出的64bit序列。通过运算得出一维0矩阵,有算法可知,本文设计的CRC校验模块能够实现误码校验功能。

参 考 文 献

[1]现代通信原理 清华大学出版社

[2] CRC - 16算法与 FPGA实现,罗志聪 ,孙奇燕 四川兵工学报 35-5

[3]基于Verilog的CRC并行实现 黄维超 刘桥 黄初华 微计算机信息 2009.25 10-3

[4] CRC 校验码并行计算的 FPGA 实现 张树刚, 张遂南, 黄士坦 计算机技术与发展,2007 2 2