基于FPGA的脉冲信号参数测量仪设计

2017-05-17虞昊迪

虞昊迪

摘要:本文提出一种脉冲信号参数测量仪的设计方案,介绍以FPGA作为控制核心,实现脉冲信号的幅值、频率、占空比、上升与下降时间参数测量。本方案测量信号参数的方法是将待测信号经过电阻分压,精密半波整流,ADC直接对运放输出端进行采样,从而测得信号幅值。待测信号通过高速电压比较器分别与10%、90%峰值比较,比较结果送FPGA,利用FPGA的定时计数功能,获得频率值、占空比以及脉冲信号上升、下降时间tr。

关键词:脉冲信号参数测量仪;FPGA;信号发生器

中图分类号:TM935.4 文献标识码:A 文章编号:1007-9416(2017)03-0173-03

Abstract:This paper presents a design of pulse parameters tester programme, introduction to FPGA is used to control, achievement of pulse amplitude, frequency, duty cycle, rise and fall time measurement. Measuring method of signal parameters of this programme is to signal to be measured resistance voltage, precision half-wave rectifier, ADC sampling the op-amp output terminal directly, which measured signal amplitude. Signals to be detected by a high-speed voltage comparator separately compared with the peak 10%, 90%, comparing results to FPGA, FPGA timer counting function, access to frequency, duty cycle and the pulse rise and fall time tr。

Key Words:Pulse Parameter tester; FPGA; Signal Generator

脉冲参数测试仪是在信号类常用的一种仪器,用它可以测量峰峰值、有效值、频率、上升沿和下降沿时间、占空比等。大型台式的测试仪功能比较齐全,而手提便携式的功能还没那么完善且生产数量较少,测量精度也没有台式的高。现在最便携式的测量仪器普遍用的就是万用表,它可以测量直流电压、电阻、电流、电容等。本设计采用FPGA作为主控芯片,以整形电路、控制电路、显示电路三大模块为基础,设计出测量峰峰值、频率、占空比、上升沿和下降沿时间的参数的脉冲参数测试仪。本文主要介绍了三大模块电路,并对相应的硬软件设计思路方法进行阐述。

1 方案理论分析

我们设计的脉冲信号测量仪主要分为以下几个部分:精密整流半波电路、电压比较器、FPGA控制系统以及LCD显示。本设计中的核心是由FPGA构成的控制系统,ADC通过对THS3001输出端口进行电压采样,测量信号电压幅度。FPGA内部的计数定时功能来完成待测信号频率、占空比以及脉冲上升时间的测量。

信号参数测量仪。

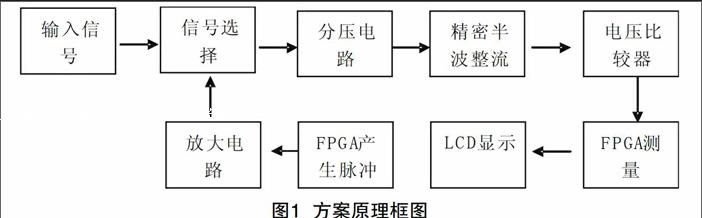

本方案主要以FPGA为核心控制系统,利用FPGA的硬件计数功能来实现信号参数的测量,并且利用FPGA把测出的数据送到LCD显示。其原理框图如图1所示。

方案的核心器件是FPGA,在高速环境下,FPGA比单片机更加适用,且使用FPGA大大降低硬件电路的复杂程度,减小体积,使电路的工作也更加稳定可靠。抗干扰和速度上,FPGA比单片机更有优势。

2 硬件电路设计

2.1 主控芯片的选择

FPGA用的是功能强大的Altera公司的Cyclone IV FPGA(含22,320逻辑单元),有32 MB的SDRAM,2 KB的EEPROM和64 Mb的串行配置存储设备。DE0-Nano是用Cyclone IV FPGA设计的紧密型开发平台,有着的一系列接口,包括 2 个可用于扩展的外接的 GPIO 在内,板载的存储设备包含有同步动态随机存取存储器(SDRAM)和电可擦除只读存储器(EEPROM),可用于较大容量的数据存储和帧缓冲,同时也配置有一般用户频繁使用的 LED 指示灯和按键等外围设备。

2.2 精密半波整流电路

本方案的精密半波整流電路是使用运放THS3001和二极管2AP9实现的。

待测信号通过电阻分压,将1/3信号电压送到THS3001的同相端。电阻和两个二极管接在反馈回路,构成精密半波整流电路。对输入信号进行半波整流。ADC在输出端进行电压采样,并将该信息送入到FPGA进行处理。

2.3 LMV7219M5电压比较电路

本设计的电压比较电路采用LMV7219M5,该芯片是一款低功耗、高速电压比较器内部迟滞,推\拉轨到轨输出。电路使用两个LMV7219M5,分别对0.5Vm与0.9Vm进行比较。将基准电压与待测信号分别输入LMV7219M5的反相端和正相端,通过两个输入端的电压比较,决定输出端口的电平高低,将其高低电平信息送至FPGA的相对应的管脚。

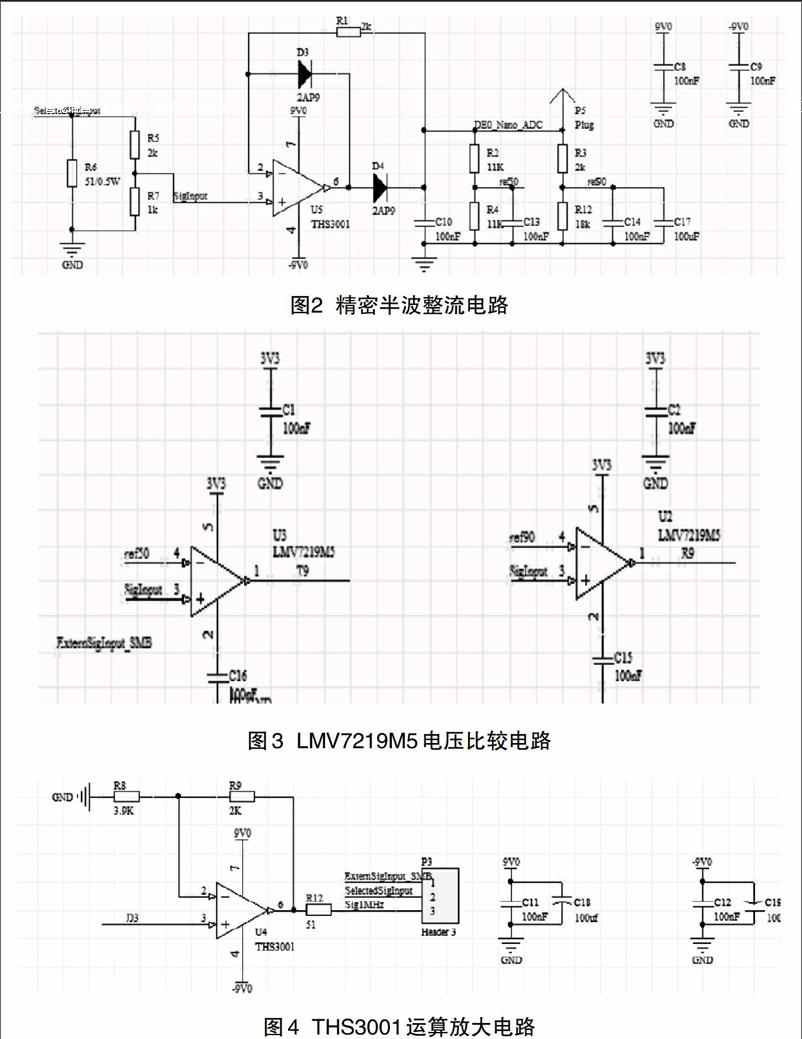

2.4 THS3001运算放大电路

FPGA产生3.3v,1MZ的脉冲信号,送到THS3001运放同相输入端,THS3001具有高达6500v/μs的转换速率,420mhz的-3db带度和良好的带内平坦度,在110mhz时,增益仅下降0.1db;大信号应用时具有40ns的建立时间;差分增益误差小于0.01%,差分相位误差小于0.02%;非线性失真小于-96db;电源电压可在±4.5~±15v之间选择,单电源工作时可在9~30v之间使用;输出电压最大可达±12v。ths3001的最大共模输入电压可接近±vcc,最大差模输入电压可达±6v,最大输出电源达100ma,经过运放放大达到5V的输出幅度。

3 程序设计

3.1 程序设计框图

3.2 显示程序

本设计采用12864显示屏,显示内容为128*64,相比与只能显示英文和数字的1602,12864能显示多行汉字,方便将需要的数据能显示在一个屏幕上.显示程序采用定时器自动扫描,定时将FPGA采集到的数据显示在显示屏上,并可开关背光灯。

3.3 數据采集程序

频率测量采用的是计数法。这是指在一定的时间间隔T内,对输入的周期信号脉冲计数为N,则信号的频率为F= N /1。测量的相对误差为I/N x100 。脉冲信号占空比,脉冲信号幅度和脉冲信号上升时间和频率的测量方法类似,这里就不再进行累述。

4 测试方案与测试结果

4.1 测试方案

(1)电路测试 将设计好的电路在仿真软件上进行仿真运行,通过分析仿真结果,调整各个参数的设置,优化电路结构。

(2)软件仿真测试 将主逻辑在电脑上编译运行,检查输出结果及动作时序。

(3)硬件软件联调 将烧录好固件的FPGA连接至电路部分,并以标准脉冲作为被测信号输入,检查LCD显示的各个参数是否符合要求。

4.2 测试结果及分析

4.2.1 频率测量结果

在输入电压为5V,占空比为50%,脉冲信号上升时间为200ns(如表1)。

4.2.2 占空比测量结果

在输入频率为1MHZ,电压为5V,脉冲信号上升时间为200ns(如表2)。

4.2.3 电压幅值测量结果

在输入信号频率为1MHZ,占空比为50%,脉冲信号上升时间为200ns(如表3)。

4.2.4 脉冲信号上升时间测量结果

在输入信号频率为1MHZ,占空比为50%,电压为5V(如表4)。

4.2.5 信号发生器参数测量

信号发生器所产生的信号频率为1MHZ,幅度为4.99V,脉宽时间为100ns, 上升时间为16ns,过冲为2%。

5 结语

通过上述测量值与实际值的对比可以得出,本设计制作的脉冲参数测量仪和信号发生器的精度较高,稳定性能较好,适合用作便携式脉冲测量仪且该设计成本较低,非常适用于工业。

参考文献

[1]童师白,华成英.模拟电子技术基础[M].第四版.北京:高等教育出版社,2006.

[2]阎石.数字电子技术基础[M].第五版.北京:高等教育出版社,2006.

[3]梅丽凤,王艳秋,汪毓铎.单片机与案例及接口技术[M].修订本.北京:北京交通大学出版社,2010.

[4]史军,雷正红.数字频率计的设计.河西学院学报,2005,21(5):37~38.

[5]凌振宝,叶剑锋.多功能数字频率计的设计与研究.吉林大学学报,2011,29(4):376~382.

[6]钱进.基于AT89C2051的高精度数字频率计的设计.机电产品开发与创新,2007,20(1):86~87.

[7]张杰,杨艳丽,马莉莉,张立倩.基于单片机C语言的数字频率计设计.内蒙古农业大学学报,2007,28(2):191~192.

[8]牛晓第,马洪涛,高志勇.数字频率计的设计.电脑开发与应用,2009,22(9):47~49.

[9]尹国光.基于单片机的数字频率计的设计和仿真.中国新通信,2008:43~45.

[10]高明华.简易数字频率计的设计.大众科技,2006,2:59~60.

[11]高晋占.微弱信号检测[M].北京:清华大学出版社,2004.