一种远程配置FPGA的方法

2017-05-17刘佳

刘佳

摘要:使用JTAG方式配置FPGA,在某些特殊环境下,因缺乏灵活性,不易操作,对设备使用产生制约。本文提出一种远程配置FPGA的方法,该方法利用PC机,通过以太网接口向Zynq传输配置文件,Zynq按照FPGA相应的配置时序,完成远程配置工作。

关键词:FPGA;远程配置;Zynq;AXI

中图分类号:TN791 文献标识码:A 文章编号:1007-9416(2017)03-0120-01

1 引言

近年来,FPGA技术广泛应用于通信、信息、信号处理等领域。传统的JTAG方式配置FPGA,强依赖于本地开发环境。当FPGA设备处于特殊环境时,远程配置功能就非常重要了。Zynq是Xilinx公司近两年力推的全可编程SOC,它将双核 ARM Cortex A9处理器系统(Processing System,PS)和可编程逻辑(Programmable Logic,PL)結合到单芯片内,并推出了PS与PL间的高速AXI总线。本文利用PC和Zynq完成对FPGA的远程配置工作,充分发挥以太网、AXI等高速接口的特性,实现高效的远程配置。

2 方案原理

远程配置,通常是指配置文件在一台PC上,待配置设备位于远端,二者可通过互联网连接。PC的作用是将配置文件通过以太网传输给设备。在设备中,包含一个Zynq SOC。该单元主要负责接收PC传来的配置文件,并完成对FPGA的具体配置工作。

在Zynq中,包括PS和PL两个模块,还含有大量的控制器资源,如USB控制器、DDR控制器,千兆以太网控制器等。AXI是Zynq中引入的新概念,它是Advanced eXtensible Interface的简称,可实现PS与PL间高速的数据交互。Zynq中AXI接口共有9个,分为3类:AXI_ACP接口、AXI_HP接口、AXI_GP接口。

Zynq收到配置文件后,可以保存在DDR或SD卡等存储器上。然后PS通过AXI接口将配置数据传递给PL。PL一边接收数据,一边实现FPGA的相应配置时序,最终完成配置工作。

3 具体实现

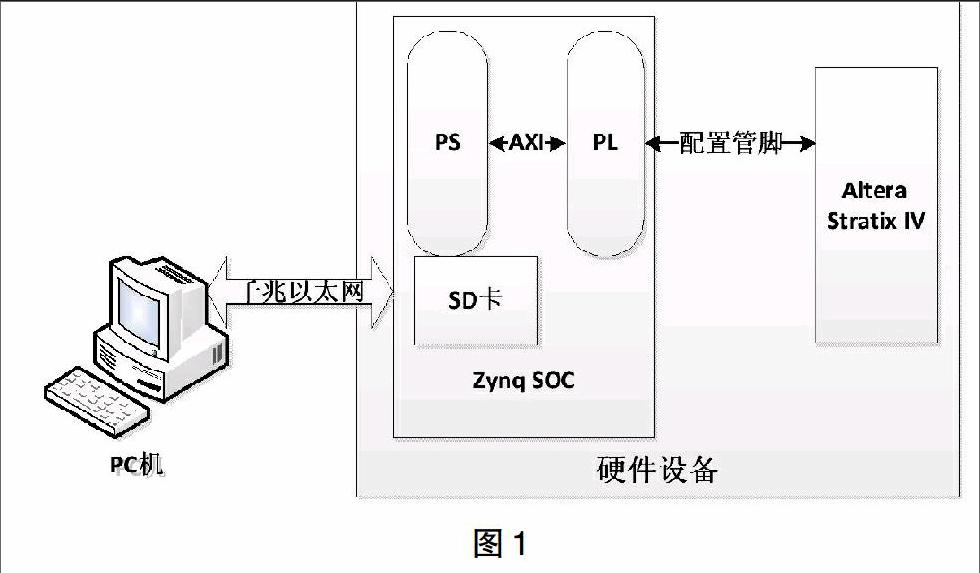

以Altera Stratix IV为例说明,Zynq SOC采用Zynq-7000系列的XC7Z030,普通PC机一台。硬件框图如图1所示。

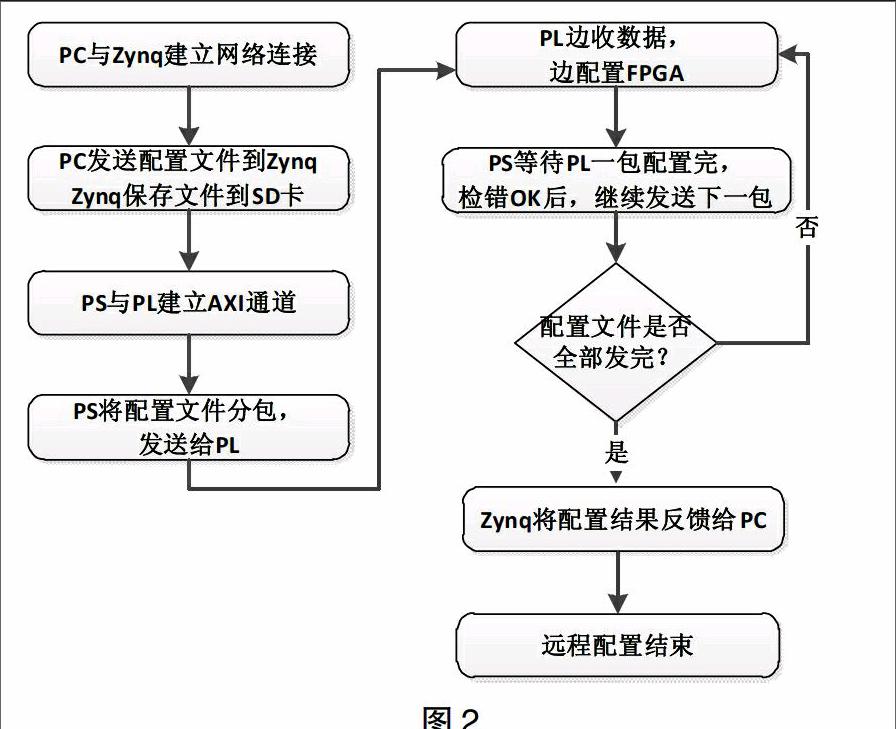

具体配置流程:

(1)PC与Zynq SOC建立TCP/IP连接,Zynq为Server,PC为Client。PC通过千兆网口将配置文件发送给Zynq,Zynq收到文件后,存到SD卡备用。

(2)Zynq中PS与PL建立AXI通道接口,PS做Master,PL做Slave。PS从SD卡读取配置文件数据,通过AXI接口,发送给PL。因配置文件通常为10几兆,因此传输时分片传输,每次可传K级别数据。

(3)PL一边接收数据,一边实现Stratix IV的配置时序,边收数据,边配置。

(4)PS每传一片数据,都要等待PL配置完成,并且检验纠错,正确时才可传送下一个数据包。

(5)重复(3)(4)步骤,至全部配置数据,传输配置完成。

(6)Zynq SOC将配置结果(成功或失败),通过以太网上报给PC。至此,完成远程配置。

流程图如图2所示。

需要注意,当PC向Zynq传送配置文件时,需要先将文件的标志信息(文件名、长度)传过去,Zynq会在本地新建同名文件。然后PC再把将文件的数据信息传过去,Zynq会自动存储到刚刚新建的文件中,以此实现配置文件的同步传送。

进行AXI数据通信时,本文选用AXI GP接口,该接口比AXI HP、AXI ACP实现简单。可选择数据位宽32bit或64bit,经典的寄存器思想,选择32bit宽时,每个AXI GP设备最多拥有512个寄存器资源,这也限制了传送配置文件数据时,最大包的最大Size。因AXI GP接口带宽高,即使分包传输,性能上依旧很好。

4 结语

借助Xilinx的Zynq SOC平台,将PS和PL的设计资源合理利用,充分发挥以太网和AXI等高速接口的性能,高效的完成FPGA的远程配置工作。本方法已在项目中得到实际运用。该方法实现巧妙,兼容性强,为硬件程序更新带来了便利。

参考文献

[1]陆佳华,江舟,马岷.嵌入式系统软硬件协同设计实战指南基于Xilinx Zynq[J].2013.

[2]何宾. Xilinx All Programmable Zynq-7000 SoC设计指南[M].清华大学出版社,2013.

[3]陶杰.FPGA局部动态可重配置的研究[J].电子科技,2009.4