基于RapidIO总线的VPX标准存储板设计

2017-05-13刘旭东

刘旭东,陈 晨

(中国科学院空间应用工程与技术中心 北京100094)

基于RapidIO总线的VPX标准存储板设计

刘旭东,陈 晨

(中国科学院空间应用工程与技术中心 北京100094)

针对现代高性能嵌入式系统RapidIO总线信号接入的应用需求,采用K7系列FPGA和mSATA盘设计了一款RapidIO接口存储容量8TB的VPX标准存储板。提出了一种基于AXI总线的RapidIO端口控制器IP核的设计方法。在FPGA内部MircoBlaze上移植μcos-II系统,编写软件实现数据在mSATA、控制器及内存间高速传输的调度。利用CPS1848交换芯片搭建RapidIO网络,搭建硬件环境测试了存储板RapidIO接口有效数据传输速率,在5 Gb/s的链接状态下读操作可达1.3 GB/s,写操作可达1.1 GB/s,表明该设计具有高速数据存储性能。

RapidIO;VPX;mSATA;数据存储;AXI总线

现代数字信号处理技术的发展,要求系统高速并实时传输大量数据,这对传输数据总线提出了更高的要求。RapidIO这种高速串行总线具有带宽高、延时低的特点,为嵌入式系统内部互联通信提供了良好的解决方案[1-4]。另一方面,高速串行总线的应用又对数据存储提出了更高的要求,如何更高效实时的进行数据存储成为了新的研究方向。固态存储这种完全采用半导体芯片作为数据存储介质和读取机构的存储形式,摒弃了磁盘物理和机械特性的缺陷[5]。基于此,本设计采用RapidIO总线结构和mSATA固态硬盘,提出了一种基于VPX标准的存储模块设计方案。

1 RapidIO总线架构设计

1.1 RapidIO技术

RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、低引脚数、基于数据包交换的互连体系结构[6-8],是为满足现在和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接[9-11]。

Rapid IO协议采用三层分级体系结构,由逻辑层、传输层和物理层构成[12],RapidIO规范层次结构见图1。逻辑层定义了所有协议和包格式,传输层为数据包从一个终端到另一个终端通道的必要信息,物理层描述了设备之间接口协议,例如包传装置,流量控制,电特性及低级错误管理等[13]。Rapid IO分为并行 Rapid IO标准和串行 Rapid IO标准,串行RapidIO是指物理层采用串行差分模拟信号传输的RapidIO标准。

图1 RapidIO规范层次结构

1.2 VPX标准

VPX标准是VME国际贸易协会于2007年提出的一种高速串行总线的总线标准。VPX标准对系统总线互联、供电方式及板卡的尺寸、结构及连接器信号定义等诸多方面,在VPX产品设计时针对不同层次、不同领域的用户建立了共同的规范,具有高可靠、高性能和系统性的优势。本设计中板卡设计遵循VITA46和VITA65规范。

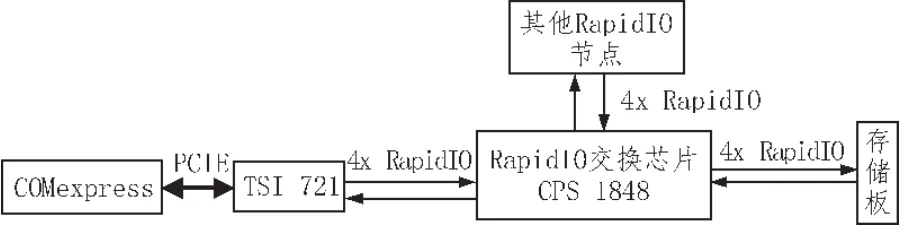

1.3 RapidIO总线架构

RapidIO总线主要应用于嵌入式系统内部互联,支持芯片到芯片、板到板间通信,可作为嵌入式设备到背板的连接。设计中RapidIO总线数据流如图2所示,如图本设计通过 TSI721桥芯片将 1路 4x PCIE总线无缝转换为1路4x RapidIO总线与交换芯片相连,同时存储板上FPGA通过GTX引出1路4x RapidIO与交换芯片相连。本设计采用的交换芯片为IDT公司的CPS 1848,该芯片最高支持12路4x RapidIO (Rev.2.1)全交换,单根线路最高支持6.25 Gbps传输速率,峰值吞吐量为240 Gbps。

图2 RapidIO总线数据流

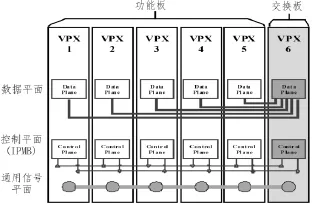

本设计符合OpenVPX标准,存储模块和交换节点均采用6U板卡实现,背板拓扑采用VITA65中BKP6-CEN06-11.2.8-n,背板拓扑图如图3所示。如图交换芯片设计在一块6U主控板上,位于slot6位置,存储板设计满足VITA46标准。

图3 背板拓扑图

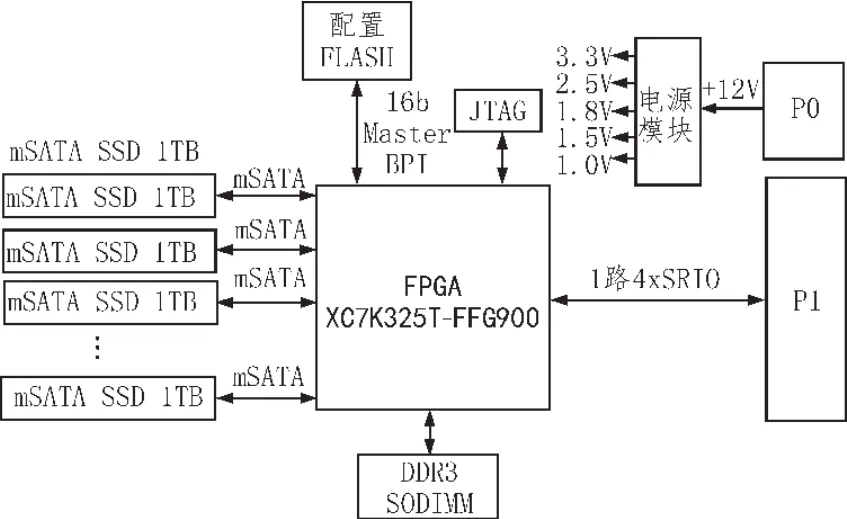

2 存储模块设计

基于VPX46标准,设计6U存储板卡。存储板结构框架如图4所示,板上FPGA通过GTX引出1路4x RapidIO与RT2连接器相连,实现存储板与背板的RapidIO总线连接。同时,FPGA提供8路mSATA接口,与板上8块固态硬盘相连,实现数据存储。FPGA选用Xilinx公司的XC7K325T-FFG900,该型号FPGA可提供16个GTX收发器,500个user IO。mSATA盘选用三星公司的850 EVO系列固态硬盘,单盘存储容量为1TB,整盘容量为8TB。

图4 存储板原理框图

2.1 FPGA设计

FPGA模块内部通过AXI总线上挂RapidIO控制器模块、DDR3接口模块、MircoBlaze控制器及AXI_SATA接口模块,实现RapidIO总线接口到mSATA接口的转换,实现数据存储与读出。FPGA结构框架图如图5所示。

2.2 RapidIO控制器模块

RapidIO控制器架构分为3层,分别为RapidIO物理层,RapidIO Link Logic层和RapidIO应用层。其中物理层和LinkLogic层采用的Xilinx官方现有IP核,RapidIO应用层是参考RapidIO标准协议[4]和SATA协议开发制定的,该层分为Data Conv和AXI SDMA两部分,Data Conv部分主要实现拆包解包功能以及一些消息回复功能,AXI SDMA主要实现接收Data Conv模块的命令与数据,并与软件进行命令的交互,与内存进行数据的交互。逻辑设计框图如下:

图5 FPGA内部结构图

图6 RapidIO分层结构

2.3 MircoBlaze设计

设计中MircoBlaze是FPGA内部软核[16-17],开发软件采用Xilinx自带的SDK 16.3。SDK支持多种操作系统的移植,本设计中采用μcos-II操作系统。本设计中MicroBlaze实现接收逻辑给出的消息,并根据消息完成内存与mSATA盘间的数据操作。图7是MircoBlaze内部软件流程图。

图7 软件设计流程图

RapidIO定义了6类请求包格式和1类响应包格式,支持读操作 (NREAD)、写操作(NWRITE、NWRITE_R)、 维 护 包 (Maintenance)、 门 铃(Doorbell)、消息(Message)等操作[14-15]。软件使用时首先对mSATA和μcos系统都进行初始化。初始化后如果接到的消息为写请求,通过SDMA中段将接到的消息上添加Address及Tag回复响应,外部接到响应后将数据写在内存对应的Address上,数据写完后软件收到DMA数据中断,将内存中数据通过mSATA写操作,将数据写到mSATA盘中;如果接到的消息为读请求,通过SDMA中段将接到的消息上添加Address回复响应,发出响应后将数据通过mSATA读操作将mSATA中制定的逻辑块地址上的数据读出到内存,再通过写操作将内存中数据写到外部,数据写完后软件会发送一个门铃给外部。

3 实际测试

基于上述内容,设计了1款符合VPX46标准的6U存储板卡,该板卡采用Xilinx公司XC7K325TFFG900型号FPGA和三星公司的EVO850系列mSATA盘。单板提供1路4x RapidIO数据总线,8TB数据存储容量及8GB的内存容量。通过存储板与主控板、背板搭建测试环境,在RapidIO总线为4x模式,包大小为4096 byte,读写操作的数据块大小为2MB情况下,得到主控板与存储板间传输速率如表1所示。

表1 RapidIO总线数据传输速率

4 结 论

文中提出了一种基于OpenVPX标准的RapidIO总线存储模块设计方案,包括硬件设计、逻辑设计和软件设计,并设计了相应的测试环境对存储板性能进行测试,验证了该模块可在通信系统中提供高速率、大容量的存储功能。本设计具有很高的通用性,可以作为高性能数字信号处理系统中互连总线设计和数据存储设计的参考方案。

[1]王辉球.一种基于FPGA的Serial RapidIO交换设计[J].电子世界,2014(6):122.

[2]蔡叶芳,田泽,李攀,等.一种RapidIO IP核的设计与验证[J].计算机技术与发展,2014(10):97-100.

[3]徐维佳.基于FPGA的PCI Express与Rapid IO高速互连技术验证[D].西安:西安电子科技大学,2014.

[4]许树军,黄镠,牛戴楠,等.基于FPGA的SerialRapidIO协议的设计与实现[J].雷达与对抗,2015(4):36-38,49.

[5]步凯.基于RAID技术的固态存储阵列系统的研究与设计[D].长沙:国防科学技术大学,2008.

[6]陈剑波,侯卫民,蒋景宏,等.基于RapidIO技术的数据交换系统的设计与实现[J].计算机与网络,2014(12):46-49.

[7]刘云鹏.基于FPGA的RapidIO总线接口设计、验证与实现[D].西安:西安电子科技大学,2013.

[8]刘芳,于礼华,李方伟,等.基于FPGA的RapidIO总线技术研究与实现[A].天津市电子学会.第二十七届中国(天津)2013IT、网络、信息技术、电子、仪器仪表创新学术会议论文集[C].天津市电子学会:,2013:4.

[9]吴海燕.基于RapidIO总线的信号处理平台设计[D].成都:电子科技大学,2009.

[10]陈宏铭,李蕾,姚益武,等.基于AXI总线串行RapidIO端点控制器的FPGA实现[J].北京大学学报:自然科学版,2014(4):697-703.

[11]杨卿,杨万麟.基于串行RapidIO协议的无线通信基带处理系统架构[J].现代电子技术,2009(13): 103-105,115.

[12]Fuller S.RapidIO:The embedded system interconnect[M].2007.

[13]杨卿.RapidIO高速互联接口的设计研究与应用[D].成都:电子科技大学,2009.

[14]李宾,马晓川,鄢社锋,等.基于VPX标准的RapidIO交换和Flash存储模块设计[J].声学技术,2011(6): 528-532.

[15]RapidIO Trade Association[M].RapidIOTM interconnects pecification,Part 1:Input/output logical specification,Version 1.3.2005.

[16]方文崇,梁寿愚.基于FPGA的智能变电站实时监控系统高速视频数据传输[J].电子设计工程,2016(23):139-142.

[17]石炜,孟金芳.一种基于vxBus的PPC与FPGA高速互联的驱动设计方法 [J].电子设计工程,2015(24):139-141.

Design of VPX standard storage module based on RapidIO bus

LIU Xu-dong,CHEN Chen

(Technology and Engineering Center for Space Utilization,Chinese Academy of Sciences,Beijing 100094,China)

A design of storage module,based on VPX standard and RapidIO bus architecture,is proposed aiming at interconnect and data storage problem met in high-performance digital signal processing.The hardware and software of the module are realized.The board is designed according to VPX standard.The switch chip CPS1848 is using in RapidIO network.K7 FPGA and mSATA is using in a RapidIO interface storage board with 8TB capacity.Transplanting μcos-II system in MircoBlaze soft core.Writing software and operating procedure.Setting up a testing environment show that the data transfer speed of reading is up to 1.3GB/s and writing is up to 1.1 GB/s.Experiments shows that this design is advanced,realizable and stable,which can be used as a reference design of interconnect and data storage.

RapidIO;VPX;mSATA;data storage;AXI bus

TN91

A

1674-6236(2017)09-0141-04

2016-04-08稿件编号:201604074

刘旭东(1991—),男,内蒙古赤峰人,硕士研究生。研究方向:卫星测控与通信系统。