基于CPLD精确控制PWM死区时间的实现

2017-04-26孟雍祥吴清收

孟雍祥,吴清收

(山东科技大学 机械电子工程学院,山东 青岛 266590)

基于CPLD精确控制PWM死区时间的实现

孟雍祥,吴清收

(山东科技大学 机械电子工程学院,山东 青岛 266590)

针对采用分立元件逻辑电路生成的PWM死区时间的不精确和修改时不便利的缺点,文章介绍了一种基于可编程逻辑器件精确控制死区时间的设计实现方案。输入信号可由外部提供也可以由有源晶振分频获得,采用VHDL硬件描述语言可在线编程,输出两路互补带死区的PWM信号。该方案具有硬件电路结构简单,延时控制准确,抗干扰能力强的优势,很好地满足了实际工作的应用需求。

可编程逻辑器件;硬件描述语言;分频;PWM死区时间

1 研究背景

脉冲宽度调制技术(Pulse Width Modulation,PWM),即通过对一系列脉冲的宽度进行调制,来等效地获得所需要波形的一种技术。作为一种利用数字输出对模拟电路进行控制的非常有效的方法,PWM在测量、通信、功率变换等诸多领域中已经得到了广泛的应用。而在电力电子技术的整流和逆变中,带死区的PWM可以防止两个IGBT不会因为开关速度问题导致同时导通,避免了半桥元件因为没有及时关断而造成的功率元件烧毁。

在之前的PWM死区时间设计中,应用多个数字芯片的组合电路来输出带死区的PWM,通过调节电位器手动控制死区时间的长短。尽管控制方式直观简单,但硬件电路结构复杂,抗干扰能力差,保密性差,功耗高,且不能精确控制PWM死区时间。所以本研究采用Altera公司的MAX3000A系列的CPLD芯片(EPM3032ATC44-7)来实现对死区时间的精确控制。通过VHDL对不同的功能模块进行描述,修改程序可方便的修改死区时长,最终获得两路带死区的互补PWM输出。

2 电路组成与方案设计

本设计使用的软件是Altera公司的Quartus II ,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整设计流程。

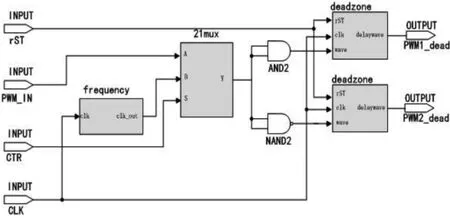

CPLD芯片内部逻辑总框图如图1所示。因为本设计的PWM死区控制有着不同的应用场合,所以设置了两种输入方式:一种是由外部输入的PWM_IN,用在有硬件电路板间级连的场合。另一种是外部48 MHz有源晶振通过CPLD内部分频模块(frequency)得到输入信号。48 MHz有源晶振同时作为芯片的外部时钟。硬件电路上设有上拉和下拉电阻控制选择模块(21mux)选择输入方式。rST为芯片使能引脚。死区控制模块(deadzone)应用VHDL硬件描述语言实现对输入的方波信号进行延时操作,最后输出带死区的两路互补PWM输出信号。若要改变输入信号的频率或者死区时长,只需修改分频模块和死区控制模块中的程序参数即可。

3 模块功能实现

图1 CPLD内部逻辑

3.1 输入选择模块

在输入选择模块21mux中,A,B为两路输入,S为选择控制端。当S端电平置高,即CPLD芯片外接上拉电阻时输出Y=A,选择PWM_IN作为输入。当S端为低电平,即CPLD芯片外接下拉电阻时输出Y=B,选择有源晶振分频方式输入。

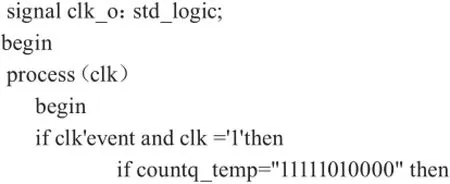

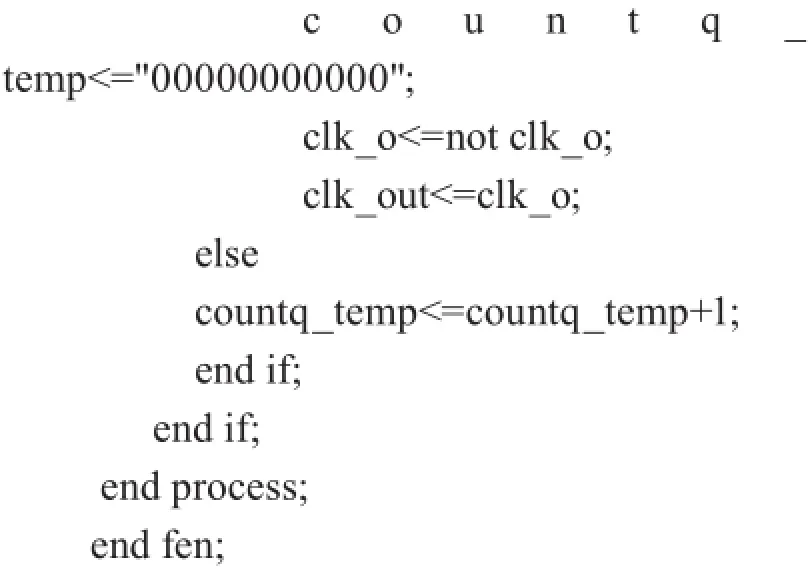

3.2 分频模块

分频模块即图1的frequency模块。在分频得到PWM输入的设计中,本研究采用十一位计数器,外接有源晶振为48 MHz。本研究应用场合需要的是12 kHz的PWM信号,所以对48 MHz有源晶振进行4 000分频。分频功能模块将会由调试成功后的VHDL程序通过软件生成。修改countq_temp的值便可更改输入信号的频率。

分频模块的VHDL程序设计如下所示:

architecture fen of frequency is

signal countq_temp: std_logic_vector(10 downto 0);

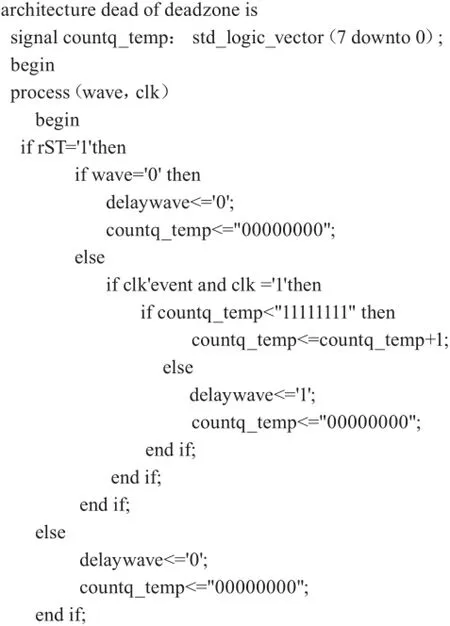

3.3 死区控制模块

两个死区控制模块即图1中的deadzone模块,模块输入为完全互补的PWM信号。在死区控制模块中,对输入信号wave上升沿延时输出,下降沿不进行操作。采用8位计数器,因为外部时钟为48 MHz,所以最长延时5.33 μs,即最大死区时长为5.33 μs,这样便得到了带死区的两路互补PWM信号。同样修改countq_temp的参数值便可得到不同的死区时长。

死区控制模块的VHDL程序设计如下所示:

4 软件仿真与硬件实现

4.1 软件仿真

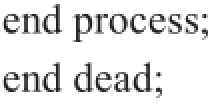

完成上述设计过程后,使用Quartus II自带的仿真器进行功能仿真。仿真结果如图2所示。

图2 软件仿真结果

本次仿真中,控制使能端rST取100 Hz方波,选择模块控制端CTR取1 kHz方波,PWM_IN输入为12 kHz方波,时钟CLK为48 MHz有源晶振。当使能端rST由高电平跳变到低电平,两路输出(PWM1_dead和PWM2_dead)均变为零。CTR控制着输入方式的选择。经过测量,生成的两路互补PWM的死区时长为5.3 μs。仿真结果和设计结果一致。

4.2 硬件实现

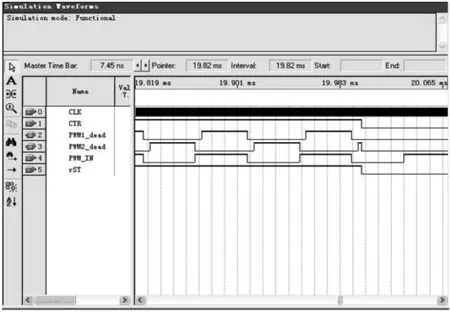

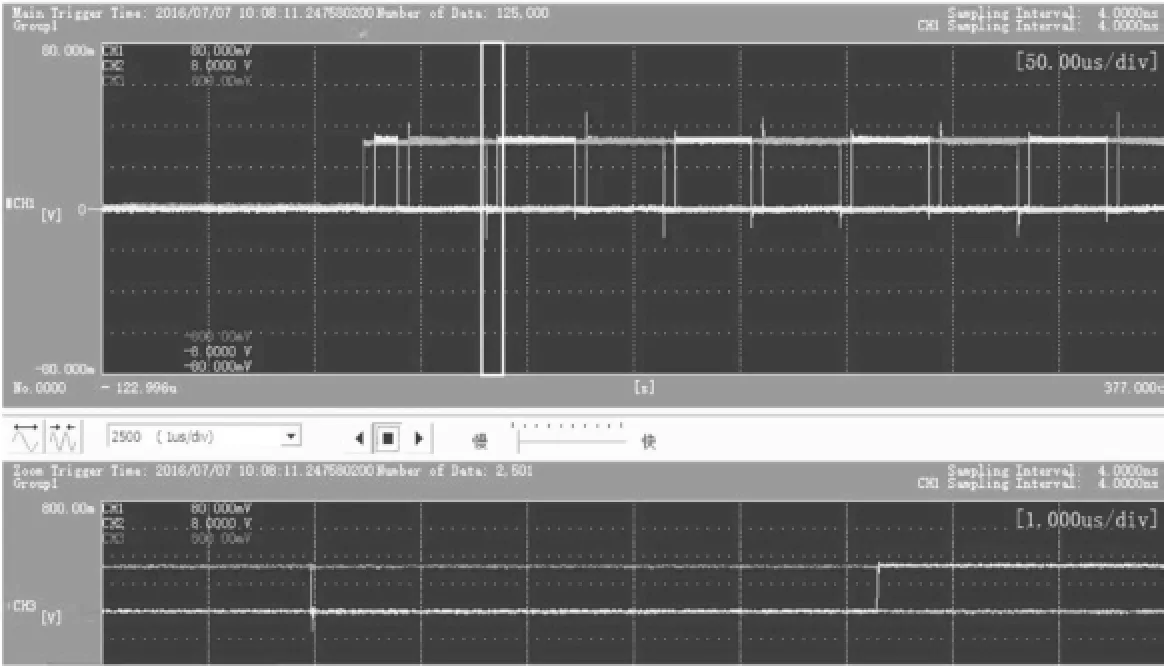

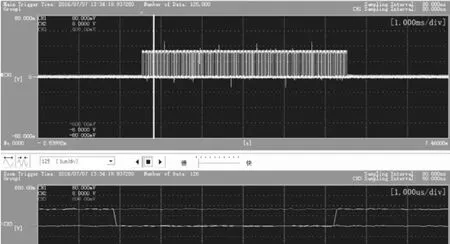

对PWM死区生成部分进行硬件电路焊接。首先在硬件电路上焊接上拉电阻,选择PWM_IN作为信号输入并观察两路输出信号波形,再换为下拉电阻选择有源晶振输入方式进行同样的波形观察。示波器的输出波形分别如图3—4所示,图3为PWM_IN作为输入的波形情况,图4为有源晶振分频作为输入的波形情况。

在图3—4的波形图中,CH1和CH2两通道为两路输出波形,紫色的CH3为所加的使能端rST波形。在图中下半部分每格代表1 μs,经测量死区时长为5.3 μs,与设计及仿真结果一致。

5 结语

本文通过理论设计,Quartus II仿真分析和硬件实现说明了基于CPLD芯片精确控制PWM死区时间的可行性。整个方案实现简单,死区时长控制精确,抗干扰能力强,达到了设计初期预想的效果。此方法可以针对不同的应用场合适时的调整CPLD的内部逻辑和VHDL语言控制来达到很好的应用效果,可以广泛运用在电力电子的整流、逆变过程和其他的场合中。

图3 PWM_IN输入,rST=100 Hz时的输出波形

图4 有源晶振作输入 rST=100 Hz时的输出波形

[1]王千文.EDA技术与VHDL程序开发教程 [M].北京:清华大学出版社,2014.

[2]周润景.VHDL数字电路设计实用教程[M].北京:北京航空航天大学出版社,2014.

[3]代金龙.基于VHDL语言和FPGA的电子密码锁[D].内蒙古:内蒙古大学,2015.

[4]赵鲁,李耀华,葛琼璇,等.单相PWM整流器死区补偿方法[J].电机与控制学报,2015(6):6-13.

[5]周俊鹏,李焱.机载平台下功率级驱动及PWM死区控制的研究[J].微特电机,2014(10):35-38.

[6]田生宏,田培成.可编程逻辑器件CPLD和FPGA的特点和应用[J].科技视界,2015(18):134-134.

[7]黄招彬,游林儒,汪兆栋等.一种考虑死区与最小脉宽限制的IPWM算法[J].电工技术学报,2014(12):11-18.

[8]孙保良.基于DSP2812和SVPWM控制的三相整流器研究[J].仪表技术,2015(1):48-50.

[9]庞佑兵,吕果,马朝骥.脉宽调制放大器死区技术研究[J].微电子学,2014(4):459-462.

[10]张明,肖波.基于CPLD的分频器设计与实现[J].工业控制计算机,2015(6):175-176.

Implementation of precisely controlling PWM dead-time based on CPLD

Meng Yongxiang, Wu Qingshou

(College of Mechanical and Electronic Engineering, Shandong University of Science and Technology, Qingdao 266590, China)

Focusing on the shortcomings:not accurate and not convenient of the PWM dead time generated by discrete components of the logic circuit,this article introduces an implementation of the design based on the programmable logic device’s precise control of dead time.The input signals can be provided by an external source or be obtained by dividing the crystal.And the description language of VHDL hardware can be online programming, outputting the PWM signals in two complementary dead zones. This scheme has a simple hardware circuit, accurate delay control and strong antiinterference ability which better meet the application requirements of the actual work.

programmable logic device; hardware description language; frequency division; PWM dead time

孟雍祥(1990— ),男,山东淄博,硕士研究生;研究方向:测试计量技术及仪器。

*通讯作者:吴清收(1969— ),男,山东临沂,副教授,硕士生导师;研究方向:测控技术。