基于ARM和FPGA的Sobel边缘检测异构系统

2017-04-15孙志豪徐政石润彬吴晨健

孙志豪+徐政+石润彬+吴晨健

摘要:为了实现直接对网络摄像监控系统进行视频画面抓取并进行高效率、高精度的图像处理,设计了一个支持RTSP协议、可进行Sobel边缘检测的数据驱动型异构系统。基于海思公司的hi3536芯片,该系统可同时获取16路1080P、H.264编码的网络摄像头的视频图像,并使用Xilinx公司的ZC702型号FPGA为载体实现的Sobel边缘检测加速器对视频图像进行实时处理。实验结果发现该系统获取视频图像的延迟很低,并且拥有对大量高清图像同时进行实时边缘提取的能力。

关键词:FPGA;网络摄像头;RTSP;Sobel;异构

中图分类号:TN911 文献标识码:A 文章编号:1009-3044(2016)34-0219-03

Abstract:In order to achieve high-efficiency, high-precision image processing for capturing the video stream of IP camera, a data-driven heterogeneous system with Sobel edge detection is designed to support RTSP protocol.The system can get 1080P, H.264 encoded video streams from sixteen IP cameras at the same time and also can process real-time Sobel edge detection of video streams base on arm from Hisilicon and ZC702 FPGA form Xilinx. Experimental results show that the system has low delay of capturing video streams and can real-time edge detection for a large number of high-definition images at the same time.

Key words:FPGA; IPC; RTSP; Sobel; heterogeneous

1 概述

实时图像处理是实现实时物体检测中的重要一环,其广泛应用于诸多领域,比如先进驾驶辅助系统(Advanced Driver Assistance System, ADAS)、工業机器人、智能安防等。图像处理技术的主要关键点是超高的实时性和结果的准确性。而边缘提取是图像处理中最基础的一步,由Irwin Sobel提出的Sobel算法又是众多边缘检测算法中较简单高效的一种,对噪声具有平滑作用[1],较为适合在嵌入式系统中应用。

异构处理系统是随着计算机技术的飞速发展出现的一种能够突破单一平台发展瓶颈,有效解决能耗高、扩展性低等问题的一种技术。近年来,基于CPU和GPU的异构图像处理系统应用正蓬勃发展。本文实现的Sobel边缘检测的异构系统是一种数据驱动(Data-Drivern)型图像处理应用系统。主要使用现场可编程门阵列(Field Programmable Gate Array, FPGA)对Sobel算法进行硬件实现,并对海思解码芯片hi3536为载体的开发板进行编程,使其能获取到网络摄像头(Internet Protocol Camra,IPC)的实时视频流,为硬件加速器提供数据。该系统的最高性能可达同时对16路1080P、60帧的视频进行边缘提取。

2 Sobel算法

在图像中边缘的像素值会发生显著的变化,表示这一变化的方法就是导数,所以一般我们用来寻找图像边缘的方法是对图像进行求导,即使用一个卷积核对图像进行平面卷积处理,这样可实现图像求导的近似计算。

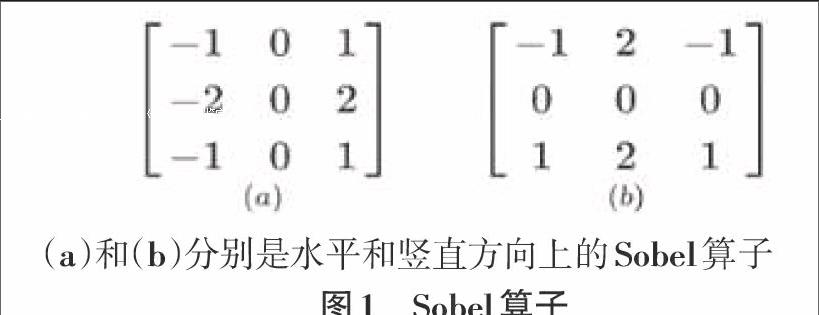

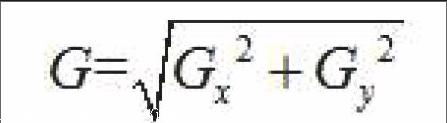

Sobel边缘检测算法在实现过程中,通过把检测水平边缘和竖直边缘的2个Sobel算子作为卷积核分别与图像中的每个像素点做卷积运算,分别得到该图像在水平方向上的梯度Gx和竖直方向上的梯度Gy。Sobel算子如图1所示。

对于图像上的每一个像素点,结合以上两个卷积处理后的结果可求出该点上的近似梯度:

我们也可以对其做出一个近似的转换:G = |Gx| + |Gy|。

梯度值的大变化预示着图像中内容的显著变化。可设定一个合适的阈值T,如果G≥T 就可以认为该点为边缘点。判别出图像中所有边缘点后,我们可以把输入的灰度图像转换为只包含边缘信息的二值化图像,即图上一点A(x,y),它的梯度值G(x,y)若大于等于阈值T,则将该点的值置为1;反之,则置为0。

2 图像边缘提取异构系统的实现

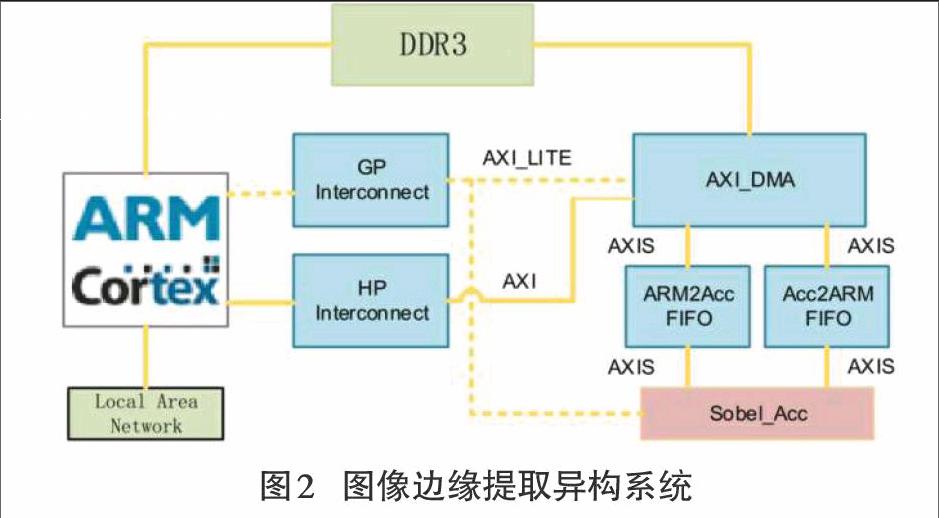

本异构系统由深圳海思公司的hi3536芯片和Xilinx公司的ZC702型号的FPGA组合搭建而成。hi3536芯片主要负责获取IPC的视频流数据并实时解码,FPGA主要负责对输入的图像进行Sobel算法的加速运算。通过使用本文编写的能够兼容大部分主流IPC的RTSP协议接口,再利用海思hi3536芯片的解码能力,完成最高可同时接收并解码16路H264或H265编码、分辨率为1080P60帧的实时视频流,再把解码后得到的YUV格式图像通过AXI-Stream总线直接传递到FPGA上的Sobel加速处理模块,实现从前端IPC进行数据采集后实时传递给硬件加速模块的完整链路。这样,使得整套系统更方便地接入到监控系统中,大幅提升系统的实用性。该模块整体的架构如图2所示。

2.1 基于ARM的前端数据采集模块

为了更加体现本异构系统的实用性,FPGA上的Sobel加速处理模块的图像输入并不是由上位机选送事先采集好一张或多张图片[2],而是采集于实际环境中的IPC。RTSP(Real Time Streaming Protocol,实时流媒体协议)[3] 是目前监控行业内广泛采用的流媒体协议,所以为了能够把我们的异构系统对接进绝大部分已存在的IPC监控系统,我们选用RTSP协议作为与IPC的对接接口。但由于现存的一些包含RTSP代码的开源项目存在图像延迟较高、图像质量不稳定以及代码可控性较差等问题,所以我们基于文献[3]和Ffmpeg[4]中的RTSP部分,编写了一个RTSP的客户端程序,并主要通过调整视频缓存块(Cache Block)和协议解析速度, 针对1080P视频流的传输延迟进行优化。使用本文编写的RTSP客户端代码,在不损失视频质量和视频流畅度的前提下,相比Ffmpeg等,大大降低了对RTSP协议解析和帧缓存带来的图像延迟,又提高了对视频流获取的可控性。在千兆局域网内,测试同时连接16路1080P、30fps(Frames Per Second,每秒传输帧数)的IPC,所有画面延迟都基本稳定在160ms到175ms之间,配合海思hi3536的强大解码性能,从IPC采集图像数据到传到Sobel加速处理模块,之间的延迟可稳定在200ms以内。

如图3是Ffmpeg中的RTSP客户端、本文中使用的RTSP客户端分别运行在电脑端和ARM端时,三者在画面延迟方面的对比结果。其中,Ffmpeg在使用时,调用了参数“-fflags nobuffer”,不做流缓冲。延迟测试方式为将一台运行着计时秒表的电脑主机A作为信号源接入到一台支持RTSP协议的H.264编码设备上,利用该编码设备将主机A的画面进行网络转播,再由接受测试的三种RTSP客户终端同时接收下视频流数据,各自解码后分别显示在三块显示器上。同时拍摄下三块显示器上的画面以及主机A直接输出的画面,再记录照片中四块显示器上的秒表读数,进行差值分析。由于海思hi3536芯片对H264、H265编码的视频流的高性能解码能力,所以在实际使用中不需要做任何的视频数据缓存,相比于在电脑端运行的本文RTSP客户端,进一步加快了视频流的实时性。

通过网络获取到的视频流是H264或H265编码的原始数据,如果需要对图像进行识别,至少需要把原始数据解码为YUV格式的图像数据。因为海思半导体公司在全球视频监控领域的核心地位[5],这里我们选用基于该公司型号为hi3536的解码专用芯片的开发板,板上具有全双工千兆网口,且对于1080P的图像分辨率最高的解碼性能是同时16路、60帧的H.264/H.265实时解码。通过研究海思芯片的SDK(Software Development Kit,软件开发工具包),结合经过交叉编译后的本文中的RTSP客户端函数库,编写了运行在ARM上的可接收IPC视频流的多线程解码程序,同时接收视频流数为可调参数,最大值不能超过16。解码后得到的就是YUV420格式的视频流。由于受限于海思解码芯片的能力,对于本程序,只测试了同时接收16路1080P视频流情况下的图像稳定性和画面延迟。测试结果证明本程序完全可以支持这种使用情况。而由于之后的图像处理需要的是YUV格式的灰度图像数据,本程序的最后部分,是对最多16路解码后的图像数据提取YUV中的Y分量,即亮度分量,将其通过AXI-Stream总线异步发送至FPGA上预先设计好并通过验证的Soble加速处理内核上。该前端数据采集模块整体的架构如图4所示。

2.2 基于FPGA的Sobel硬件加速处理模块

本异构系统在FPGA上实现Sobel边缘检测功能,并且输入图像的大小以及Sobel边缘提取的阈值T都是可配置的。该模块有下列几个主要部分:与ARM数据交互模块,数据接收模块,梯度计算模块和最后的阈值比较输出模块。如图5是Sobel加速处理模块的整体架构框图。各个模块均使用Verilog语言实现[6],并使用Synopsis公司的VCS工具进行功能仿真。该加速模块实现了数据驱动的工作方式,所谓数据驱动,指的是当系统处于工作状态时,只要有数据输入系统,Sobel加速处理模块就能够对输入的数据进行实时处理后输出结果,数据输入停止时,处理工作也会暂停。下面逐个介绍不同的功能模块

2.1.1 FIFO模块

与ARM的数据交互是通过AXI-Stream总线实现的[7],AXI-Stream总线是AXI4总线的简化版,而AXI4总线是由ARM公司研发推出的AMBA(Advanced Microcontroller Bus Architecture)片上总线。AXI-Stream总线由于整个通道只有数据传输通道,而不需要传输地址的通道,所以相对AXI总线来说要简便很多。我们使用AXI-Stream总线向ARM和DDR申请数据,这样就可以大大提高数据的传输效率。并且为了防止数据出现遗漏或者丢失,我们采用FIFO(First-In First-Out,先入先出)存储器去同步数据的信号。

Sobel加速处理模块被设计为数据驱动的工作形式,当系统被配置为工作模式时,只要AXI-Stream总线上有数据传输,加速器模块就会进行计算,这样减少了由上位机的控制和交互的时间成本。

2.1.2 数据排列模块

数据排列(Ram Array)模块用于接收数据并将其分别存放在不同的缓存中,方便后续的梯度计算模块进行数据的读取和并行计算。输入为AXI-Stream总线串行输入的数据流,输出的数据则被调整成便于梯度计算模块进行并行卷积计算的格式。同时,数据排列模块是一个可配置处理图像大小的模块,图像的长宽都可由上位机进行配置,这样使得整个系统处理的图像大小都是可控的。该模块所支持的最大图像分辨率为2048×2048。

2.1.3 梯度计算模块

梯度计算模块是一个进行卷积计算的模块。基于文献[8]中提出的方案,本文使用了并行计算的方式,并采用数据移位(shift)的方法进行乘法计算,左移一位即乘以2,这样可以大量减少硬件资源的使用,大幅提高Sobel边缘检测中水平方向和豎直方向的梯度向量的计算速度。该模块逻辑图如图5(b)所示。所以在这种计算结构下,使用3个时钟周期就可以计算出一个3×3卷积框中最后的梯度值,并将梯度值传输给阈值比较模块进行最后结果的运算。

2.1.4 阈值比较输出模块

从梯度计算模块输出的计算完的梯度值,会在阈值比较模块中与设定好的阈值T进行对比。并且在这个模块中存在一个状态机用于控制输出的值,如果梯度值大于等于阈值T,则输出1;反之输出0。由于卷积的原因,图像的长宽会分别下降1个像素点,所以为了使得上位机收到的还是规整的图片,我们还在这个模块中对这缺失的一行一列进行了补0操作,以保证最后输出图像的尺寸依旧与原图的尺寸相同。

如图6是对本文中的Sobel加速处理模块使用VCS工具进行行为级仿真得出的波形图。

3 结论

图像边缘提取是图像处理、物体识别中很重要的一环,本文以Sobel边缘提取为例,通过利用本文中编写的RTSP客户端协议和基于FPGA实现的Sobel硬件加速器,实现了一个通过网线就可接入到监控系统等各个拥有IPC的网络中,并对高画质视频流进行高实时性高精度的边缘提取的数据驱动型异构系统。本设计采用模块化的方式,且对接IPC的路数、图像分辨率等参数均为可调参数,并专门优化了硬件资源占用率。在实际测试中也达到了设计初时的目标,有助于进一步开发可接入监控系统的人脸识别、车牌识别等物体识别异构系统。

参考文献:

[1] Tsai M Y, Yost M G, Wu C F, et al. Line profile reconstruction: validation and comparison of reconstruction methods[J]. Atmospheric Environment, 2001, 35(28):4791-4799.

[2] 张丽红, 凌朝东. 基于FPGA的Sobel边缘检测应用[J]. 电子技术应用, 2011, 37(8):26-29.

[3] Schulzrinne H, Rao A, Lanphier R. Real Time Streaming Protocol (RTSP)[J]. Rfc, 1998.

[4] Surhone L M, Tennoe M T, Henssonow S F, et al. Ffmpeg[Z]. 2010.

[5] 康毅. 海思IVE技术开启智能视频监控新纪元[J]. 中国公共安全:学术版, 2014(22):204-204.

[6] 夏宇闻. Verilog数字系统设计教程[J]. 2003(6):51-51.

[7] He L, Zhao H, Shao L. FPGA Video System Based on AXI4-Stream Bus[J]. Microcontrollers & Embedded Systems, 2015.

[8] 朱学亮, 柴志雷, 钟传杰,等. 基于FPGA的图像卷积IP核的设计与实现[J]. 微电子学与计算机, 2011, 28(6):188-192.