胚胎型仿生自修复系统硬件消耗分析

2017-04-10孟亚峰朱赛韩春辉

孟亚峰 朱赛 韩春辉

摘 要: 胚胎型仿生自修复系统具有实时自修复能力,可用于高可靠性电子系统的设计。在设计过程中,其硬件消耗是工程师十分关心的问题。在分析胚胎型仿生自修复系统结构基础上,根据自修复过程特征,建立了其系统硬件消耗模型。并以三模冗余自修复系统为对比,对胚胎型仿生自修复系统的硬件消耗进行了仿真分析。分析表明,胚胎型仿生自修复系统在大规模、高自修复能力的电路设计中具有优越性,且通过电子细胞辅助电路的优化设计,可以降低自修复过程中的硬件消耗。

关键词: 电子细胞辅助电路; 胚胎电子阵列; 硬件消耗; 自修复能力

中图分类号: TN911?34; TP302.8 文献标识码: A 文章编号: 1004?373X(2017)06?0129?04

Abstract: The embryonic bio?inspired self?repairing system has the real?time self?repairing ability, and can be used in the design of the electronic system with high reliability. On the basis of analyzing the structure of the embryonic bio?inspired self?repairing system, the system hardware consumption model was established according to the characteristics of the self?repairing process. In comparison with the triple?modular redundancy self?repairing system, the simulation analysis for the hardware consumption of the embryonic bio?inspired self?repairing system was performed. The analysis results show that the embryonic bio?inspired self?repairing system has superiority in the design of the large?scale circuit with high self?repairing capacity, and can reduce the hardware consumption in the self?repairing process by means of the optimization design of the electronic cell auxiliary circuit.

Keywords: electronic cell auxiliary circuit; embryonic array; hardware consumption; self?repairing ability

0 引 言

胚胎型仿生自修复系统是受多细胞生物体结构和胚胎发育过程启发提出的一种仿生硬件[1?2],与生物体类似,具有自检测、自修复能力,可用于航空、航天等领域及复杂电磁环境下高可靠性电子设备的设计。

胚胎型仿生自修复系统自提出以来,研究者对其系统结构[3?5]、自修复机制[6?7]、自修复实验[8]等方面进行了深入研究,提出了多种系统结构框架[9?12],并实现了小规模电路的自修复实验。利用胚胎型仿生自修复系统进行电路设计时,在一定自修复能力下,系统硬件消耗是电子工程师十分关心的问题。学者对胚胎型仿生自修复中的硬件消耗研究较少,缺少系统层面的硬件消耗分析,无法指导胚胎型仿生硬件的应用及研究。

本文根据胚胎型仿生自修复系统结构及其自修复原理,建立了系统自修复实现中的硬件消耗模型,并与经典的三模冗余系统进行了硬件消耗对比。通过分析,明确了胚胎型仿生自修复系统的应用范围,对胚胎型仿生自修复系统的设计和应用具有指导意义。

1 胚胎型仿生自修复系統基础知识

1.1 胚胎型仿生自修复系统

胚胎型仿生硬件是由结构相同的电子细胞排列而成的均匀二维阵列,因此也被称为胚胎电子阵列,其结构如图1所示[13]。胚胎电子阵列中的每个电子细胞都是具有一定数据处理能力的逻辑单元,由地址产生器、基因库、I/O单元、逻辑单元和自检测单元(Build?In Test, BIT)组成。地址产生器用来计算细胞在电路中的位置,产生细胞在电路中的惟一标识,细胞通过该标识表达对应基因,执行特定的功能;基因库存储整个电路的所有基因,不同的基因代表不同的电路功能及细胞连接方式;I/O单元进行细胞与周围细胞的连接控制,在表达基因配置下控制细胞与阵列中其他细胞的信号交互;逻辑单元执行细胞的逻辑功能,在不同的表达基因配置下执行不同的逻辑功能;BIT在细胞运行过程中实时检测细胞状态。

阵列中每个细胞根据自身位置表达基因库中的特定基因,确定I/O单元连接方式及逻辑块执行的逻辑功能,整个阵列的细胞一起完成目标电路功能。运行过程中,细胞内的BIT模块实时检测细胞状态,检测到细胞故障时,对外发出细胞故障信号触发修复机制,移除故障细胞,消除故障对目标电路的影响。剩余细胞重新计算位置并更新表达基因,执行新的细胞功能及连接。通过故障细胞的移除和正常细胞的替代,阵列上目标电路功能得以维持,完成胚胎电子阵列上目标电路的自修复。

1.2 自修复过程及自修复能力

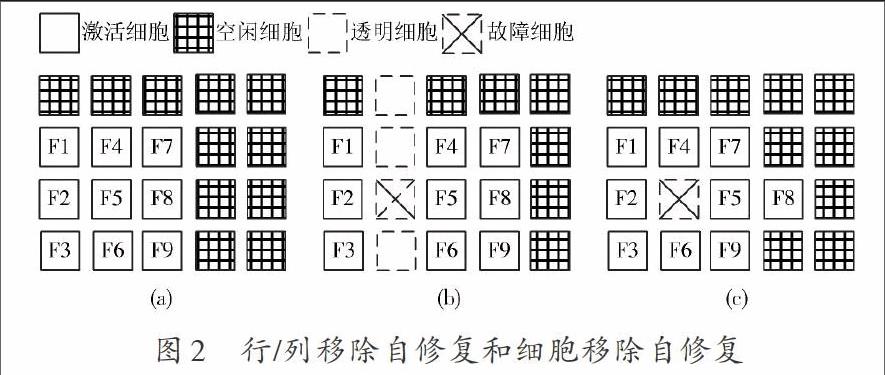

胚胎型仿生自修复系统通过移除故障细胞,消除故障对目标电路的影响,从而完成自修复。根据移除故障细胞的方式不同,其自修复方式主要为行/列移除自修复和细胞移除自修复,如图2所示。

行/列移除自修复指当胚胎电子阵列中某个电子细胞发生故障后,移除故障电子细胞所在的整行/列电子细胞,故障细胞所在行/列及其后所有激活行/列的功能向后移一行/列,直至最后使用一个空闲的行/列,如图2(b)所示。细胞移除自修复指当阵列中某个细胞单元故障后,移除该故障细胞,并将该行/列内故障单元细胞及位于故障单元后的细胞单元的功能后移,直至使用该行/列内的空闲细胞,如图2(c)所示。电路的自修復能力(Self?Repair Capacity,SRC)是系统自修复的重要指标,表征了电路能够从故障状态修复到正常状态的能力。对于移除自修复模式来说,电路的自修复能力即为胚胎电子阵列中冗余行/列资源的数目。

2 硬件消耗建模

根据胚胎电子阵列和经典的N模冗余自修复特点,考虑自修复过程中自修复能力指标,进行了硬件消耗的建模。

2.1 胚胎电子阵列与FPGA结构比较

FPGA与胚胎电子阵列结构相似,由许多独立的可编程逻辑模块CLB(Configurable Logic Block)排成阵列组成,用户通过可编程的互连资源将这些模块连接起来构成任何复杂的逻辑电路。

当前使用FPGA进行目标电路设计时,电路映射到FPGA基本单元CLB上。CLB中包含多个Slice,每个Slice中包括两个LUT、两个触发器和相关逻辑,不同的CLB间通过开关盒进行连接。

胚胎电子阵列进行目标电路的实现时,与FPGA类似,目标电路映射到电子细胞上,电子细胞由LUT,FF,开关盒和基因存储模块、自检测模块等组成。在硬件消耗上,相当于在FPGA基本单元上增加了基因存储模块、自检测模块及控制模块。

为了在相同级别上验证目标电路的硬件消耗,分别在设计的FPGA阵列上和胚胎电子阵列上进行目标电路的实现。两种阵列的功能模块、开关盒结构相同,阵列上目标电路实现方式相同。

2.2 硬件消耗模型

假设某电路由m×n个基本单元组成,每个单元消耗为ω。电子细胞在每个功能单元的基础上增加了基因存储、自检测及修复控制电路,设所增加的辅助电路与原电路的硬件消耗比为α,其值大小取决于电路设计水平及自检测中故障覆盖率。则电路由基本逻辑单元组成时,其硬件消耗为mnω;电路由电子细胞实现时,其硬件消耗为mnω(1+α)。

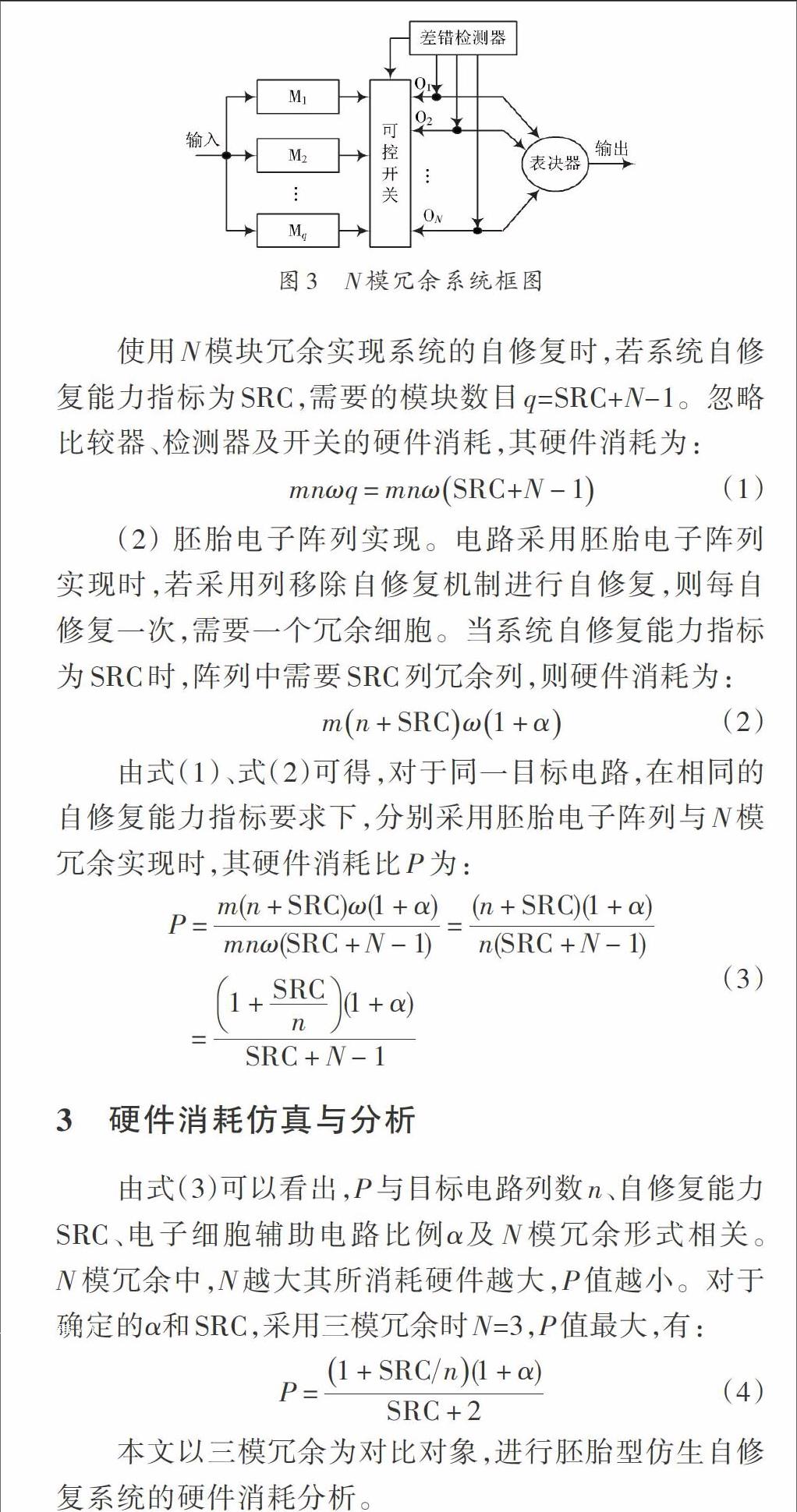

(1) N模冗余实现。电路采用N模冗余实现时,q个完全相同的模块M1,M2,…,Mq通过可控开关选择N个模块工作,工作模块的输出O1,O2,…,ON通过差错检测器检测模块状态,并使用表决器确定系统的输出,其结构如图3所示。当检查到N个工作模块中存在故障模块时,可控开关将故障模块断开,使故障模块不影响电路的最终输出,并选择冗余模块进行工作,保证同时有N个正常模块工作。

使用N模块冗余实现系统的自修复时,若系统自修复能力指标为SRC,需要的模块数目q=SRC+N-1。忽略比较器、检测器及开关的硬件消耗,其硬件消耗为:

[mnωq=mnωSRC+N-1] (1)

(2) 胚胎电子阵列实现。电路采用胚胎电子阵列实现时,若采用列移除自修复机制进行自修复,则每自修复一次,需要一个冗余细胞。当系统自修复能力指标为SRC时,阵列中需要SRC列冗余列,则硬件消耗为:

[mn+SRCω1+α] (2)

由式(1)、式(2)可得,对于同一目标电路,在相同的自修复能力指标要求下,分别采用胚胎电子阵列与N模冗余实现时,其硬件消耗比P为:

[P=m(n+SRC)ω(1+α)mnω(SRC+N-1)=(n+SRC)(1+α)n(SRC+N-1) =1+SRCn(1+α)SRC+N-1] (3)

3 硬件消耗仿真与分析

由式(3)可以看出,P与目标电路列数n、自修复能力SRC、电子细胞辅助电路比例α及N模冗余形式相关。N模冗余中,N越大其所消耗硬件越大,P值越小。对于确定的α和SRC,采用三模冗余时N=3,P值最大,有:

[P=1+SRCn(1+α)SRC+2] (4)

本文以三模冗余为对比对象,进行胚胎型仿生自修复系统的硬件消耗分析。

3.1 固定辅助电路比的硬件消耗

当目标电路列数n在[10,100]上、自修复能力SRC在[1,20]上变化,电子细胞辅助电路比例α分别为0.2,1.0,2.0,3.0,4.0,5.0时,P随n和SRC的变化如图4所示。由图4可以看出,胚胎电子阵列与N模冗余实现同一目标电路时,硬件消耗比P随着电子细胞辅助电路比例α的增加而增加,随着目标电路列数n和自修复能力SRC的增加而降低。在相同的电子细胞设计水平下,目标电路规模越大、自修复能力越大,P值越小,胚胎电子阵列的优势越明显,这是由于胚胎电子阵列与N模冗余的自修复特点不同决定的。N模冗余中将故障模块整块移除,而胚胎电子阵列中只移除故障细胞所在列,因此胚胎电子阵列在大规模、大自修复能力要求的环境下优势更加突出。对于相同规模和自修复能力要求的目标电路,α越大,P值越大,且对规模较小、自修复能力要求较低的电路影响较大。当[α≥2.0]时,对于规模[n≤20]、自修复能力[SRC≤5]的目标电路有[P≥1.0],此时,胚胎电子阵列的硬件消耗大于三模冗余的硬件消耗。但是对于规模[n≥20]、自修复能力[SRC≥10]的目标电路,即使[α=5.0],即电子细胞中辅助电路是细胞功能电路的5倍,P值依然小于1,即胚胎电子阵列与三模冗余相比依然具有优势。

3.2 固定电路规模的硬件消耗

为了进一步研究电子细胞辅助电路比例α对P的影响,当α在[1,20]上、自修复能力SRC在[1,20]上变化,目标电路列数n分别为10,20,30,50,100,200时计算胚胎电子阵列和三模冗余消耗硬件比例P,计算结果如图5所示,图5中黑色线条为[P=1.0]对应位置。

由图5可以看出,在相同的辅助电路比α和电路自修复能力SRC要求下,目标电路规模n越大,P值越小。同时,n越大,使[P<1.0]的α和SRC取值范围越大。当[n=200]时,即使辅助电路比[α=20],即电子细胞中检测、基因存储、修复控制电路规模是逻辑功能规模的20倍,对于自修复能力[SRC>20]的应用场合,胚胎电子阵列实现依然有硬件优势。

当目标电路规模较小时,如[n=10],使[P<1.0]的α和SRC取值范围较小。此时若[α>5],即电子细胞中检测、基因存储、修复控制电路规模是逻辑功能规模的5倍,则胚胎电子阵列相对于三模冗余没有硬件优势。

通过对图4和图5的分析可知,对于大规模、自修复能力要求高的目标电路,使用胚胎电子阵列实现时更具有优势。同时,电子细胞中检测、基因存储、修复控制等辅助电路的设计影响胚胎电子阵列的硬件消耗和应用范围,辅助电路比越低,胚胎电子阵列可应用范围越大。在胚胎电子阵列设计过程中,应尽量优化电子细胞设计,降低辅助电路比。

4 结 语

根据胚胎型仿生自修复系统中基本单元——电子细胞的结构特点,并结合其列移除自修复机制,建立了系统硬件消耗模型。在该模型基础上,对基于胚胎型仿生自修复系统的电路硬件消耗进行了分析。分析表明胚胎型仿生自修复系统适用于大规模目标电路、可靠性要求高的应用环境。对于目标电路规模较小、自修复能力要求较低的应用,胚胎型仿生自修复系统与传统的三模冗余相比,在硬件消耗上没有优势。另外,仿生电子系统的硬件消耗与电子细胞的设计水平紧密相关,通过优化电子细胞设计,可以有效降低系统硬件消耗。

参考文献

[1] DE GARIS H. Genetic programming: artificial nervous systems, artificial embryos and embryological electronics [C]// Proceedings of the 1st Workshop on Parallel Problem Solving from Nature. London: Springer, 1990: 117?123.

[2] DE GARIS H. Artificial embryology: the genetic programming of an artificial embryo [M]. New York: Wiley, 1992: 373?393.

[3] MANGE D, SANCHEZ E, STAUFFER A, et al. Embryonics: a new methodology for designing field?programmable gate arrays with self?repair and self?replicating properties [J]. IEEE transactions on very large scale integration (VLSI) systems, 1998, 6(3): 387?399.

[4] THOMA Y, TEMPESTI G, SANCHEZ E, et al. POEtic: an electronic tissue for bio?inspired cellular applications [J]. Biosystems, 2004, 76(1): 191?200.

[5] BREMNER P, LIU Y, SAMIE M, et al. SABRE: a bio?inspired fault?tolerant electronic architecture [J]. Bioinspiration & biomimetics, 2013, 8(1): 1?17.

[6] 张砦,王友仁.基于可靠性分析的胚胎硬件容错策略选择方法[J].系统工程理论与实践,2013,33(1):236?242.

[7] ZHU S, CAI J Y, MENG Y F. A novel embryonics system with evolutionary ability [J]. WSEAS transactions on circuits and systems, 2015, 14: 164?173.

[8] 朱赛,蔡金燕,孟亚峰,等.用于胚胎电子阵列的实验系统[J].电光与控制,2015,22(4):70?74.

[9] YANG I, JUNG S H, CHO K H. Self?repairing digital system with unified recovery process inspired by endocrine cellular communication [J]. IEEE transactions on very large scale integration (VLSI) systems, 2013, 21(6): 1027?1040.

[10] 李岳,王南天,钱彦岭.原核细胞仿生自修复电路设计[J].国防科技大学学报,2012,34(3):154?157.

[11] 徐佳庆,窦勇,吕启,等.电子组织:一种具有自适应能力的可重构仿生硬件结构[J].计算机研究与发展,2012,49(9):2005?2017.

[12] 郝国锋,王友仁,张砦.可重构硬件芯片级故障定位与自主修复方法[J].电子学报,2012,40(2):384?388.

[13] ZHU S, CAI J Y, MENG Y F, et al. A novel embryonics electronic cell array structure [J]. WSEAS transactions on circuits and systems, 2014, 13: 224?232.