基于VHDL设计的FPGA功能仿真结果与实际功能不一致问题研究

2017-04-08金臻姜丽梅

金臻++姜丽梅

摘要:在FPGA设计过程中,功能仿真(前仿真)使用EDA工具将硬件描述语言(设计源代码)用仿真器解析并进行功能验证,而设计中则采用的芯片厂商的工具进行综合及布局布线,两者对硬件描述语言的解析采用的工具不同,可能会导致对代码的理解不一致,仿真结果与实际设计功能不一致。在使用VHDL进行FPGA设计时,当对时钟信号进行赋值后,在本文的情况下,目前主流EDA工具在信号赋值语句的解析实际设计均不一致,在FPGA设计过程中应尽量避免使用该类语法,仿真验证过程中应对此予以关注。

关键词:FPGA;VHDL;功能仿真;综合;布局布线

中图分类号:TM13 文献标识码:A 文章编号:1007-9416(2017)02-0111-03

1 引言

当前的FPGA设计流程一般都是通过EDA[1]开发软件和编程工具对FPGA芯片进行开发,开发流程通常包括电路设计与输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真、板级仿真与验证、调试与加载配置等主要步骤[2]。其中每个步骤所采用的EDA工具都不尽相同。

由于功能仿真的工具和综合布局布线的工具不同,本文从一个功能仿真与综合布局布线结果不一致的例子引出了对VHDL代码中可能引起功能仿真结果不正确的原因的分析。

2 功能仿真、综合、布局布线的基本目的和常用工具

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证[3]。功能仿真的主要目的是确定一个设计是否实现了预定的功能或设计意图,分析电路的逻辑关系的正确性[4],由于仿真速度快,可以根据需要观察电路输入输出端口和电路内部任意信号和寄存器的波形,因此功能仿真是设计过程中不可缺少的步骤。目前功能仿真常用的EDA工具为Mentor公司Modelsim/QuestaSim、Sysnopsys公司的VCS和Cadence公司的NC等软件。

综合是将RTL级的行为描述转化为使用门级单元的结构描述[5]即网表。网表文件主要记录的是所用工艺库门级单元之间的互连关系(即门级结构)。而布局布线则是对网表中的每一个门级单元在器件中定位(布局) , 并使用器件内的连线资源按照网表中的连接关系连接起来(布线)的操作[4]。因为综合和布局布线将软件设计与硬件的可实现性挂钩,是将软件转化为硬件电路的关键步骤[6]。由于综合和布局布线与FPGA底层资源关系紧密,根据采用的芯片不同,一般设计人员采用各个FPGA厂家自己推出的综合开发工具。

3 功能仿真结果与实际功能不一致案例

在对某个采用VHDL编写的FPGA设计进行功能仿真和硬件调试中发现两者结果不一致的情况。分析结果发现硬件功能与设计意图一致,而功能仿真发生错误。设计代码可简化如图1。

根据代码分析设计意图为:时钟信号CLKA在该设计中进行了被赋值给了sys_clk信号,即将信号CLKA重命名为sys_clk,用重命名后的时钟信号sys_clk对Gate信号进行延迟1个时钟周期产生信号Gate_r。而使用VCS仿真结果如图2所示。

用sys_clk信号对时钟CLKA信号产生的Gate信号进行延迟时,仿真器显示Gate_r与Gate信号波形一致;同时将Gate信号进行赋值,则Gate_wr信号为Gate_w延迟1个时钟,与设计意图不一致。

4 不一致原因分析

分析代码发现,由于在设计中对时钟信号进行了赋值(重命名),导致该时钟产生的信号用赋值后的时钟进行延时处理时,第一个节拍的延迟未起作用,仿真的信号比实际信号在该处提前一个时钟周期跳变,仿真功能与实际设计不一致。

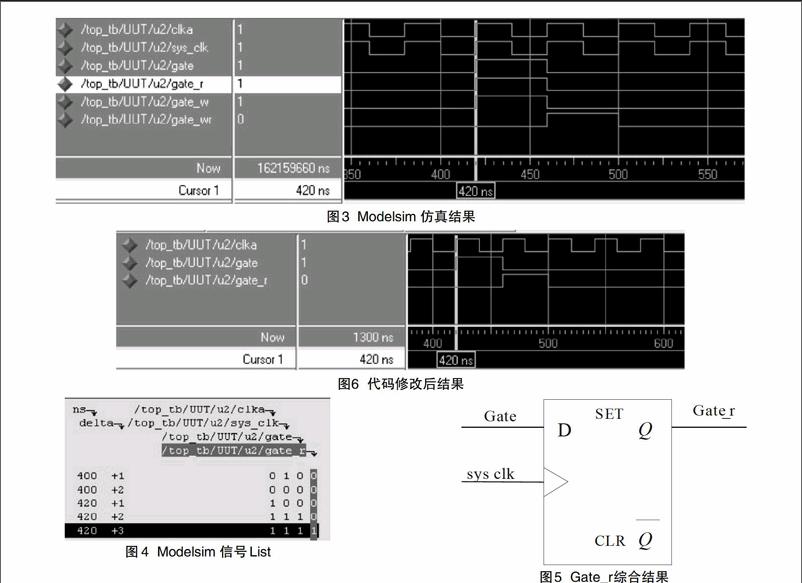

我们试用Modelsim仿真发现,仿真结果与VCS仿真结果一致(图3)。根据VHDL信号语法特性结合仿真器工作原理分析如下:

(1)在VHDL中,在进程(process)外的信号赋值有一定的延时[7],在仿真是对应于在等式右边的信号值跳变后的delta时间后;

(2)在进程(process)内信号的赋值在进程结束时起作用[8];

(3)仿真中,时钟上升沿判断后也会产生一个delta时间;

(4)仿真中,进程(process)内信号的时钟边沿赋值是将时钟信号跳变时刻等式右侧的信号值在时钟跳变后的delta时间赋值给左侧的被赋值信号;

打开仿真器的List信号分析信号跳变过程(图4),针对图2的设计代码分析如下,

(1)CLKA的跳变产生了第一个delta时间(420ns + 1);

(2)由于代码中的赋值语句“sys_clk<=CLKA”仿真过程多了个delta时间(420ns +2),因此process外的信号sys_clk在420ns +2处由0跳变为1;

(3)而process 中的时钟边沿赋值Gate<=1 也在CLKA上升沿后的delta时刻(420ns +2)将CLKA上升沿跳变时刻(420ns + 1)的1赋值给Gate。

(4)对于process 中的时钟边沿赋值Gate_r<=Gate,赋值发生在时钟信号sys_clk上升沿跳变时刻(420ns+2)后的delta时间(420ns+3),而在仿真器发现在sys_clk由0跳变为1的420ns +2时刻,Gate =1,所以在420ns +3时刻,Gate_r被赋值为1。

尽管Gate_r的跳变晚于Gate,但仅晚了一个delta时间,不占用仿真时间,所以导致了从波形仿真結果看Gate_r与Gate同时跳变的现象。

而对以上代码使用芯片厂商开发工具进行综合和布局布线,很显然,Gate_r在时钟sys_clk的赋值将被综合成触发器(如图5),sys_clk的赋值(重命名)将被综合成线连接,sys_clk等同于CLKA。从硬件实现看,Gate_r实际布局布线后将晚于Gate一个时钟周期而不是一个仿真用的delta时间。因此,功能仿真结果和布局布线后实际功能不一致。

5 纠正措施分析

根据上面的机理分析,对于本段代码,以下两个方法均可以使得功能仿真与设计一致:

方法一:将设计中的Gate_r的赋值条件由sys_clk改为CLKA时,仿真结果与预期结果一致,再次观察Modelsim信號List,可见由于少了时钟赋值语句,420ns处未出现420 +3时刻,Gate_r的赋值发生在时钟信号CLK从0跳变为1且Gate=1(460ns + 1)时刻后的delta时间(460ns +2),功能与设计一致。

方法二:对Gate信号也同时进行一次赋值产生Gate_w信号,在process中依然将该信号用sys_clk上升沿采样赋值,则Gate_wr信号为Gate信号延迟一个时钟周期。仿真波形如图5所示,观察仿真器的信号List,可以发现,仿真过程和上一种改法是不一致的。仿真器依然产生了420ns +3时刻,但由于Gate_w信号的跳变在420 +3时刻发生,Gate_wr信号的跳变依然晚于Gate信号一个时钟周期,在460 +3时跳变,因此仿真结果与设计实际要求一致。

6 结语

根据VHDL中对于信号赋值的延时特性,仿真器的原理严格按照VHDL语法进行,而厂商的综合布局布线工具却更加考虑到底层电路的特性。因此在基于VHDL的FPGA设计中,对时钟信号的赋值在因为VHDL语法种信号赋值特性的原因可能会造成仿真器的解析与期望不一致的情况。经测试,这种解析方式为仿真器EDA厂商的一致做法,我们利用手上多个版本的VCS和Modelsim均无法避免这种现象的发生。同时,由于verilog语法中,进程外的信号赋值仅相当于重命名操作,不存在延时,故此类问题在verilog的仿真中不会出现。

对于FPGA设计人员,在VHDL设计中应特别注意避免对时钟信号的赋值操作,以免出现为了功能仿真的结果正确性改动代码后导致实际功能错误的情况。

在FPGA的验证工作中,由于没有有效的自动检测手段,在分析VHDL代码时,验证人员也应重点注意设计代码中有没有对时钟赋值操作,以及该操作会不会影响功能仿真结果,避免漏测问题或者误测问题,必要时进行综合后仿真或布局布线后仿真对功能仿真结果进行确认。

参考文献

[1]梁丽.EDA技术在现代电子设计中的应用研[J].科技创新与应用,2016(35),66-67.

[2]蒋昊,李哲英.基于多种EDA工具的FPGA设计流程[J].微计算机信息,2007,23(11-2):201-203.

[3]戚新宇.基于FPGA 设计的功能仿真和时序仿真[J].航空电子技术,2005,36(03):51-54.

[4]程耀林.FPGA的系统设计方法解析[J].电子技术,2005(19):91-93.

[5]杨之廉,申明.超大规模集成电路设计方法学导论[M].北京:清华大学出版社,2000.

[6]潘松.电子设计自动化(EDA)技术及其应用(一)[J].电子与自动化,2000(1):52-55.

[7]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安电子科技大学出版社,1999.

[8]杨丹.VHDL中的信号与变量[J].电子工程师,2006,32(11):53-55.