一种低功耗高效率的双向AXI2AHB总线桥设计与实现

2017-03-02焦龙涛

焦龙涛,高 欣

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国人民解放军63916部队,北京 100089)

一种低功耗高效率的双向AXI2AHB总线桥设计与实现

焦龙涛1,高 欣2

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国人民解放军63916部队,北京 100089)

为了方便不同IP(intellectual property)核之间通信,针对广泛使用的AXI与AHB这2种总线,提出了一种低功耗高效率的双向AXI2AHB总线桥的设计与实现方法。介绍了这2种总线协议的特点,阐述了AXI2AHB总线桥的设计结构和实现方法,并采用多事务处理、写数据预读策略以及低功耗优化技术。使用Verilog语言在modelsim工具下进行了验证,仿真结果表明该总线桥能较大提高SoC芯片的系统带宽利用率并降低芯片产生的功耗。

AXI总线;AHB总线;总线桥;双向;低功耗

0 引言

为了使基于不同总线的IP核之间能够进行数据传输,必须使用总线桥来完成总线协议转换。针对目前ARM公司的AMBA3.0总线规范中的AXI与AHB总线,旨在构造一个AXI总线与AHB总线之间的双向通路,设计出双向AXI2AHB总线桥,该双向总线桥实现了多个AXI设备与多个AHB设备之间的相互访问,并且采用多事务处理、写数据预读策略以及低功耗优化技术,使之性能更佳、功耗更低[1-3]。

1 AXI、AHB总线及总线桥概述

AXI总线协议是ARM公司提出的AMBA3.0协议中核心部分,它是面向高性能、高频率和高带宽的系统设计。采用独特分离的地址、控制和数据通道,支持非对齐的数据传输和乱序访问。基于猝发的传输方式,启动传输时只需首地址,再加上对读、写和地址/控制通道的有效利用,能使系统以更小的面积获得更高的性能和效率[4]。

AXI总线具有以下特点:① 单向通道体系结构。数据流在通道中以单方向传输,简化了数据双向传输的等待时间,显著提高了带宽利用率。② 支持多项数据交换。通过并行和乱序访问猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,既可以满足高性能要求,同时也减少了系统功耗。③ 分离的地址和数据通道。将地址和数据通道分离,可以单独对每一个通道进行优化,通过对时序通道的控制,可将时钟频率提到最高,并将信号时延降到最低[5]。

AHB总线是ARM公司推出的主要用于高性能IP之间连接的总线,数据总线宽度支持32位~128位。AHB总线有效支持了处理器、直接储存器、外部储存器和低功耗外设接口之间的连接,具有猝发传输、分块处理、单时钟沿操作和更宽的数据总线架构等特点。AHB总线传输为地址/数据分离的二级流水线操作,通过从设备驱动的HRESP和HREADY应答信号控制数据操作的等待周期长度[6-7]。

总线桥的目的就是实现不同总线之间的协议转换,它具有2种含义:① 通过实现总线桥两侧不同总线接口信号之间的转换,完成不同总线标准之间接口信号的匹配;② 通过对总线桥两侧总线接口信号的时序调整,以符合相应总线标准的时序规范[8]。通过使用总线桥可以有效解决IP核直接接入系统总线所造成2个缺点:① 不同IP的工作频率不同,会加大系统架构的复杂度,降低系统总线的工作效率;② IP的带宽不同,容易造成带宽资源浪费。这样不同总线之间就能够更顺利地进行数据交换和相互通信。

2 双向AXI2AHB总线桥的设计

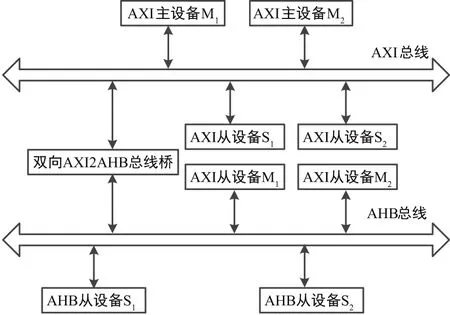

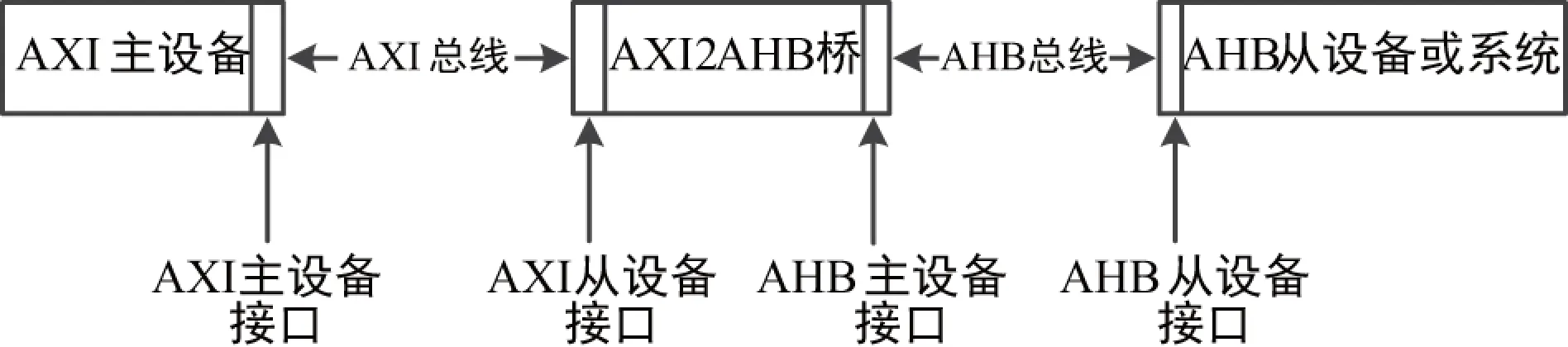

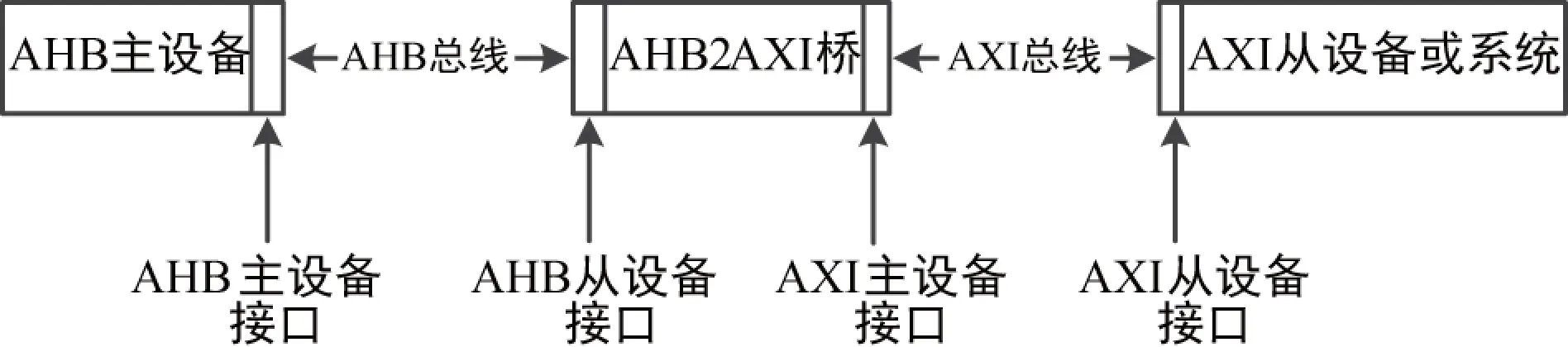

AXI2AHB总线桥在SoC中的位置如图1所示。从图中可以看出,通过双向AXI2AHB总线桥,可以实现AXI(AHB)主设备访问AHB(AXI)从设备。双向AXI2AHB总线桥作为AXI(AHB)总线的从设备,当AXI(AHB)总线主设备进行数据传输时,由双向AXI2AHB总线桥内部的主设备模块决定读或写AHB(AXI)总线连接的从设备,其内部结构如图2和图3所示。

图1 双向AXI2AHB总线桥在系统中的位置

图2 单向AXI2AHB总线桥架构

图3 单向AHB2AXI总线桥架构

从功能上讲,双向总线桥可以分成2部分:① 单向AXI2AHB总线桥从设备将接收到的AXI协议信号转换成AHB协议信号,通过总线桥主设备外接AHB总线,如图4所示;② 单向AHB2AXI总线桥从设备将接收到的AHB协议信号转换成AXI协议信号,通过总线桥主设备外接AXI总线,如图5所示[9]。

图4 AXI到AHB总线的接口转换

图5 AHB到AXI总线的接口转换

3 双向AXI2AHB总线桥的实现

AXI主设备对AHB从设备进行访问,双向AXI2AHB总线桥则将AXI主设备的输出信号转换为AHB从设备的输入信号,AHB从设备的输出信号转换为AXI主设备的输入信号;AHB主设备对AXI从设备进行访问,双向AXI2AHB总线桥则将AHB主设备的输出信号转换为AXI从设备的输入信号,AXI从设备的输出信号转换为AHB主设备的输入信号[10]。

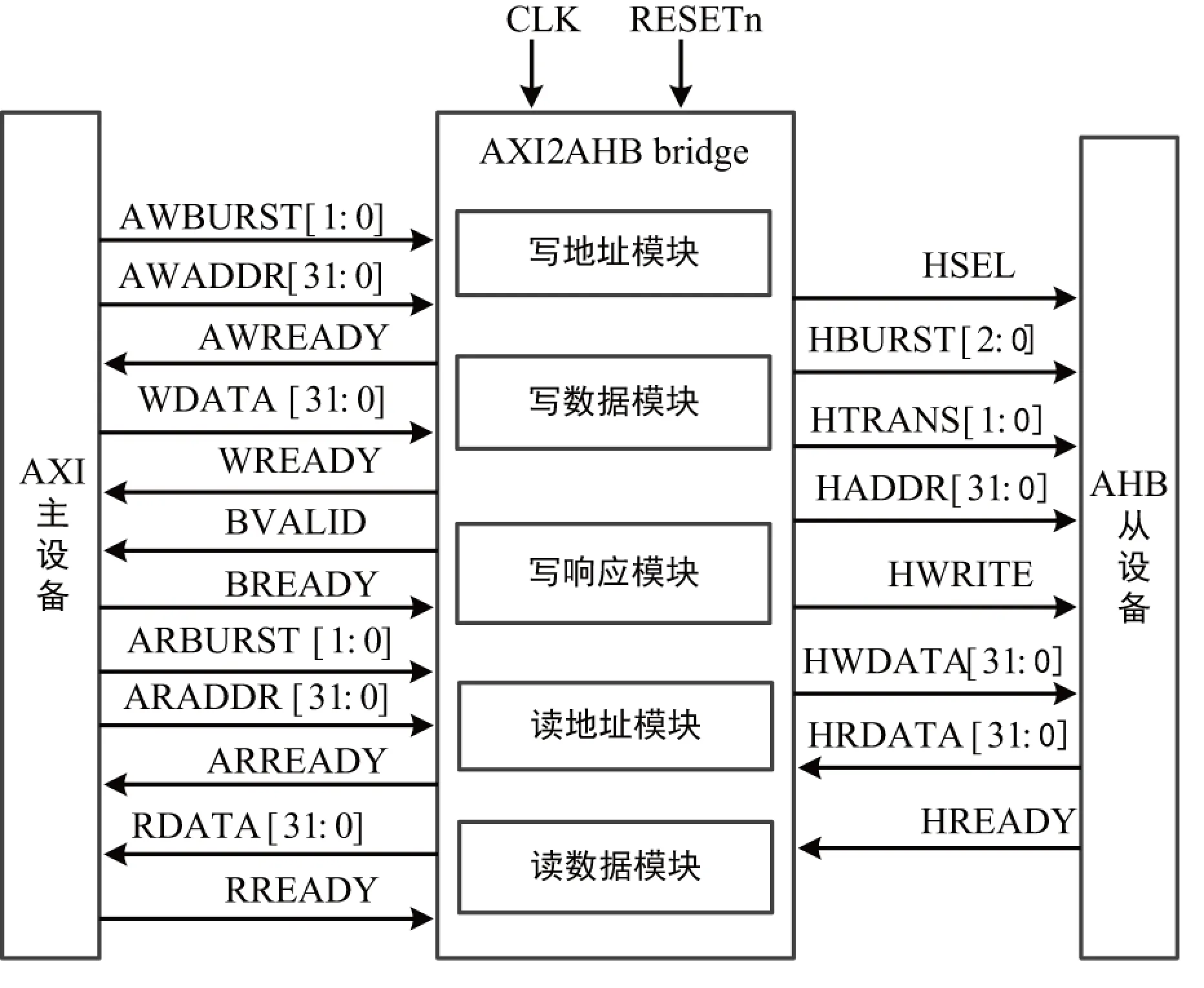

3.1 AXI2AHB总线桥的实现

AXI2AHB总线桥主要由写地址通道、写数据通道、写响应通道、读地址通道和读数据通道5部分组成。该桥通过上述5个通道来完成来自AXI主设备的读、写命令的操作,全部5个通道使用相同的VALID/READY握手机制传输数据及控制信息。传输源通过VLAID信号表明何时的数据或控制信息有效,目的源产生READY信号来表明已经准备好接受数据或控制信息,在VALID和READY信号同时为高的时候,开始传输信息。

当一个来自于AXI主设备的读命令到达时,总线桥先把读命令放置于读地址通道中,AHB从设备从读地址通道中取走读命令的相关信息,并把AXI主设备要读取到的数据放置于读数据缓冲器,同时会把读响应等相关信息一起置于读数据缓冲器。AHB从设备会不断地检查读数据缓冲器是否为空,如果非空,则取出读数据并放置到总线桥读数据通道上,并根据读取信息产生Rlast信号和RID。

当一个来自于AXI主设备的写命令到达时,总线桥先把写命令放置于写地址通道内,然后,AHB从设备从写地址通道内取走写命令的相关信息,并开始准备接收数据。与写命令的通道独立,只要有写数据写入并且写数据缓冲器非满,AXI 主设备先把写数据放置于写数据缓冲器,AXI总线接口的信号Wlast与Wstrb也会一起存入。总线桥把AHB从设备产生写响应的相关信息和BID存入写响应缓冲器,总线桥会不停地监听写响应缓冲器的状态,如果非空,总线桥会把写响应信息以及BID 取走,并置于写响应通道上,再传送给AXI主设备。

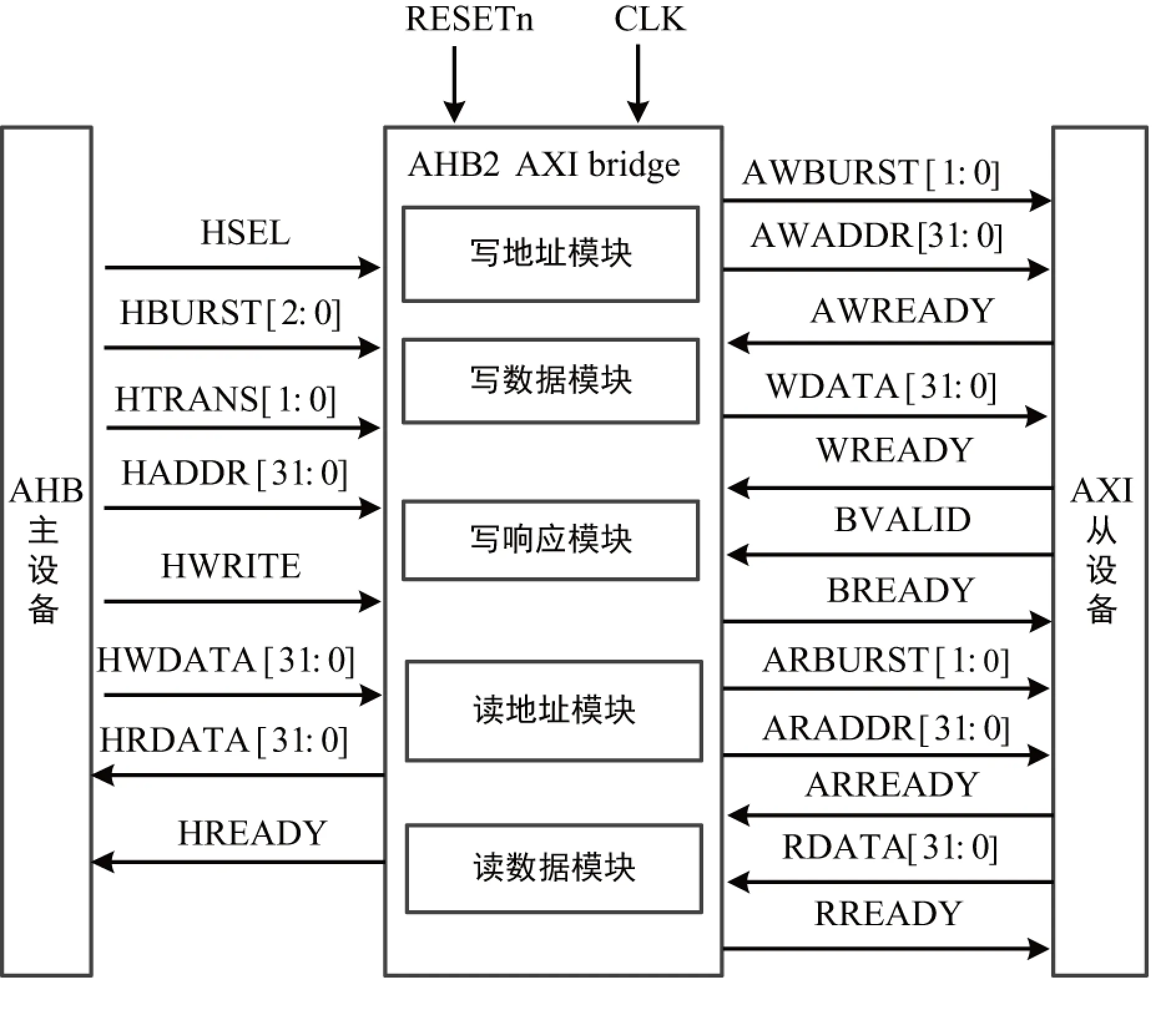

3.2 AHB2AXI总线桥的实现

与AXI2AHB桥相似,AHB2AXI桥的主要功能是实现从AHB总线到AXI总线的协议转换。由图3和图5可知,该桥带有一个AHB从设备的接口与一个AXI主设备的接口。从功能上讲,总线桥通过AHB从设备接口接收AHB总线协议,内部转换成AXI总线协议,通过AXI主设备接口外接AXI总线。由于AHB2AXI总线桥的数据流与AXI2AHB总线桥相反,处理方式也相近,因此,对于AHB2AXI桥的设计不再做详细分析[11-12]。

3.3 高效率策略分析

高效率意味着高带宽利用率,由于总线桥接入到高性能系统总线AXI,因此需要尽量提高AXI主设备单元对系统带宽的利用效率。为了提高带宽利用率,改进的思路是尽可能减少每个环节的等待时间,本文采取了2个措施:① 实施AXI协议所支持的多事务处理;② 采用写数据预取策略[13]。

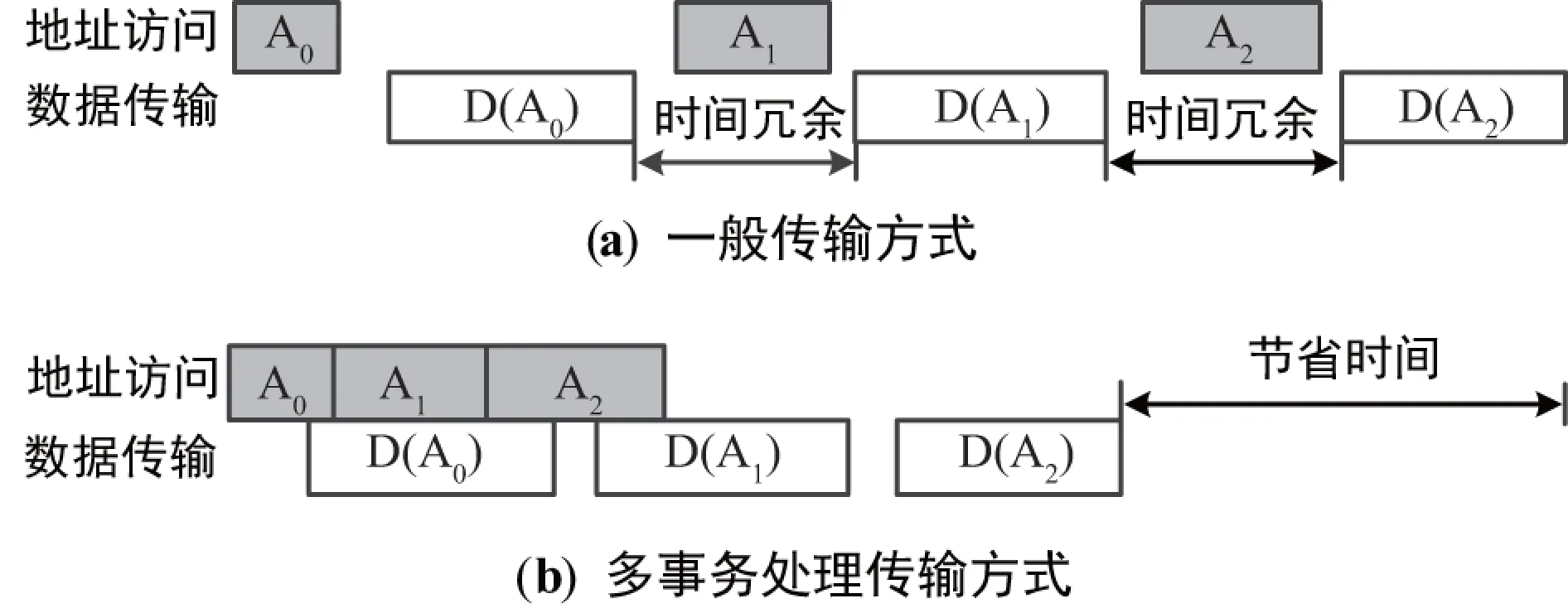

3.3.1 多事务处理

如图6(a)中,AXI主设备写数据的时候,基本传输流程是:

地址通道握手→数据通道握手→反馈通道握手→新的地址通道握手。

传统的传输方式会造成数据通道和地址通道之间存在等待反馈信号的问题,每次传输数据时必须等待上一次传输完成后才能进行下一次传输。实际上,AXI总线协议定义了5个分离的单向通道,能够支持乱序传输。在图6(b)中,AXI主设备可以连续向从设备发送多个访问请求,在一个访问正在进行的同时可以发布新的访问请求,这样可以减少通道之间额外的时间开销,提高总线带宽利用效率,同时也可以让目标设备提前准备接收数据。

图6 多事务处理技术的示意图

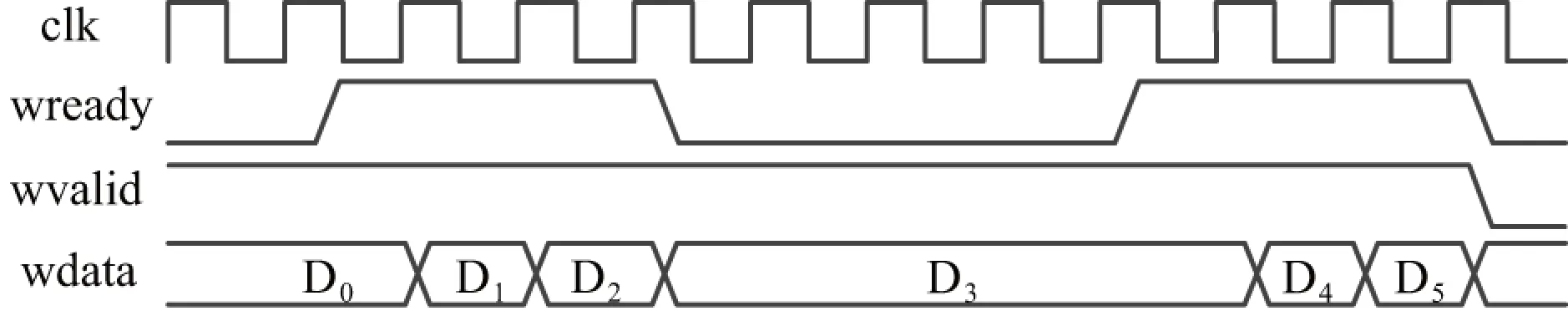

3.3.2 写数据预读

AXI主设备主动预取写数据,可以避免AXI主设备必须等待wready信号生效后才发送数据,在从设备就绪之前把数据发送出去,使得wvalid信号先于wready信号,从而减少写数据通道的无效等效时间,提高了系统带宽利用率。

图7为写数据通道的时序示意图,从图中可见,写数据D0和D3在wready信号生效之前就已经生效,避免了AXI主设备等待wready信号生效的时间冗余,可以提高带宽利用率。

图7 写数据通道的时序示意图

3.4 低功耗优化设计

由于AXI总线优越的性能和低时延,使得集成在SoC上的标准化IP越来越多,但是AXI总线自身提供的低功耗控制手段过于单一,实际降低的功耗并不是很理想。考虑到AXI总线本身具有很好的可扩展性,可以对AXI总线进行一定的低功耗优化技术扩展,以达到降低功耗的效果[14]。

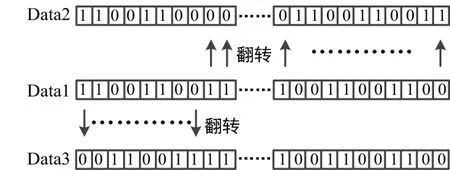

对于AXI总线来说,数据位宽最高可以达到128 bytes,地址位宽也有32 bits位宽。如果地址从0xFFFFFFFF变化到0x00000000,所有的地址线都会翻转,就会有32根线发生跳变。由于跳变造成的功耗对整个系统的功耗影响很大,所以尽可能地降低总线翻转频率是节省总线功耗的唯一方法。

本文设计的总线桥当主设备通过总线桥每次传输数据时,在当前传输数据与上一次传输数据之间进行判决,判决结果显示传输当前传输数据时总线翻转次数超过预定次数,则通过指示信号改变当前传输数据每一位的高低电平极性。例如:主设备传输的数据从Data10xCCCCCCCC变成Data20xCC333333,需要翻转24 bits信号,而只有8 bits信号不变化。主设备可以改变极性指示信号,同时也把数据变为Data30x33CCCCCC(按之前的电平表示方式,实际上二进制显示仍为0xCC333333),这样,只需要翻转9根数据线。由于数据线走线比较长,负载比较多,所以在密集传输过程中减少数据线的翻转,可以达到降低功耗的效果,示例如图8所示。

图8 极性反转bit示例

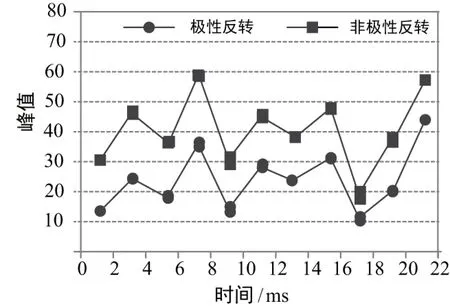

使用ESL(电子系统级别)平台构造双向总线桥的仿真环境[15-16],运行Dhrystone基准程序,在极性反转和非极性反转2种情况下的总线桥中的总线翻转率比较如下:极性反转指示的数据传输比不带极性反转的数据传输在22 ms 内的平均翻转率下降41%,如图9所示。

图9 2种环境下Drystone程序运行的总线翻转率对比

4 AXI2AHB总线桥的验证

本文使用Verilog语言在modelsim平台建立工程,实现了双向AXI2AHB总线桥,在testbench中设定一个虚拟的设备存储,再建立一个模拟读写的AXI或AHB主设备模型。

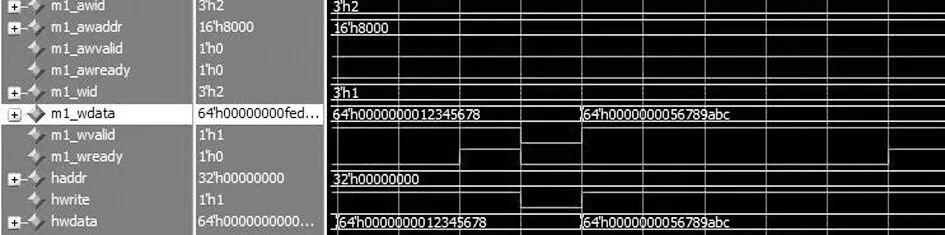

AXI总线向AHB总线写数据时,wvalid(图10中m1_ wvalid)信号为1,如图11所示仿真了突发类型为AWBURST[2:0] = 000(FIXED)时的传输情况,地址以固定式突发读写随机输入,AXI2AHB总线桥两侧的AXI总线地址、数据、控制信号和AHB总线地址、数据、控制信号完全对应。

图10 AXI总线到AHB总线读、写数据仿真

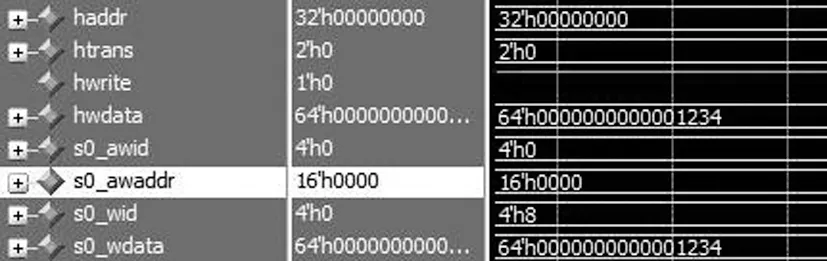

AHB总线向AXI总线写数据时,HWRITE信号为1,图11为仿真单次写传输的情况,AHB2AXI总线桥两侧的AHB总线地址、数据、控制信号和AXI总线地址、数据、控制信号完全对应。

图11 AHB总线到AXI总线读/写数据仿真

5 结束语

设计了一种支持多个主设备与多个从设备连接的双向AXI2AHB总线桥,既可以实现AXI总线到AHB总线的转换,也可以实现AHB总线到AXI总线的转换,同时经过优化也提高了效率,并降低了功耗。通过编写激励文件在Modelsim的仿真环境下进行了验证,验证结果表明了所设计的双向AXI2AHB总线桥符合片上总线转换的要求。当前随着SoC设计技术的不断提高,该设计提高了IP核的复用率,将会广泛用于SoC设计中。

[1] PrimeCell.Infrastructure AMBA3 AXI Register Slice(BPl30) Technical Overview[R].ARM Co.Ltd.,2004.

[2] Pasricha S,Dutt N.On-Chip Communication Architectures:System on Chip Interconnect[C]∥Morgan Kaufmann,2008:150-157.

[3] Jung H K,Jin X Z,Jung Y J.Design of Multimedia SoC Platform with a Crossbar On-Chip Bus for Embedded Systems[J].Network Computing and advanced InformationManagement,2008,1(9):292-297.

[4] 蒋周良,权进国,林孝康.AMBA总线新一代标准AXI分析和应用[J].微计算机信息,2006,10(2):275-277.

[5] 李 瑞,张春元,罗 莉.三种常用 SoC 片上总线的分析与比较[J].单片机与嵌入式系统应用,2004(2):5-8.

[6] 闫启政,李 斌,沈贵元.一种基于AMBA总线的SoC硬件加速器设计[J].无线电通信技术,2015,41(1):71-73.

[7] 刘林海.AHB总线分析及从模块设计[J].无线电通信技术,2007,33(3):33-38.

[8] 杨舜琪.AMBA AXI4 总线的研究与实现[D].哈尔滨:哈尔滨工业大学,2011.

[9] 夏 宏,郝春娥,闫江毓.双向AHB-WISHBONE总线桥的设计与验证[J].计算机工程与科学,2011,32(6):2201-2204.

[10] 胡景华.基于AXI总线的SoC架构设计与分析[D].上海:上海交通大学,2013.

[11] 闫 改,郭晓光.基于DSP的PCI总线高速DMA数据传输[J].无线电工程,2013,43(8):19-21,32.

[12] 邢悦新,王景伟,孙彦臣,等.传感信息无线传输系统设计与实现[J].无线电工程,2015,45(3):7-9.

[13] 梁天永.IP集成方案研究与DFI-AXI总线桥的设计[D].广州:华南理工大学,2010.

[14] 王 艳.基于AMBA AXI总线的低功耗扩展设计[J].计算机与信息技术,2008(12):105-108.

[15] 尚军辉.通用 SOC 系统的低功耗设计方法[J].中国集成电路,2013(9):23-30.

[16] 姚 刚.ESL设计方法在中国设计业生根[J].电子设计技术,2006(10):140.

Design and Verification of a Low Power and High Efficiency AXI2AHB Bidirectional Bridge

JIAO Long-tao1,GAO Xin2

(1.The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China;2.Unit 63916,PLA,Beijing 100089,China)

To make a convenient connection among different IP(intellectual property) cores,a design of Low Power High Efficiency bidirectional bus bridgeis proposed in view of AXI and AHB buses.Firstly,the characteristic of the two buses is described.And then a conclusion of the designing and implementing technique of the bidirectional bus bridge is reached accordingly,in combination of multi-transaction processing,write data prefetching strategy,and low powertechnology.Finally validation is implemented utilizing Verilog language under the environment of modelsim.Simulation results show that the bus bridge could greatly improve the system bandwidth utilization and reduce the power of the SoC chip.

AXI bus;AHB bus;bridge;bidirectional;low power

10.3969/j.issn.1003-3114.2017.02.20

焦龙涛,高 欣.一种低功耗高效率的双向AXI2AHB总线桥设计与实现[J].无线电通信技术,2017,43(2):78-82.

2016-11-22

国家部委基金资助项目

焦龙涛(1990—),男,硕士研究生,主要研究方向:数字集成电路设计。高 欣(1987—),女,助理工程师,主要研究方向:数字集成电路设计。

TP336

A

1003-3114(2017)02-78-5