基于Multisim 10的数字时钟的设计与仿真

2017-03-01陕西国防工业职业技术学院张喜凤

陕西国防工业职业技术学院 张喜凤

基于Multisim 10的数字时钟的设计与仿真

陕西国防工业职业技术学院 张喜凤

Multisim10作为一个高效的电路设计平台,是一个电路原理设计、电路功能测试的虚拟仿真软件。应用Multisim10 电路仿真工具设计了一款数字时钟电路,所设计的数字时钟可直接在数码管上显示“时”、“分”、“秒”十进制数字,同时具有校时功能,可分别对“时”、“分”、“秒”进行单独校准。计时过程具有整点自动报时功能。仿真结果表明,基于Multisim的数字时钟的设计是可行的,这种方法也为其他电子系统的灵活设计提供了方向。

数字时钟;Multisim 10;校时;整点报时

引言

Multisim 10作为一个高效的仿真软件,是在计算机上虚拟出一个测试仪器先进、元器件品种齐全的电子工作台[1-3],克服了实验室的条件限制,避免了使用中仪器损坏等不利因素,通过计算机完成电路的功能设计、性能分析、时序测试以及印刷线路板的自动布线,它与传统的设计方式相比较 采用计算机虚拟技术进行电子线路的分析和设计[4-5],大大提高了设计效率。

数字时钟是用数字集成电路构成并有数字显示特点的一种现代计时器,与传统的机械计时器相比,它具有走时准、显示直观、无机械磨损等优点,因而广泛应用于车站、码头、商店等公共场所[6]。

目前,数字电子钟的设计,主要是采用计数器等集成电路构成,由于所用集成电路多,连线杂乱[7],不便阅读与设计。本文采用层次电路设计,应用Multisim 10 设计了一个数字时钟电路。所设计的数字时钟能直接显示“时”、“分”、“秒”十进制数字,同时具有校时功能,可分别对“时”、“分”、“秒”进行单独校时。计时过程具有整点自动报时功能。

1.设计原理及框图

数字时钟是采用数字电路实现“时”、“分”、“秒”数字显示的计时装置[8]。数字时钟的主要功能就是计时,因此需要有振荡器来产生时间标准信号,即1Hz的秒脉冲信号,然后由计数器对秒脉冲信号进行计数,并将累计的结果以 “时”、“分”、“秒”的数字在数码管上显示出来[9]。由于计时的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路。电路设计框图如图1所示。

图1 数字时钟电路设计框图

2.单元电路的设计及仿真调试

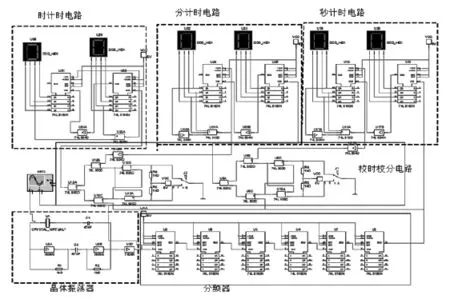

使用Multisim所设计的数字时钟电路的总电路如图2所示,下面对其模块电路进行下介绍。

2.1 振荡器的设计

振荡器是数字时钟的关键,它的频率稳定性直接影响数字时钟的精度。要产生稳定的时间标准信号,一般采用石英晶体振荡器。现在使用的指针式数字钟和数字显示的电子钟都使用石英晶体振荡器电路。从数字精度考虑,晶体振荡器频率越高,计时的精度愈高,但这样会使分频器的级数增加。在综合考虑这两方面因素的情况下,本设计使用的石英晶体频率为1MHz。

振荡器电路如图2左下角的晶体振荡器电路所示,其中U2A和U2B反相器构成多谐振荡器电路,石英晶体构成选频环节。由于当频率为f0时,石英晶体的电抗X=0,而在其他频率下电抗都很大,因此只有频率为f0的信号能够顺利通过,满足振荡条件。在电路接通后,电路就会在频率f0作用下形成自激振荡。由于该电路的频率比较稳定,但波形不够理想,因此需要在电路输出端加一个反相器U2C,这样既能起整形作用,使输出脉冲更接近矩形波,又能起缓冲隔离作用。

图2 数字时钟电路图

2.2 分频器设计

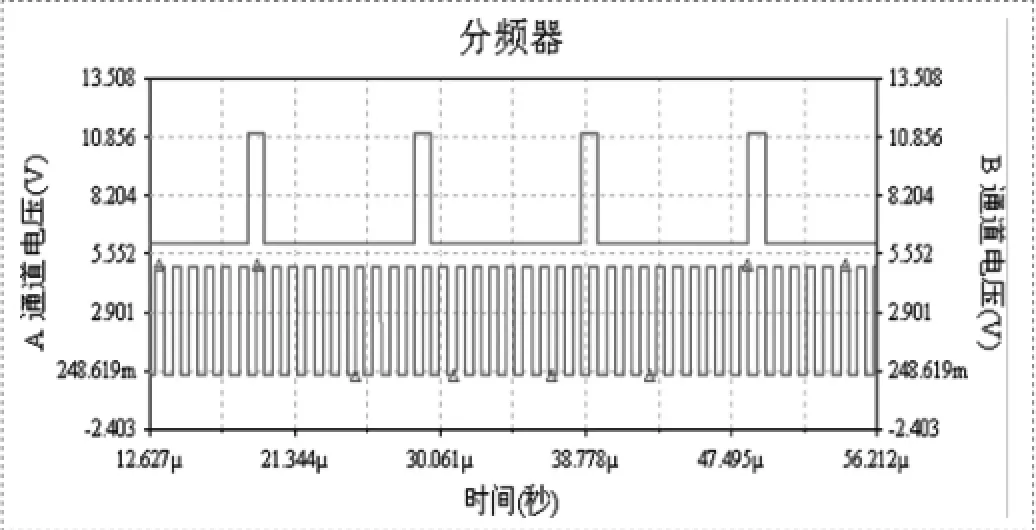

石英晶体振荡器产生的频率很高,要得到秒信号需采用分频电路。分频器的级数和每次的分频次数要根据晶体振荡器产生的信号频率来确定。如图2中分频器电路所示,电路产生的输出信号的频率为1MHz,需经过6级是分频电路分频后才可得到秒信号。电路中十分频电路采用的是十进制计数器74LS160,从计数器进位端输出的信号频率是时钟频率的十分之一,将前级的输出接到后级的输入,经过6级分频后,就可以得到1Hz的秒脉冲信号。对任一级分频器进行仿真,其仿真波形如图3所示,可以看出每一级分频器都可以很好地实现十分频。

图3 分频器仿真波形

2.3 秒、分计数器的设计

有了秒脉冲信号就可以对秒信号进行累计计时。根据60秒进1分的原则,秒计数器设计成六十进制计数器。电路设计采用两片74LS160,一片接成十进制计数器,作为秒的个位;另一片接成六进制计数器,作为秒的十位,然后将个位片的进位输出端通过一个非门连接到十位片的CLK输入端,组成六十进制计数器,完成秒的计数功能,其设计图见图2中的秒计数器。

该计数器中U1采用直接清零复位法构成的六进制计数器,U2是十进制计数器,将U2的进位输出通过一个非门直接连接到U1的时钟输入端实现计数器的级联,从而用两片74LS160实现六十进制计数。

秒的显示采用两个数码管,分别显示秒的个位和十位。为了简化电路,该数码管选用了元件库中的DCD_HEX元件,这是带译码功能的七段数码管,因此电路中省略了译码电路。为了调试电路方便,电路中直接调用了一个脉冲信号,将其频率设为1Hz作为秒脉冲信号源。

根据60分进1小时的原则,分计数器也应设置成六十进制计数器,所以分计数器电路和秒计数器电路电路完全相同。所不同的是,只有当秒计数器计到60时,分电路才能计一次,所以要将计分电路的时钟输入端通过一个非门与计秒电路的十位74LS160的清零端相连,如图9所示,这样,当秒计数器完成一个60计数时,计分电路才接收到一个时钟信号。

2.4 时计数器设计

计时电路的设计采用两片74LS160,先采用级联的方法,即将低位片的进位输出端RCO通过一个非门连接到高位片的时钟CLK输入端,采用一百进制计数,然后将高位片的QB和低位片的QC连接到两输入与非门的输入端。与非门的输出同时连接到两片的清零端,实现当计数到24时异步清零翻转为00,从而构成24进制计时电路。设计电路如图2中时计时电路所示,其中CLK输入的脉冲信号是为了调试时计数器电路的需要,在数字钟的设计中,该时钟输入端通过一个非门与计分电路的十位74LS160的清零端相连,这样,当分计数器完成一个60计数时,计时电路才接收到一个时钟信号。

2.5 校时电路

在刚开机接通电源时,由于“时”、“分”为任意值,或当数字钟出现走时误差时,都需要对时间进行校准。校时电路的基本原理是将秒信号直接引进计时器,让时计数器快速计数,在时达到需要的数字后,切断秒信号。较分电路也按此法进行。

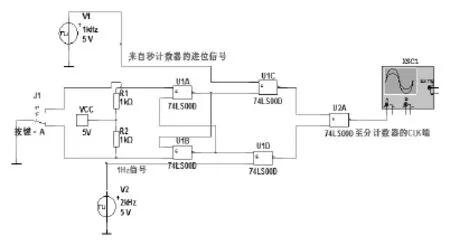

实现校时的电路的方法很多,如图4所示电路即可作为时计数器或分计数器的校时电路,其中采用RS触发器作为无抖动开关。通过开关J1,可以选择是将1Hz信号还是将来自秒计数器的进位信号送至分计数器的CLK端。

当开关J1置于上端时,来自秒计数器的进位信号送至分计数器的CLK端,分计数器正常工作;需要校正分计数器时,将开关J1置于下端,这时1Hz信号送至分计数器的CLK端,分计数器在1Hz信号的作用下快速计数,直至正确的时间,再将开关置于上端,达到校准分的目的。校准时的方法于此类似。

图4 校时电路

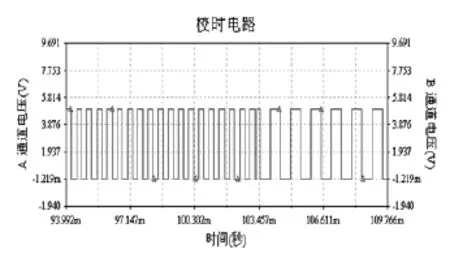

图5 校时电路仿真波形

连接该电路,仿真调试该电路的工作,其仿真波形如图5所示。在调试时在两个信号输入端输入不同频率的两个时钟信号,按A键切换开关J1,在输出端接示波器检测输出。

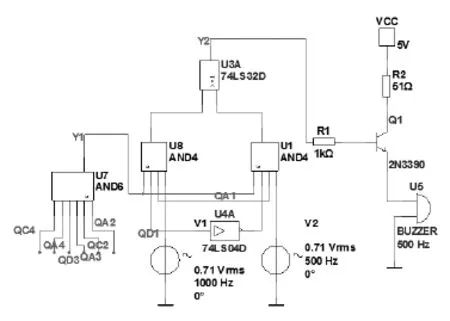

2.6 整点报时电路

电路设计要求差10秒为整点时开始每隔1S鸣叫一次,每次持续时间为1s,共鸣叫5次,前四次为低音(500Hz),最后一次为高音(1kHz)。因为分计数器和秒计数器在从59分51秒计数到59分59秒的过程中,只有秒各位计数器计数,分十位、分个位、秒十位的计数器的状态不变,分别为QD4QC4QB4QA4=0101,QD3QC3QB3QA3=1001,QD2QC2QB2QA2=0101,所以QC4= QA4= QD3= QA3= QC2= QA2= 1不变。设Y1= QC4QA4QD3QA3QC-2QA2,又因为在51、53、55、57秒时QA1=1,QD1=0,输出500Hz信号f2;在59秒时,QA1=1,QD1=1,输出1kHz的信号f1,由此可写出整点报时电路的逻辑表达式为:

用门实现该逻辑功能,则整点报时电路如图6所示。

3.整机电路的设计及仿真调试

将秒计数器、分计数器和时计数器单元电路共同构成数字电子时钟系统,秒计数器的CLK的输入端接晶振分频后获得的秒脉冲信号,再将辅助电路(如校时电路、整点报时电路)连接到电路中。数字时钟的整体电路设计图如图2所示。运行仿真开关,调试电路,直至电路工作正常。

图6 整点报时电路

4.结论

利用Multisim10对数字时钟进行设计和仿真,结果表明,其功能能够很好的实行,并且可以使用显示仪器直观快速地观察到设计结果,免去搭建电路的过程,大大缩短了设计时间,提高了效率和系统的可靠性。同时,此方法也可以移植到其他电子系统的设计,可以大大的减少设计研发时间,同时更换元器件方便快捷,为电子产品的设计提供了新的思路。

[1]孙立辉,权庭兰.基于Multisim的克拉泼电路设计[J].电子技术与软件工程.2013(22).

[2]王志强.开关电源设计[M].北京:电子工业出版社,2006.

[3]路士兵.数字电子时钟的设计[J].通讯世界,2015(12).

[4]刘允峰.基于Multisim的数字时钟设计[J].现代电子技术,2012(10).

[5]汤兵兵,帅江华.Multisim在电子技术实验教学中的应用[J].无线互联科技.

[6]朱晶波.电子电路仿真技术Multisim及其应用[J].电子制作.

[7]孙筠.Multisim应用于电子技术实验教学的研究[J].科技信息(科学教研),2007(27).

[8]赵玉婷,魏强,高鑫伟.Multisim 10在电子技术实验教学中的应用[J].电子制作,2013(14).

[9]伍俊.中职电工电子教学中有关Multisim的应用分析[J].时代教育,2016(14).

The design of digital clock Based on Multisim 10

Zhang Xifeng

(Electronics Engineer Department of ShaanXi Institute of Technology, Xi’an 710300,China)

Multisim10 as an effcient platform for the circuit design, is a virtual simulation software for the design and test of circuit function. The digital clock circuit is designed based on Multisim10. The digital clock has the functions of display "hours", "minutes" and "seconds" decimal number. The time can be calibrated individually and the automatic time function are also designed. Simulation results show that the design of digital clock based on Multisim is feasible, this approach also offers other electronic system of the fexible design direction.

Digital clock; Multisim 10; calibration; Alarm clock

张喜凤(1982—),女,内蒙古包头人,硕士,讲师,主要从事智能器件控制和集成电路设计方面的研究。

本文由陕西国防工业职业技术学院研究与开发项目(GFY-16-28)“基于arduino的辉光管万年历的设计与实现”项目提供基金支持。