基于电流补偿电路的密码芯片抗功耗攻击设计

2017-03-01严迎建许纪钧于敬超

严迎建 许纪钧 于敬超

(解放军信息工程大学 河南 郑州 450000)

基于电流补偿电路的密码芯片抗功耗攻击设计

严迎建 许纪钧 于敬超

(解放军信息工程大学 河南 郑州 450000)

为了建立具有普适性的功耗攻击防御单元,从系统级功耗恒定设计思想出发,设计一种电流补偿电路。首先,通过构建高线性转换I→V模块和V→I模块,实现准确模拟出密码算法IP核动态电流变化的功能;其次,通过电路的对称性设计,使得电流和电压变化相互补偿,抑制温度漂移效应对电流补偿电路的影响;最后,通过UltraSim仿真评估其抗功耗攻击效果,并分析其面积消耗。

功耗恒定 电流补偿电路 功耗攻击

0 引 言

对于密码芯片攻击者而言,在实际功耗攻击中一般采用在密码芯片的电源引脚和内核电源之间串联一个小电阻的方法,通过分析电阻两端的差分电压变化获取有关密钥信息。为了防御这种攻击方法,密码芯片设计者可以在密码SoC系统顶层添加抗功耗攻击模块,以掩盖密码芯片的功耗泄露。Shamir等提出了一种基于独立电源结构的智能卡抗功耗攻击设计方案[1];Muresan等提出在芯片内集成一个动态功耗检测的模拟电路,使得芯片的功耗始终处于一定的范围之内[2];Zafar和Güneysu等提出了基于多时钟源随机切换的方法实现时间随机化[3-4]。但是这些防御技术的安全性较低,如果攻击者掌握较高的降噪技术,就可以有效地过滤无关噪声,提高信噪比,获得有用的动态功耗信息。为此,王晨旭等提出了一种抗功耗攻击的电流平整电路[5],通过使密码设备供电电源端的电流保持恒定,消除了功耗与数据之间的相关性,但是其存在电路工作频率低、普适性差的缺点。

针对以上问题,本文从安全性和普适性角度出发,研究了系统级功耗恒定设计思路。同时为了保证模拟出的动态电流的准确性以及电流补偿电路的稳定性,本文设计一种电流补偿电路的硬件架构,其由动态电流检测模块、高线性转换I→V模块和高线性转换V→I模块,并通过UltraSim仿真[6]对其安全性、面积消耗进行了评估。

1 系统级功耗恒定模块架构分析

根据功耗测量的基本原理,由于密码芯片运行过程中的能量泄露无法直接获得,对于攻击者而言,一般采用在密码设备和电源之间插入测量电路。首先在密码芯片开发板上找到内核电源引脚,然后切断其与密码芯片的电源引脚,再串联上10 Ω小电阻。假如电源电压Vdd保持恒定,由于电阻上的压降正比于流经密码芯片的电流,可以将该电阻上电压变化作为能量泄露大小的衡量工具。如图1所示为实测能量泄露采集平台架构,整个密码芯片功耗信息采集平台包括FPGA开发板、DE2开发板、示波器和PC机。

图1 功耗采集与分析平台整体架构

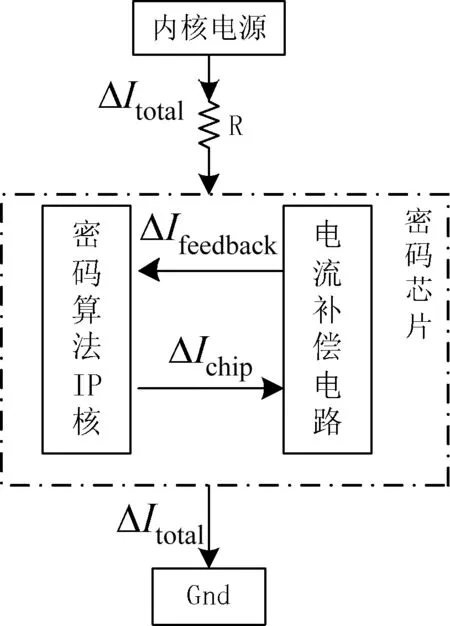

系统级功耗恒定模块设计思想是通过补偿待测电阻的电流变化,使得电阻上的压降保持恒定,从而使攻击者无法准确采集到密码芯片运算过程中的能量泄露。如图2所示为基于电流补偿设计的系统级防护原理[7]。ΔItotal表示流经密码芯片的总电流变化,也就是待测电阻上的电流变化;ΔIchip表示在密码芯片运算过程中,密码算法IP核的总电流变化,也就是实际上的能量泄露;ΔIfeedback表示电流补偿电路产生的补偿电流变化。当补偿电流ΔIfeedback变化与密码算法IP核电流ΔIchip变化大小相等并且同步时,内核电源端和密码芯片电源端之间的电流变化保持恒定,即采样电阻上的电压恒定,密码芯片的功耗泄露被“隐藏”,功耗攻击失效。

图2 电流补偿电路设计的系统级防护原理

2 电流补偿电路架构设计

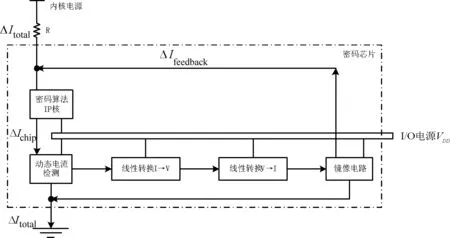

在实际电路设计过程中,无法通过镜像电路或者其他放大器电路直接准确模拟出密码算法IP核动态电流变化ΔIchip。因此,为了得到准确的补偿电流ΔIfeedback,本文设计了如图3所示的电流补偿电路架构。

图3 电流补偿电路架构

2.1 动态电流检测电路

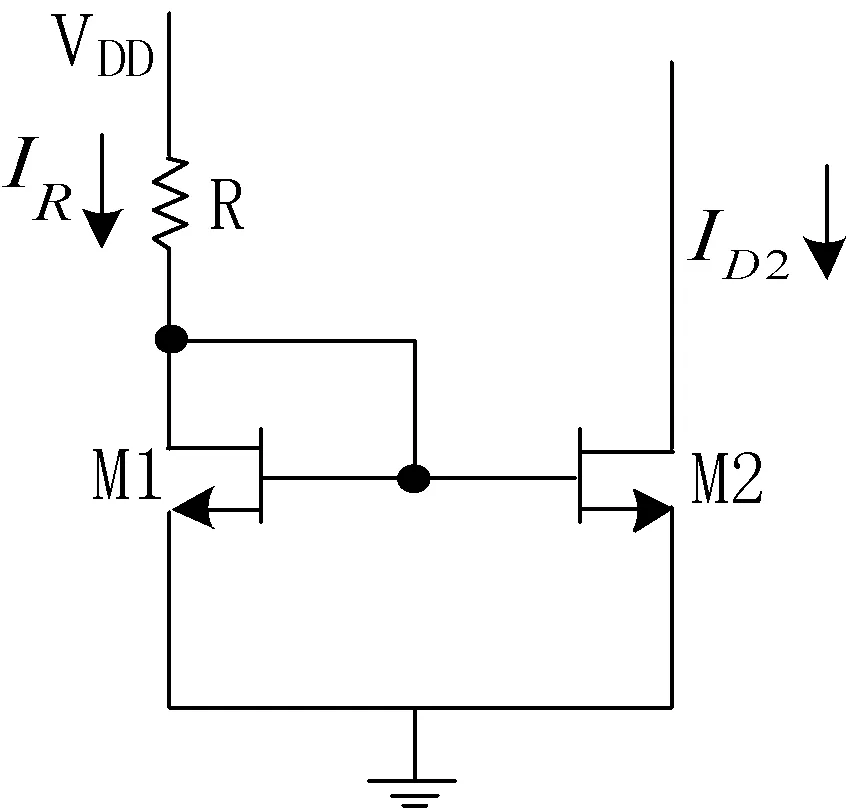

镜像电路如图4所示,能够复制输入端电流变化,并且不受制造工艺和环境温度的影响,因为镜像电路具备温度补偿效应。

图4 镜像电流源

但是,其也存在以下两方面的缺陷:(1) 影响电路电压的稳定性;(2) 镜像电路的准确性低。

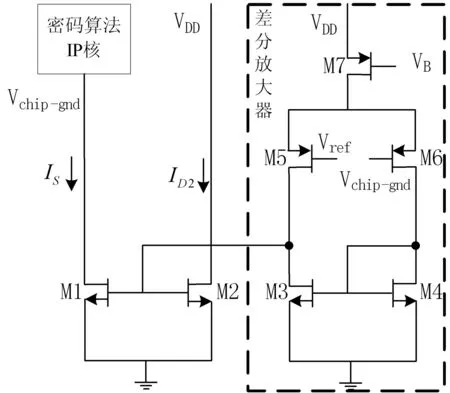

为改善上述缺陷,本节对镜像电路进行了改进,并设计如图5所示的动态电流检测电路,其由性能参数相同的晶体管M1-M7以及参考偏置电压构成。

图5 动态电流检测电路

如图5所示右侧为差分放大器,电路的对称性使得电流、电压变化相互补偿,能够抑制温度漂移效应对电路性能的影响。对于晶体管M5和M6而言,栅极输入电压为共模信号,使得两只晶体管栅极和源极的电流变化相近,即IG5≈IG6,IS5≈IS6。因此,漏极电压变化也相近,使得差分输出电压极小,可以忽略不计。实际上,差分放大器对共模输入电压的抑制,不仅利用了电路的对称性原理,而且利用了镜像电路的负反馈原理,抑制了M5和M6的漏极电流变化,使得差分输出电压极小。

差分放大器的差分输出电压作为镜像电路M1管和M2管的栅极电压,可以通过反馈作用,将镜像电路中M1管的漏极—源极电压变化固定在较小的范围内,且电压值也较低,从而可以保证晶体管M1和M2工作在饱和区内,电流复制效应也相应的提高。在不影响密码芯片正常工作的前提下,当密码算法IP核工作电流变化ΔIchip时,M2管的电流变化也为ΔIchip,从而起到精准复制密码算法IP核电流变化的作用。

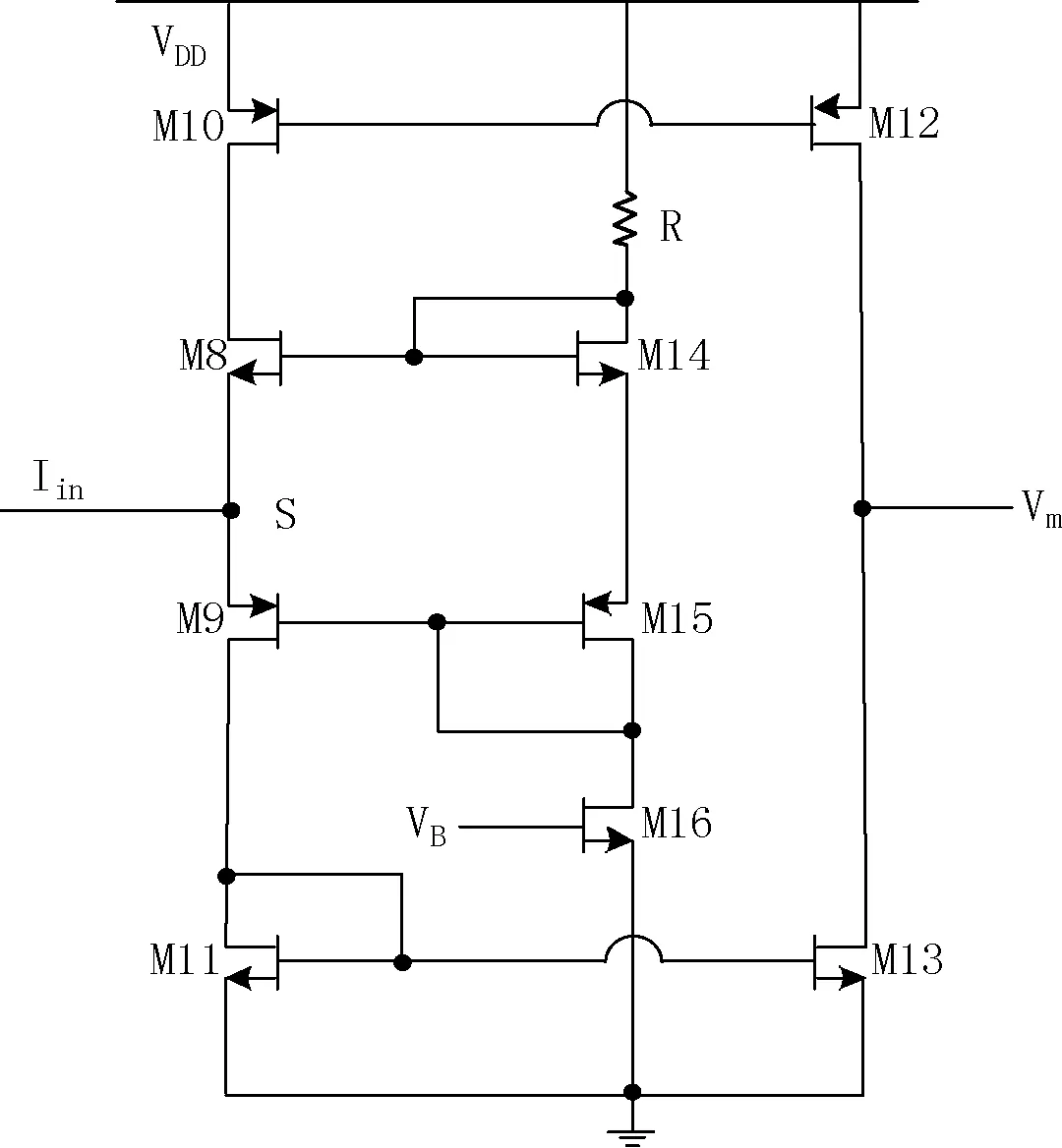

2.2 线性转换I→V电路设计

图6为本节设计的高线性转换I→V电路。电流Iin注入跨导放大器中,作为晶体管M8和M9源极输入电流,节点S为一个低阻抗节点,输入M8管和M9管的电流之比为gm8/gm9。晶体管M10和M12构成一组镜像电路,晶体管M11和M13构成一组镜像电路,输入电流Iin经过晶体管M8和M9分流后,经过镜像电路、放大电路,转化为输出电压变化Vm。其中,Vm表示由镜像电路配置提供的偏差电压,输入电流Iin和输出电压Vm之间存在式(1)所示关系:

(1)

其中,W和L分别表示晶体管的宽度和长度设计尺寸,Rm表示在节点Vm处产生的输出寄生阻抗,则Rm可以用式(2)表示:

(2)

其中,rDS12和rDS13分别表示晶体管M12和晶体管M13漏极-源极的寄生阻抗,ID12和ID13分别表示晶体管M12和晶体管M13的漏极电流,λ表示沟道长度调制参数。

图6 高线性转换I→V模块

通过以上分析可知,假设不考虑晶体管的失调效应以及外部环境因素对I→V转换电路的影响,通过I→V转换电路能够将输入电流变化高线性的转换为输出电压变化。

2.3 线性转换V→I电路设计

将集成运算放大器的同相输入端连接输入电压,反相输入端连接负反馈电路,则集成运算放大器可以构成一种线性V→I转换电路。但是集成运算放大器一般面临以下两种威胁:(1) 输入电压或电流过大,导致PN结被击穿;(2) 输出端直接接地或电源,导致输出功耗过高。

为了提高集成运算放大器的安全性,以及结合实际应用环境,本节设计了一种负载电阻接地的电压—电流线性转换电路。如图7所示,两个集成运算放大器都采用了负反馈效应:A1在同相输入端和输出端之间并联引入电流负反馈电路,实现同相求和功能,并且能够防止输入电压过大而引起的PN结击穿效应;A2在同相输入端和输出端之间并联引入电压负反馈电路,实现电压跟随器功能,而且能够防止在闭环状态下由于共模电压过大而引起的损坏。此外,在集成运算放大器的输出端通过插入电阻RL,可以割断输出端与地或电源的直接连接。

图7 实用型电压—电流线性转换电路

2.4 电流补偿电路设计实现

本文提出了一种密码芯片电流补偿电路,其晶体管级电路设计如图8所示,由密码算法IP核、测量电阻R、镜像电路、高线性转换I→V、高线性转换V→I以及镜像补偿电路组成,Vref、Vb为偏置电压输入,IR为电流源,R0为1Ω小电阻,VDD为I/O电源的供电电压。

图8 电流补偿电路的晶体管级设计实现

本文设计的电流补偿电路的工作原理为:首先镜像电路通过检测密码算法IP核的电流变化映射出与IS变化方向和大小都相等的镜像电流ID2,即IS≈ID2;之后,在固定电流源IR的作用下,镜像电路输出与IS变化大小相等、方向相反的电流Iin,即Iin≈IR-IS;然后,将Iin作为高线性转换I→V模块的输入电流,经过镜像、放大后,得到输出电压:

输出电压变化与密码算法IP核的电流变化成线性关系,方向相反;其次,将输出电压Vm作为高线性转换V→I模块的输入电压,经过转换,得到输出电流:

输出电流变化与密码算法IP核的电流变化成高线性关系,方向相反;最后,通过镜像电流源电路,将输出电流Im变化镜像映射至Ifeedback,则Ifeedback≈Im。通过以上转换可知,补偿电流Ifeedback变化与密码算法IP核电流IS变化大小相等、方向相反。当流经密码算法IP核的电流IS增大时,电流补偿电路产生与之变化大小相等、方向相反的补偿电流,则流经待测电阻的电流保持不变;同样,当流经密码算法IP核的电流IS降低时,电流补偿电路产生的补偿电流降低,则流经待测电阻的电流同样保持不变。因此,待测电阻两端的电压保持恒定不变,通过差分探头无法获得功耗信息与处理数据之间的相关性。

3 电流补偿电路抗功耗攻击验证

本文在0.18umCOMS工艺下,采用Cadence环境下UltraSim仿真工具对电流补偿电路的安全性和功耗消耗进行仿真验证。采用DES加密运算作为密码芯片的算法,具体功耗采集步骤为:首先用Verilog语言描述DES算法;之后在后端布局布线的基础上,提取带有寄生参数的Spice网表;然后将电流补偿电路添加到DES算法的Spice网表中,得到具有抗功耗攻击效果的DES算法Spice网表;最后结合生产工艺参数,通过UltraSim模拟出接近DES加密过程的瞬态电流曲线。

3.1 电流补偿电路的抗功耗攻击效果评估

电流补偿电路能够补偿采样电阻两端的差分电压变化,从而消除采样功耗与处理数据之间的相关性,其中:电流变化抑制率A是衡量电流补偿效果的最直接指标[8],可以用式(3)定义:

(3)

为了评估电流补偿电路的抗功耗攻击效果,本节采用1.8V工作电压,电流源IR为7mA,参考电压Vref为0.7V,V→I转换模块电阻R0为1Ω,电路工作频率为100MHz,则通过UltraSim仿真得到的瞬态电流曲线如图9所示。其中:曲线a表示流经DES加密过程中的电流消耗ΔIchip,曲线b表示补偿电流ΔIfeedback,曲线c表示流经采样电阻的电流ΔItotal。

图9 加入电流补偿电路的密码芯片仿真瞬态电流

由图9可知:补偿电流的变化ΔIfeedback与DES加密芯片的电流变化ΔIchip,大小相等,方向相反;并且补偿电流与密码算法IP核电流之和基本上等于流经采样电阻的电流ΔItotal;ΔItotal变化范围较小,可以忽略不计。在100MHz下,密码芯片的瞬时电流变化最大范围为2mA,采样电阻的瞬时电流变化最大范围为0.2mA,则电流变化抑制率A为90%。因此电流补偿电路可以极大地降低采样电阻两端的功耗变化范围,显著增加了功耗攻击的难度。

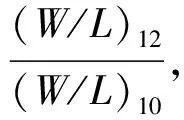

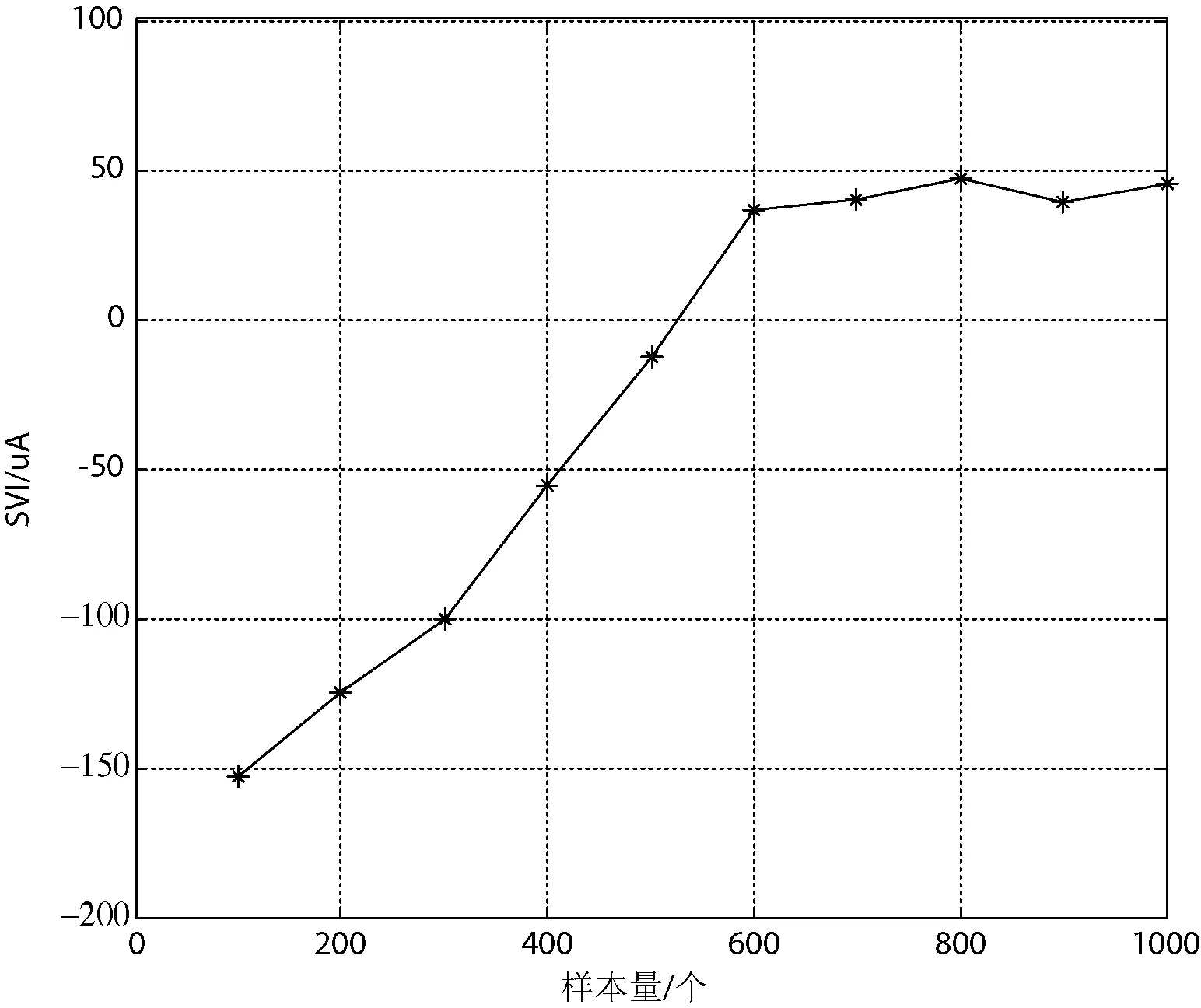

为了验证电流补偿电路的抗功耗攻击效果,采用DPA攻击所需样本量作为量化指标,采用相同明文和密钥对DES算法进行加密运算。

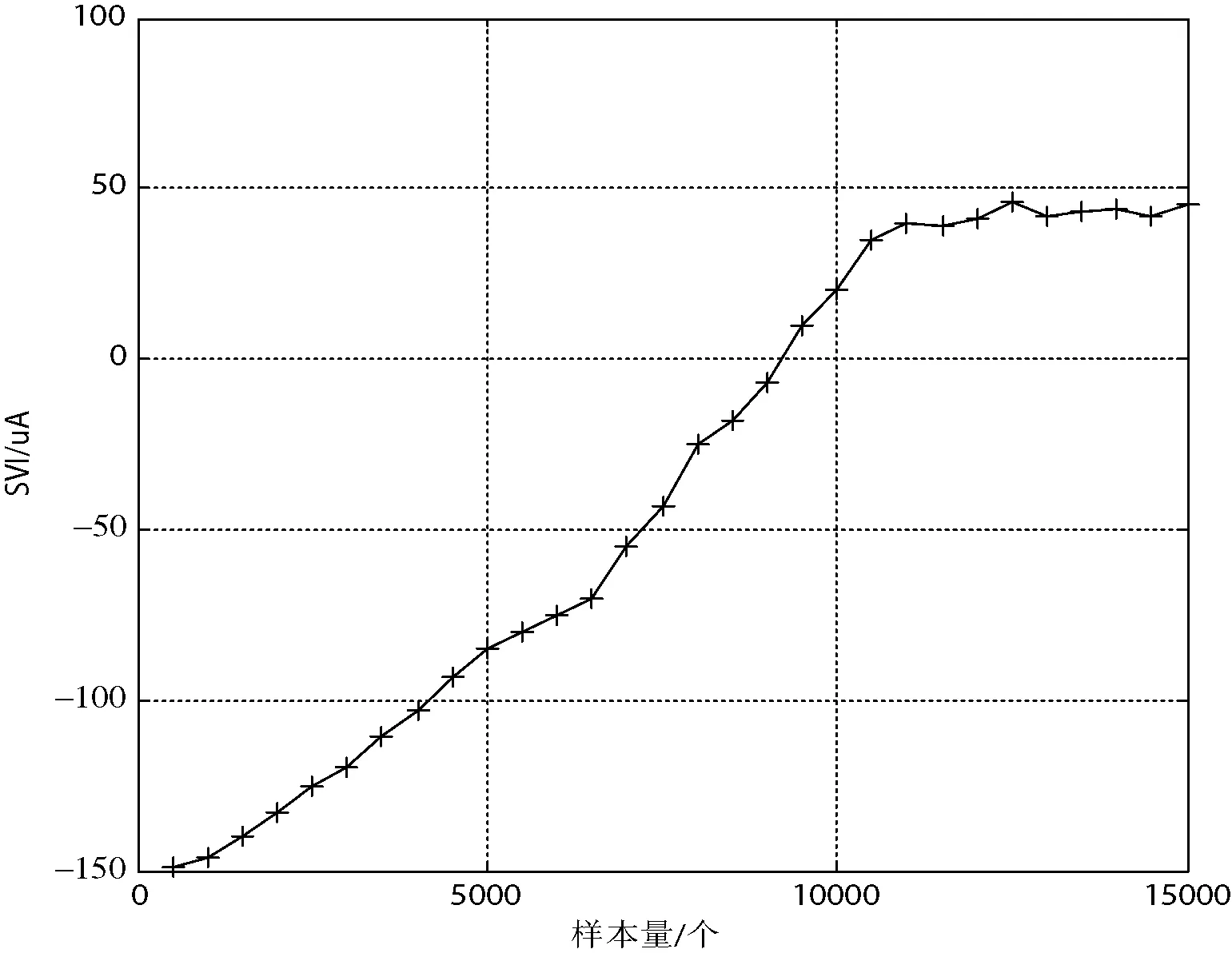

定义 假设正确密钥的DPA曲线尖峰峰值为Icorrect,错误密钥的DPA曲线尖峰峰值为Iwrong,定义SVI(SuccessValueIndicator)为功耗攻击成功指标,并且SVI=min(Icorrect-Iwrong)。

分别攻击未添加防护措施和添加电流补偿电路的DES第一轮加密运算第一个S盒对应的前6bits子密钥,并以S盒输出的第1位作为区分函数。通过综合、布局布线以及网表抽取得到DES算法的Spice网表,使用UltraSim仿真得到15 000组随机明文加密运算的功耗曲线,采用DPA攻击,得到如图10和图11所示的样本量与SVI之间的关系。分析可知,对于未添加防护措施DES密码芯片而言,DPA攻击成功所需的样本量最少为600;对于添加补偿电路设计的DES密码芯片而言,DPA攻击成功所需的样本量最少为9500,增大了至少15倍。因此可以认为电流补偿电路设计能够显著提高密码芯片的安全性。

图10 未加防护措施的DPA攻击时SVI与样本量的关系

图11 加电流补偿电路的DPA攻击时SVI与样本量的关系

3.2 电流补偿电路的面积消耗评估

在0.18umCOMS工艺下,当密码芯片的工作电流在1~10mA范围内时,本文提出的电流补偿电路的版图面积为12×103um2,而DES密码算法的版图面积为180×103um2,3-DES密码算法的版图面积为326×103um2。因此,电流补偿电路占DES算法版图面积的6.7%,占3-DES算法版图面积的3.7%,可以认为电流补偿电路占用密码芯片的面积非常小,对设备面积的影响可以忽略不计。

在0.18um的COMS工艺下,将本文设计的电流补偿电路的工作频率、面积消耗、电流变化抑制率与文献[5,9]相对比,得到表1。由表1可知,与文献[9]和文献[5]相比,本文设计的电流补偿电路面积增益显著降低。因此,本文设计的电流补偿电路具有工作频率高、面积消耗小、电流变化抑制率高的特点。

表1 不同电流补偿电路的性能对比

4 结 语

本文从系统级防护技术出发,研究了基于电流补偿电路的功耗恒定模块设计方案,提出了一种安全性高、工作频率高、面积消耗低的电流补偿电路。该电路由动态电流检测模块、高线性转换I→V模块和高线性转换V→I模块三个基本部分组成。通过UltraSim仿真发现,面积增益不超过7%;针对DES算法,该电路设计使得DPA攻击成功所需的样本量至少增大了15倍,实现了系统级抗功耗攻击的效果。

[1]ShamirA.ProtectingSmartCardsfromPassivePowerAnalysiswithDetachedPowerSupplies[C]//ProceedingsoftheSecondInternationalWorkshoponCryptographicHardwareandEmbeddedSystems.London:Springer,2000:71-77.

[2]MuresanR.ModelingandApplicationsofCurrentDynamicsinaComplexProcessorCore[D].Waterloo:UniversityofWaterloo,2003.

[3]ZafarY,HarDS.ANovelCountermeasuretoResistSideChannelAttacksonFPGAImplementations[J].InternationalJournalonAdvancesinSecurity,2009,2(1):1-7.

[4]GüneysuT,MoradiA.Genericside-channelcountermeasuresforreconfigurabledevices[C]//Proceedingsofthe13thInternationalConferenceonCryptographicHardwareandEmbeddedSystems.Springer,2011:33-48.

[5] 王晨旭,王进祥,韩志伟,等.一种用于DPA防御的电流平整电路设计[J].华中科技大学学报(自然科学版),2013,41(2):58-63.

[6] 罗俊,郝跃,秦国林,等.微纳米CMOSVLSI电路可靠性仿真与设计[J].微电子学,2012,42(2):255-260.

[7] 王晨旭.密码芯片抗功耗攻击技术研究[D].哈尔滨:哈尔滨工业大学,2013.

[8]MuresanR,GregoriS.ProtectionCircuitagainstDifferentialPowerAnalysisAttacksforSmartCards[J].IEEETransactionsonComputers,2008,57(11):1540-1549.

[9]TiriK,VerbauwhedeI.Adigitaldesignflowforsecureintegratedcircuits[J].IEEETransactionsonComputer-AidedDesignofIntegratedCircuitsandSystems,2006,25(7):1197-1208.

A DESIGN OF CIPHER CHIP BASED ON CURRENT COMPENSATION CIRCUIT TO RESIST ANT POWER ATTACK

Yan Yingjian Xu Jijun Yu Jingchao

(ThePLAInformationEngineeringUniversity,Zhengzhou450000,Henan,China)

In order to design high universality units to resist ant power attack, a current compensation circuit is designed from the view of power consumption constant in system-level. Firstly, a high linearity I→V transformation module and a high linearity V→I transformation module is constructed, which realizes the function of accurate copying the current variation of cipher algorithm IP core. Secondly, the changes in current and voltage do compensate based on the symmetrical design, which inhibit the effect of temperature drift to current compensation circuit. Finally, the UltraSim simulation evaluates the effect of resisting power attack of this design, and analyzes the area consumption.

Consumption constant Current compensation circuit Power attack

2015-11-15。严迎建,教授,主研领域:芯片安全防护。许纪钧,硕士生。于敬超,硕士生。

TP309.7

A

10.3969/j.issn.1000-386x.2017.01.056