用于高速流水线ADC的低抖动多相时钟产生电路

2017-02-27戴立新冯立康洪国东陈珍海叶爱民

戴立新,冯立康,洪国东,陈珍海,叶爱民

(1.黄山市七七七电子有限公司,安徽黄山245041;2.中国电子科技集团公司第58研究所,江苏无锡214072;3.江西省电力公司,南昌330096)

用于高速流水线ADC的低抖动多相时钟产生电路

戴立新1,冯立康1,洪国东1,陈珍海2,叶爱民3

(1.黄山市七七七电子有限公司,安徽黄山245041;2.中国电子科技集团公司第58研究所,江苏无锡214072;3.江西省电力公司,南昌330096)

设计了一种用于高速流水线ADC的多相时钟产生电路。通过采用一种高灵敏度差分时钟输入结构和时钟接收电路,降低了输入时钟的抖动。该多相时钟产生电路已成功应用于一种12位250 MSPS流水线ADC,电路采用0.18 μm 1P5M 1.8 V CMOS工艺实现,面积为2.5 mm2。测试结果表明,该ADC在全速采样条件下对20 MHz输入信号的信噪比(SNR)为69.92 dB,无杂散动态范围(SFDR)为81.17 dB,积分非线性误差(INL)为-0.4~+0.65 LSB,微分非线性误差(DNL)为-0.2~+0.15 LSB,功耗为320 mW。

流水线模数转换器;时钟产生;时钟接收

1 引言

高速ADC是一个时控系统,其必须严格按时间序列进行信号采样和模数转换,因而对高稳定时钟的要求特别高。时钟的抖动直接决定了ADC能达到的信噪比。流水线ADC电路的工作需要多相位、不同占空比时钟信号的控制,时钟信号的上升沿控制着ADC的采样和偶数级流水线的量化,下降沿控制信号的保持和奇数级流水线的量化[1~2]。因此高稳定的时钟对于高速流水线ADC异常重要。

本文基于0.18 μm CMOS工艺设计了一种用于高速流水线ADC的多相时钟产生电路,并成功运用于一款12位250MSPS流水线ADC中,测试结果表明所设计的ADC性能良好。

2 电路结构

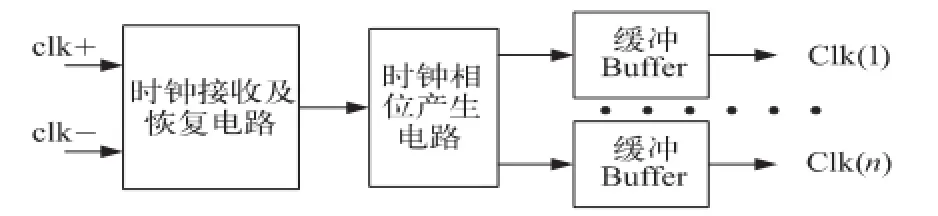

对于高速流水线ADC所需的低抖动多相时钟的实现,本文采用输入时钟恢复整形、相位产生电路和时钟缓冲驱动电路级联使用的方式获得。如图1所示,输入差分互补时钟首先进入时钟接收及恢复整形模块,将片外原始输入时钟进行转化得到电源地摆幅互补时钟;其次该互补时钟分别进入一个时钟相位产生模块,产生流水线ADC工作所需要的多相时钟;最后多相时钟经时钟输出缓冲Buffer输出到各级子级电路中。

图1 低抖动时钟产生电路系统结构框图

3 电路实现

3.1 时钟接收及恢复电路

高速ADC的采样时钟通常采用差分输入,因此其接收电路类似一个比较器电路。差分时钟输入的共模电平基本设置在VDD/2左右,差分信号经过一个单端放大器进行放大,放大之后的信号经过缓冲器整形即可得到标准摆幅的时钟信号。

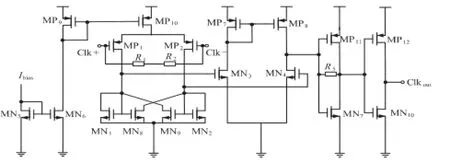

图2所示为本文设计的差分时钟接收电路,图中MPl、MP2、MNl、MN2、MN8和MN9组成的施密特触发器,以检测一个大于50 mV的迟滞电压[3]。在电路中有两个反馈路径,第一个反馈是负反馈,通过MP1和MP2的共源节点的电流串联负反馈。第二个反馈是一个正反馈,通过连接MN8和MN9的源和漏的并联电压正反馈。如果正反馈的系数小于负反馈的系数,整个电路将会变成一个负反馈,同时失去迟滞效应。如果正反馈的系数大于负反馈的系数,整个电路将会变成一个正反馈,迟滞效应将会出现在电压传送线上。作为一个低压信号,一个电路需要一个固定的迟滞特性(或一个20~50 mV的迟滞电压)以便改善接受电路接口的抗干扰性。在图2的电路里,为了确保一个25 mV的迟滞电压,MN8和MN9需要以一个固定电流增加宽长比,这样整个电路变成了正反馈,但电路的工作速度减慢了。

图2所示时钟接收及恢复电路对高质量的外部输入时钟进行处理即可得到非常稳定的内部时钟Clkout。为得到高稳定度时钟,通常需要使用专用的时钟产生电路为高性能流水线ADC提供采样时钟。然而在实际系统应用中,为减小系统复杂度,ADC所需时钟通常直接由应用系统中的数字信号处理电路直接提供。而该类电路所提供时钟的抖动特性和稳定度基本上难以满足高性能流水线ADC的时钟要求。因此,为降低ADC对外部时钟的性能要求,ADC片内时钟恢复模块通常在图2所示电路的后端增加使用多相位时钟产生电路,以保证ADC内部工作所使用时钟的高稳定度。

图2 时钟接收电路

3.2 多相非交叠时钟产生电路

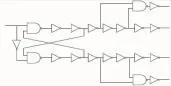

对于流水线型ADC,其子级电路为完成对模拟输入信号的采样和保持,需要一个两相时钟来控制电路的工作状态。在高速高精度的要求下,两相时钟之间的相位偏差与时钟相位抖动等将直接影响到信号的动态性能[4]。图3所示即为本文采用的两相非交叠时钟电路,其中CLKIN为外部输入的高精度基准时钟信号,Φ1和Φ2为电路输出的两相非交叠信号。同时在流水线模块中,通常为消除开关管的沟道电荷注入效应和时钟馈通效应等非线性影响,需要加入辅助的时钟信号,Φ1′和Φ2′是为了消除上述非线性而设计的辅助时钟输出信号。

图3 两相非交叠时钟电路

该时钟电路通过一个RS触发器产生,通过两个反相器的延时来控制非交叠的间隔时间。辅助时钟电路通过非交叠时钟信号同该信号与两反相器延时后在与门电路作用下产生,通过与门电路可使两时钟信号的上升沿对齐,辅助时钟与非交叠时钟信号的延时时间由反相器的延时大小决定。引入两个辅助时钟Φ1′和Φ2′分别在各自对应的原始时钟信号Φ1和Φ2关断前关断。其理想的波形图如图4所示。其中t1为Φ1′提前Φ1时钟关断的时间,t2为Φ1和Φ2两相非交叠的延迟时间对于反相器构成的延时单元,当管子尺寸过小时,会使得反相器的延时时间过短,且很难驱动大负载信号,且小尺寸会对时钟抖动比较敏感。当管子尺寸太大时又会占用较大的版图面积。通过在输出时钟信号与负载间加缓冲器来兼顾面积和延迟时间的问题。图4所述时钟相位产生电路可用于产生简单的两相非交叠时钟,通过扩展触发器和反馈环路也可以产生四相不交叠时钟。

图4 两相非交叠时钟时序

4 试验结果

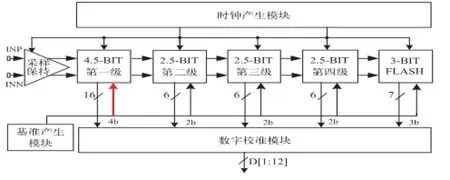

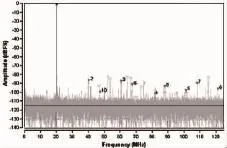

本文所设计多相时钟产生电路被运用于一款12位250 MSPS流水线ADC芯片电路中,用于提供采样保持电路和各级流水线子级电路的采样和复位时钟。该12位ADC的系统框图如图5所示,输入模拟信号处理通道包括一个高速采样保持电路,一级4.5-bit流水线子级电路,3级开关电容2.5-bit子级电路和最后一级3-bit flash ADC电路[5]。各级子级电路所量化得到的数字码最后进入延时同步和数字纠错模块,经移位累加得到最后12位输出码字。电路采用0.18 μm 1P5M 1.8 V CMOS工艺。时钟产生电路的位置为图中右下角的Clock模块。图6给出了12位250 MSPS流水线ADC的典型FFT测试结果,输入为20 MHz正弦信号,峰峰值为2 V,幅度为-1 dBm,测得SNR为69.92 dB,SFDR为81.17 dB,表明所设计的时钟产生电路满足12位高速ADC的系统设计要求。

图5 ADC系统结构图

图6 ADC FFT测试结果

5 结论

本文基于0.18 μm CMOS工艺设计了一种用于高速流水线ADC的低抖动多相时钟产生电路,并被运用于一款12位250 MSPS流水线ADC芯片电路中,用于提供采样保持电路和各级流水线子级电路的采样和复位时钟。测试结果显示,该ADC对输入为20MHz的正弦信号,测得的SNR为69.92 dB,SFDR为81.17 dB,表明所设计的时钟产生电路满足12位高速ADC的系统设计要求。该低抖动多相时钟产生电路非常适合应用于各类高速高精度ADC中以提供多相低抖动时钟。

[1]Chai Yun,Tsorng Wu jieh.A 5.37 mW 10 b 200 MS/S Dual-path Pipeline ADC[C].IEEE ISSCC Digest,2012: 462-464.

[2]Huang Yen-Chuan,Lee Tai-Cheng.A 10 b 100 MS/s 4.5 mW Pipelined ADC with a Time Sharing Technique[C]. IEEE ISSCC Digest,2010:300-302.

[3]Sung-Rung Han,Shen-Iuan Liu.A 500 MHz 1.25 GHz Fast-Locking Pulsewidth Control Loop With Presettable Duty Cycle[J].IEEE Journal of Solid-State Circuits,2004, 39(3):463-468.

[4]Q Du,J Zhuang,T Kwasniewski.A low-phase noise,anti harmonic programmable DLL frequency multiplier with period errorn compensation for spur reduction[J].IEEE Trans Circuits Syst.II,Exp.Briefs,2006,53(11): 1205-1209.

[5]于宗光,陈珍海,吴俊,邹家轩,季惠才.一种基于伪随机动态补偿的12位250 MS/s流水线ADC[J].东南大学学报(自然科学版),2014,44(5):902-906.

Low-Jitter Multi-Phase Clock Generator for High Speed Pipelined ADC

DAI Lixin1,FENG Likang1,HONG Guodong1,CHEN Zhenhai2,YE Aimin3(1.Huangshan triple seven electronics Co.,Ltd.,Huangshan 245041,China;2.China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214072,China;3.Jiangxi electric power company,Nanchang 330096,China)

A Low jitter multi-phase clock generator for high speed pipelined ADC is presented.In order to reject the clock jitter,the high sensitivity differential clock input structure and clock receiver is used.A 12-bit 250 MSPS pipelined ADC based on the proposed sub-stage circuit is presented.The ADC is manufactured in 0.18 μm 1P5M 1.8 V CMOS process,with a die area of 2.5 mm2.The test result shows that the ADC achieves an SNR of 69.92 dB,an SFDR of.81.17 dB,an INL of-0.4 to+0.65 LSB,a DNL of-0.2 to+0.15 LSB and a power consumption of 320 mW for 20 MHz input at full sampling speed.

pipelined analog-to-digital converter;clock generator;clock receiver

TN402

A

1681-1070(2017)02-0025-03

戴立新(1967—),男,安徽黄山人,现任黄山市七七七电子有限公司董事长兼总经理,祁门县电子行业协会副会长,1992年起一直从事功率半导体芯片和集成电路的研发与制造工作,在该领域获得国家发明和实用新型等专利12项。

2016-9-30