一种低功耗带隙基准电压源的设计

2017-02-27胡成煜顾益俊李富华

胡成煜,顾益俊,李富华

(苏州大学,江苏苏州215000)

电路设计

一种低功耗带隙基准电压源的设计

胡成煜,顾益俊,李富华

(苏州大学,江苏苏州215000)

设计了一种工作在亚阈值区无运放结构的CMOS带隙基准电压电路。通过使用线性区工作的MOS管取代传统电阻,使电路工作在亚阈值区,结合无运放设计,极大地降低了功耗。采用0.35μm CMOS工艺,在室温27℃、工作电压3 V的条件下进行仿真,输出基准电压1.2086 V,偏差在4 mV内,工作电流仅为1.595 μA,功耗仅为4.785 μW。在-50℃到120℃的温度范围内温度系数为17.3× 10-6/℃。该带隙基准电压电路具有低功耗、宽温度范围、面积小等特点。

带隙基准;亚阈值;低功耗;无运放;温度系数

1 引言

基准电压源是各种模拟或数模混合集成电路中极其重要的模块,广泛应用于A/D(D/A)转换器、开关电源、线性稳压器、电源充电和传感器接口等电路中。这些基准受电源、温度或者工艺参数的影响很小,为电路提供一个相对稳定的参考电压或电流,从而保证整个模拟电路稳定工作。随着便携电子设备的发展,电池续航能力成为制约发展的关键因素,因此低功耗的带隙基准电压源电路得到广泛的发展。在有运算放大器的带隙基准电路中,运算放大器的失调电压是造成温度系数非零的最主要因素,并且运放的存在也要消耗电流[1]。与其相比,无运放结构的基准电路功耗更低。

本文在传统无运放带隙基准电压源的基础上做了进一步改进,利用亚阈值MOSFET的特性,设计了一种结构更加简单的工作在亚阈值区无运放的基准电压源电路,基于以上特点实现很小的功耗和更小的芯片面积。

2 传统无运放带隙基准电压源

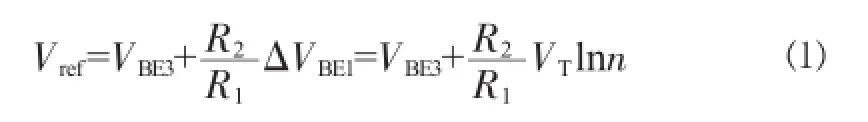

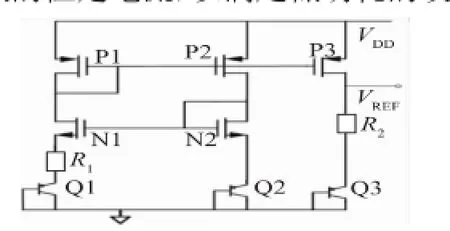

图1是传统无运放带隙基准电压源电路的结构[2],P1、P2、N1、N2组成反馈环路,迫使两路的偏置电流相等。结果,两个晶体管发射极电压必须由电阻R1决定。R1上的电压等于Q1和Q2的基极-发射极电压之差ΔVBE1。这里ΔVBE1可用VTlnn表示,其中VT为热电压,n为Q1和Q2的发射极面积之比。设N1、N2的宽长比相等,P1、P2、P3的宽长比相等,则带隙基准电压为:

由式(1)可知,只要选取适当的电阻R2、R1和n值,Q3基极-发射级电压VBE3的负温度系数就可以抵消ΔVBE的正温度系数,即可得到与温度无关的基准电压Vref。

无运放的带隙基准电路能大大降低电源敏感性以及对器件及工艺的依赖程度,同样得到了零温度系数的带隙基准电压。又因为所有电流损耗都直接用于产生Vref,因此降低了功耗。同时因使用的CMOS管子个数较少,芯片面积有了较大的减小。

但是此电路中的MOS管均工作在饱和区,电流往往超过几个微安。又由于P1、P2、P3的沟道长度调制效应,输出基准电压精度并不能得到保证。为了进一步降低功耗,本文使用了一种工作于亚阈值区的电路结构,利用两个MOS管栅极-源极电压差,形成具有正温度系数的恒定电流,以满足低功耗的设计要求。

图1 传统无运放带隙基准电压源电路

3 改进的带隙基准电压源电路

3.1 亚阈值区MOSFET的特征

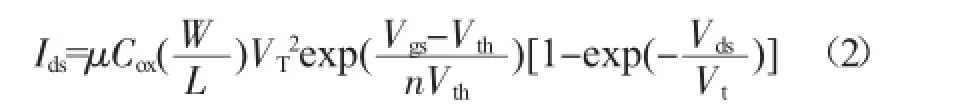

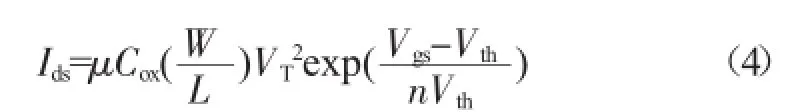

工作于亚阈值区的MOSFET的特征类似于双极型晶体管,其漏电流随栅源电压成指数变化[3]。其特征公式如下:

其中,n是斜率因子,μ是迁移率,VT是热电压,Vds是漏源电压,Vgs是栅源电压,Vth是阈值电压,Cox是栅氧电容,T是温度,有:

μ(T0)是基准温度的迁移率,1≤m≤2;

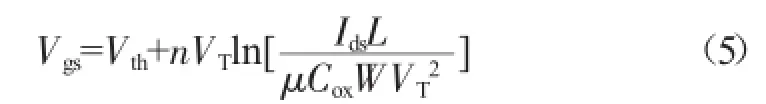

如果Vds>>VT,公式中的末项可以忽略,得到

并推导得到

其中,ln运算中的项远小于1,则第二项可以忽略。因此,阈值电压的负温度系数导致栅源电压也是负的温度系数。

在亚阈值区工作的MOS器件,其电流和Vgs/nVT的指数成正比,可以通过将两个MOS器件栅源电压同时加在一个电阻上,取其电压差,即可得到与热电压成正比的正温度系数项[4]。

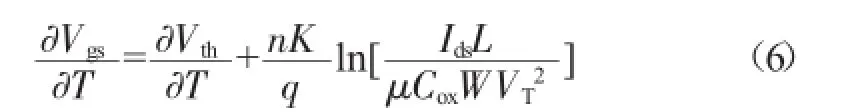

假设电流为常数,m取2,Vgs对T的微分有

图2 工作于亚阈值区的带隙基准电压源电路

3.2 工作于亚阈值区的带隙基准电压源电路

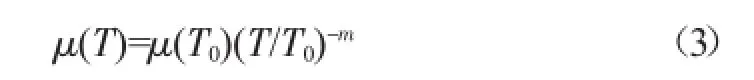

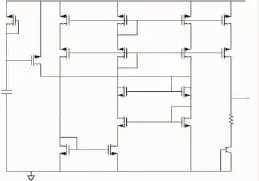

图2是工作于亚阈值区的带隙基准电压源电路的结构。P1、P2、N1、N2组成的电流镜形成一个封闭回路,其起始回路增益大于1。因此,在两个支路中的电流将不断增加,直至达到平衡。P1、P2、N1、N2工作于亚阈值区,用工作于线性区的NMOS器件N3代替电阻,取得正温度系数的恒定电流。其他器件均工作于饱和区。

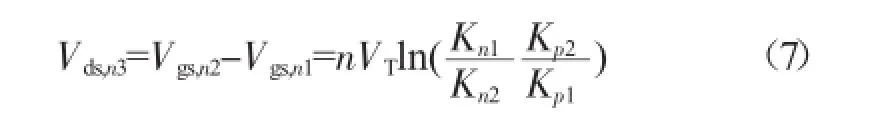

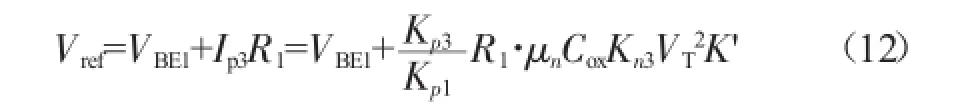

由分析可知,N3上的电压降为:

其中,K表示各管的W/L比。

由于N3工作在线性区,则:

得到:

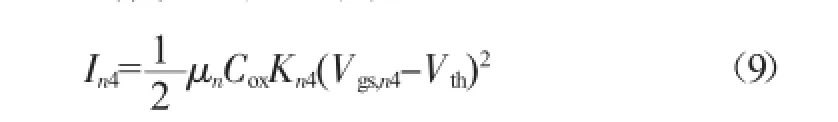

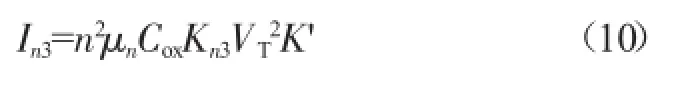

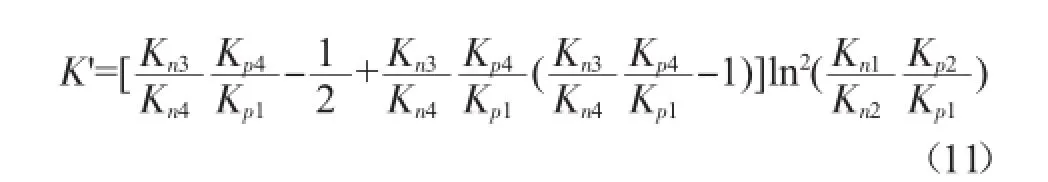

由(7)、(8)、(9)式可得:

式中:

而N4工作在饱和区,则:

式中,第一项具有负温度系数,第二项具有正温度系数。适当选择R1、Kn1、Kn2、Kn3、Kn4和Kp1、Kp2、Kp3、Kp4的值,在一定温度下,就可以使Vref的温度系数补偿为零。

然而由于使用的是简单电流镜,且P1、P2和P3有沟道长度调制效应,当电源电压发生变化时,Vref会受到较大影响。又由于N1和N2栅源电压的失配,这样两支路PTAT电流不能完全一致,输出电压Vref的精度同样受到影响[5]。

共源共栅结构具有较好的电源电压抑制比,同时电路PTAT电流匹配性也更好。在电路中采用共源共栅结构来提高Vref的精度,同时还能提高输出电压的PSRR[6]。总体来说,共源共栅形式经常被用于在几乎所有的工艺中来改善参考电路的性能。共源共栅形式的主要限制是它增加了让所有晶体管工作在放大区所需的最小电源电压。

3.3 启动电路

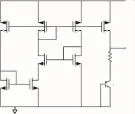

在基准产生电路中,由于自偏置结构的存在,往往在电源电压VDD接通的瞬间存在零电流简并态,一个零点和一个正常工作点。为保证整个电路在电源接通后能够正常工作,设计了启动电路。启动电路由S1、S2和C1组成。当电源电压VDD由零开始上升的时侯,由于S2的栅极电位处于低电平,S2先导通,则给自偏置管N6一个启动电流,直到VDD上升到Vth,则S1导通,给C1充电,S2栅极电位开始变高,最终关断S2,完成整个启动过程。此启动省去了大阻值的限流电阻,而且正常工作时没有直流电流,降低了整个基准电压源的功耗,节省了芯片面积。改进后的电路如图3所示。

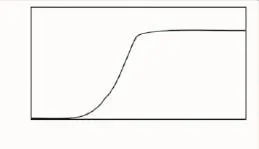

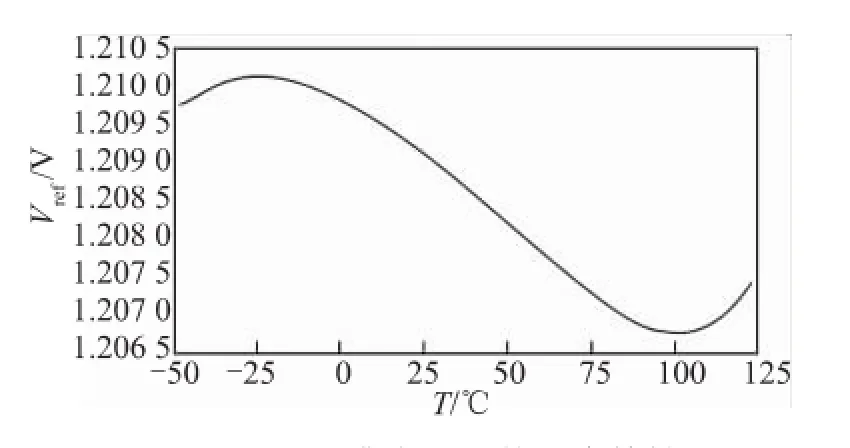

4 仿真结果

改进的无运放亚阈值带隙基准电压源电路如图3所示。电路采用Nuvoton 0.35 μm 3 V/5 V 2P3M BCD工艺,采用Cadence Spectre仿真工具进行仿真。进行直流电压扫描,电源电压范围从0 V到3 V,仿真结果如图4所示。从图4可知,电路在直流电压1.4 V左右时即可工作,输出电压为1.2086 V,并且在1.4 V到3 V的范围内输出结果均稳定。图5所示是供电电压从0 V到3 V范围内电路消耗的总电流的仿真图。从图5可知,当电路稳定工作后,工作电流仅为1.595 μA,功耗仅为4.785 μW。在3 V的工作电压下,在-50℃~120℃温度范围内进行温度扫描,仿真结果如图6所示,基准电压在1.206~1.121 V之间变化,温度系数约为17.3×10-6/℃。

图3 改进的无运放亚阈值带隙基准电压源电路

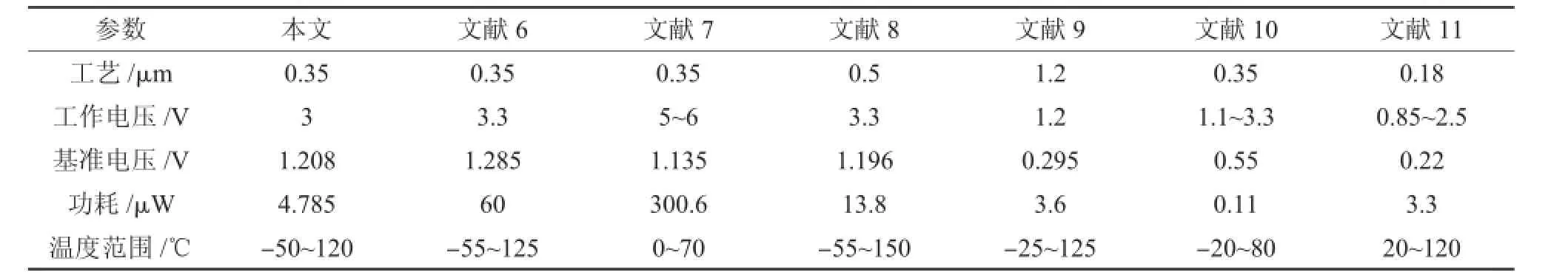

表1是相关文献提出的低功耗带隙基准电压源和本文设计的带隙基准电压源性能的对比数据。与文献[6]、[7]、[8]相比,本文提出的方案功耗更低。与文献[9]、[10]、[11]相比,本文提出的方案具有更宽的温度范围。由此可见,本文提出的带隙基准电压源在综合考虑低功耗和温度范围上更具优势。

图4 基准电压随VDD变化的仿真

图5 功耗电流随VDD变化的仿真

图6 基准电压源的温度特性

表1 其他低功耗带隙基准电压源与本设计的性能对比

5 结论

设计了一种工作于亚阈值区无运放的带隙基准电压源,使用工作在线性区的MOS管取代传统电阻,降低功耗并减小了芯片面积。在室温27℃、3 V工作电源下,输出基准电压1.2086 V,工作电流仅为1.595μA,功耗仅为4.785 μW。在-50~120℃温度范围内基准温度系数为17.3×10-6/℃,具有功耗低、面积小和温度范围宽的特性。

[1]Paul R Gray.模拟集成电路的分析与设计第四版[M].张晓林,等译.北京:高等教育出版社,2005:308.

[2]毕查德·拉扎维.模拟CMOS集成电路设计[M].陈贵灿,等译.西安:西安交通大学出版社,1995:313-314.

[3]Adl A H,El-Sankary K,El-Masry E.Bandgap reference with curvature corrected compensation using subthreshold MOSFETs[C].IEEE International Symposium on Circuits and Systems.2009:812-815.

[4]Allen P E.CMOS模拟电路设计[M].王正华,译.北京:科学出版社,1995:571-578.

[5]文武,文治平,张永学.一种高精度自偏置共源共栅的CMOS带隙基准源[J].微电子学与计算机,2008,25(8): 216-220.

[6]邹勤丽,汤晔.一种低功耗无运放的带隙基准电压源设计[J].电子与封装,2015,15(2):22-24.

[7]祁琳娜,唐宁,翟江辉,等.一种低温漂低功耗的简易带隙基准电压设计[J].电子设计工程,2010,18(4):147-148.

[8]代赟,张国俊.一种高性能的亚阈值基准电压源设计[J].微电子学与计算机,2013,30(5):108-111.

[9]Giustolisi G,Palumbo G,Criscione M,et al.A low-voltage low-power voltage reference based on subthreshold MOSFETs[J].Solid-State Circuits,IEEE Journal of,2003, 38(1):151-154.

[10]Hirose T,Ueno K,Kuroki N,et al.A CMOS bandgap and sub-bandgap voltage reference circuits for nanowatt power LSIs[C].Solid State Circuits Conference(A-SSCC),2010 IEEE Asian.IEEE,2010:1-4.

[11]Huang P H,Lin H,Lin Y T.A Simple Subthreshold CMOS Voltage Reference Circuit With Channel-Length Modulation Compensation[J].Circuits&Systems II Express Briefs IEEE Transactions on,2006,53(9): 882-885.

作者简介:

周昊(1986—),男,江苏盐城人,毕业于西北工业大学材料学专业,现于中国电子科技集团公司第55研究所封装事业部工作。

A Design of Low-Power Bandgap Voltage Reference Circuit

HU Chengyu,GU Yijun,LI Fuhua

(Soochow University,Suzhou 215000,China)

The paper presents a non-operational amplifier bandgap reference circuit based on sub-threshold CMOS.Instead of traditional resistances,the MOSFET works in linear region and thereby greatly reduces consumption.The performance of temperature drift is improved.The circuit is manufactured in 0.35 μm CMOS process and simulated at 27℃and 3 V working voltage.The output reference voltage is 1.2086 V within a deviation of 4 mV;the current is about 1.595 μA;and the power consumption is only about 4.785 μW. And the temperature coefficient is 17.3×10-6/℃in the range of-50℃to 120℃.The bandgap voltage reference circuit is of wide temperature range,low power consumption,and small size.

bandgap reference;sub-threshold;low power consumption;non-operational amplifiers; temperature coefficient

TN402

A

1681-1070(2017)02-0013-04

胡成煜(1991—),男,河北沧州人,苏州大学硕士,主要研究方向为集成电路设计。

2016-9-20