基于IODELAY原语SAR载荷模拟器延迟单元设计

2017-01-13艾铁柱张宇坤

赵 君,艾铁柱,张宇坤

(中航工业西安航空计算技术研究所,西安 710065)

基于IODELAY原语SAR载荷模拟器延迟单元设计

赵 君,艾铁柱,张宇坤

(中航工业西安航空计算技术研究所,西安 710065)

针对星载合成孔径雷达中数传分系统测试时,需要进行接收数据时序拉偏测试需求,提出一种基于FPGA原语的SAR载荷模拟器延时单元设计方法,该延迟单元采用IODELAY原语,通过时序约束实现正反向时钟与数据时序拉偏功能,同时分析了FPGA内部逻辑资源约束对时序拉偏功能的影响;仿真与试验结果表明,基于该延迟单元的SAR载荷模拟器时钟与数据时序调整范围可达-6~6 ns,步进1 ns,系统运行稳定,满足设计要求。

星载合成孔径雷达;数传分系统;载荷模拟器;IODELAY原语

0 引言

随着1978年美国“海洋卫星”(SEASAT)的成功发射升空,作为全球第一颗合成孔径雷达(SAR)卫星,它掀开了空间微波遥感的新篇章,同时也引发了全球对SAR卫星的需求热潮。数传分系统是遥感卫星的重要组成之一,在卫星在轨运行过程中,数传分系统主要完成针对星上有效载荷捕获的高分辨率图像数据的接收、存储于传输[1 2]。

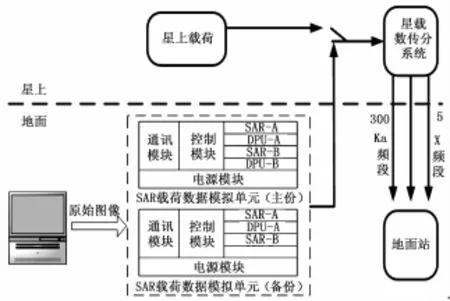

在针对星载数传分系统的测试过程中,真实数据源——星上有效载荷价格昂贵,容易受损,为了避免数传分系统在地面测试时,频繁对真实载荷进行操作而造成功能损坏,一般采用SAR载荷数据模拟器(简称SAR数据源),用来替换真实的星上有效载荷,模拟出符合卫星在轨运行时的数据及时序。SAR数据源应用方式如图1所示[3]。

本文针对星上实际应用中载荷与数传分系统间高速信号时序测试需求,依据测试信号类型进行时序控制分析,基于IODELAY原语实现受控延时单元设计,有效地减少系统维护复杂度与测试耦合度,并提高了SAR数据源系统的可扩展性。

图1 SAR数据源应用方式

1 SAR数据源时序测试原理

1.1 功能需求技术指标

本SAR数据源仅针对LVDS接口型数传分析进行测试,在数据传输过程中,一般包括时钟、门控和数据信号。在时钟上升沿时,若门控信号为有效,则此刻的数据为有效;若门控位无效,则数据为无效[4]。

通常情况下,要求时钟、门控和数据在同一时刻跳变,即在时钟上升沿跳变。同时跳变可以减少数据接收设备在数据采集时采集到错误数据。使得数据传输的可靠性提高。但是,在对数传分系统测试时,需要SAR数据源模拟实际星上工况。在实际工作中,时钟、门控和数据信号经过电缆传输后,会产生不同程度的相位偏移,该偏移的产生原因较多,如逻辑综合约束,PCB布线,寄生电容等。在测试过程中,为了尽可能模拟真实情况,需要SAR数据源将钟码关系进行拉偏,从而模拟时钟与数据不同步的情况,以此测试星载数传分系统数据接收功能的稳定性。

1.2 系统工作原理

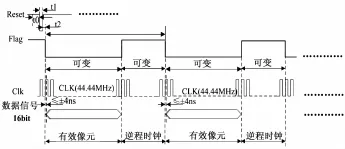

SAR模拟源通道与数据处理器交互信号包括2组LVDS数据传输接口,每组有四类信号构成:CLK、Flag、DATA [15:0]、RESET。模拟源功能如下:

1)SAR模拟源具有将自身内部存储的SAR数据从LVDS接口输出的功能;

2)模拟源具有19 bit(含时钟、门控和复位)位宽;

3)信号电平为LVDS,时钟频率44.44 MHz;

4)可以设置门控正程和逆程。

SAR模拟源与数传分系统接口时序关系如图2所示。

图2 SAR模拟源与数传分系统接口时序关系示意图

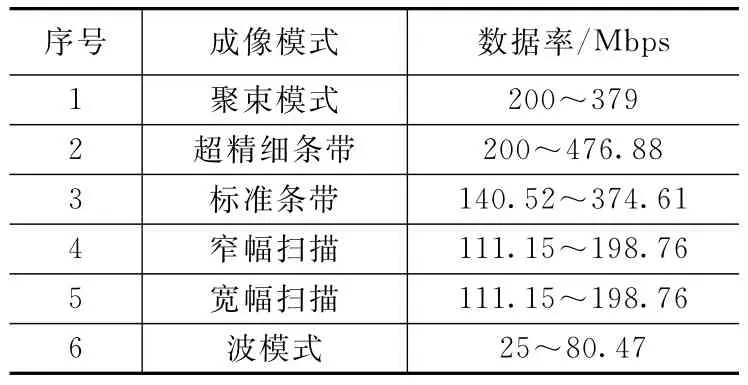

SAR模拟源工作模式及数据率如表1所示。

表1 SAR模拟源工作模式及数据率

其中:数据率是指单路数据速率,速率范围约定为每10帧跳变10%或20%(百分比可选择);针对波模式的间歇工作特性,约定工作时间(范围约1.27~1.43 s)和间歇时间 (范围约5.8~6.1 s)。

SAR模拟源接口参数如下:

1)时钟频率:44.44 MHz;

2)时钟上升沿对准FLAG信号下降沿,超前或者滞后flag下降沿小于4 ns;

3)Reset信号宽度为t1(不小于500 ns),信号超前稳定输出数据的时间为t2(不小于200 ns,不大于100 ms);

4)T0时间为SAR信源加电正常后到第一个正常的Reset低脉冲到来之前时间间隔,要求T0≥500 ms;

5)FLAG信号下降沿到来时开始传送SAR雷达数据,16 bit雷达数据并行传输,且有效门控下时钟周期为偶数;

6)时钟上升沿超前数据跳变沿,超前小于4 ns(时钟时延考验±6);

7)时钟占空比:45%~55%;

8)时钟连续不间断;

9)SAR模拟源输出至数传分系统的数据由2路16 bit的并行数据传输完成,数据处理器两个通道的图像数据计数器与图像的时间关系保持一致;

2 SAR数据源延时单元设计

为了满足时间偏移测试需求,本文提出调用Xilinx原语IODELAY和IDELAYCTRL方式实现产生纳秒级偏移的设计方案,其中IODELAY是输入/输出延迟单元,IDELAYCTRL模块是为IODELAY模块服务的,主要用于提供参考时钟。

2.1 IODELAY概述

每个I/O模块包含一个可编程绝对延迟单元,称为IODELAY。IODELAY可以连接到ILOGIC/ISERDES或OLOGIC/OSERDES模块,也可同时连接到这两个模块。IODELAY是具有64个tap的环绕延迟单元,具有标定的tap分辨率,64 个tap的环绕延迟单元产生的延时为参考时钟(Frequency used for IDELAYCTRL)的一个周期。IODELAY可用于组合输入通路、寄存输入通路、组合输出通路或寄存输出通路,还可以在内部资源中直接使用。IODELAY允许各输入信号有独立的延迟。按照类型可以分为IDELAY、ODELAY、IODELAY[5]。

当用作IDELAY时,数据从IBUF或内部资源输入,然后输出到ILOGIC/ISERDES,包括3种可用操作模式:

1)零保持时间延迟模式(IDELAY_TYPE=DEFAULT);

2)固定延迟模式(IDELAY_TYPE=FIXED);

3)可变延迟模式(IDELAY_TYPE=VARIABLE);

当用作ODELAY时,数据从OLOGIC/OSERDES输入,然后输出到OBUF,仅有一种固定延迟输出模式

当用作IODELAY时,将IOB配置成双向模式。IODELAY交替延迟输入通路和输出通路上的数据,包括两种工作模式:

1)固定IDELAY(IDELAY_TYPE=FIXED)和固定ODELAY模式;

2)可变IDELAY(IDELAY_TYPE=VARIABLE)和固定ODELAY模式;

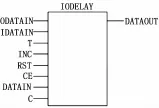

IODELAY基元结构如图3所示。

图3 IODELAY基元结构

其中:ODATAIN、IDATAIN、DATAIN均为被调节信号输入端,区别在于需要和IODELAY基元链接的端口类型不同。通过配置原语,选择其中一种模式来使用;DATAOUT为输出端,当输入使用ODATAIN时,输出端只能接到输出管脚,不能再做逻辑处理;T为三态控制信号输入脚;CE、INC、C用于可变延迟模式下调节延时的控制信号;RST为复位信号输入。

2.2 基于时钟偏移的延时单元设计

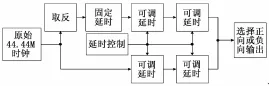

通过多次调用IODELAY原语,通过调整时钟。产生等效的负向偏移。使得输出的时钟延时接近3/4周期后输出,同时做微调,可以实现输出时钟偏移量为负1/4周期[6],其他延时量以此类推,延时单元实现流程如图4所示。

图4 延时实现流程图

2.2.1 正/负向延时输出设计

正向延时输出设计时,若IODELY的资源充足,可以使用200 M时钟作为参考时钟,连续调用两个可变IODELAY,两个可变IODELAY的初始值设为0,将其串联,设置其以tap递增模式变化。使用同一组控制信号控制器微调,可完成正向0~10 ns延时微调。完全满足0~6 ns延时微调。

若IODELY的资源不足,可以使用175 M时钟作为参考时钟,调用一个可变IODELAY,IODELAY的初始值设为0,设置其以tap递增模式变化。使用同一组控制信号控制器微调,可完成正向0~5.7 ns延时微调。

负向延时输出设计时,若IODELY的资源充足,使用200 M时钟作为参考时钟,先将原始时钟取反,接入一个连续固定IODELAY,再接入两个可变IODELAY。固定延时设置为18(计算得到),同时控制两个可变IODELAY,两个可变IODELAY的初始值设为63,设置其以tap递减模式变化。使用同一组控制信号控制器微调,可完成正向0~-10 ns延时微调。

若IODELY的资源不足,使用175 M时钟作为参考时钟,先将原始时钟取反,接入一个连续固定IODELAY,再接入一个可变IODELAY。固定延时设置为18(计算得到),同时控制可变IODELAY,两个可变IODELAY的初始值设为63,设置其以tap递减模式变化。使用同一组控制信号控制器微调,可完成正向0~-5.7 ns延时微调。

2.2.2 正负方向延时切换设计

由于正向延时和负向延时的产生方法不一样,所以调用两组IODELAY原语,第一组完成正向延时,第二组完成负向延时,最终按照配置的要求,二选一输出。在FPGA中,通过内部逻辑产生信号,信号被送到OBUF,再从OBUF输出到PAD,其中OBUF自身就具有逻辑选择功能。

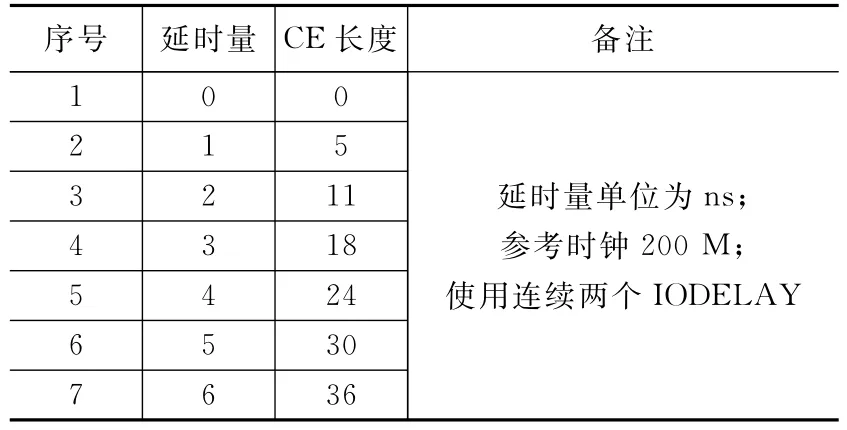

当需要将时钟拉偏时,首先通过解析延时配置参数,获取产生CE电平相应长度的控制量,然后对所有IODELAY进行复位,使其恢复到初始状态,最后根据表2配置的控制量产生相应长度的CE信号。

表2 CE参数配置表

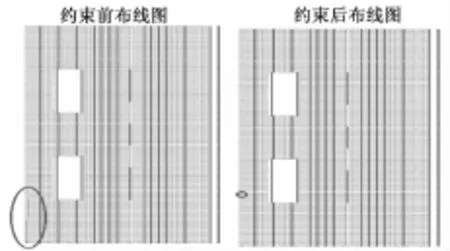

2.3 逻辑资源约束

在进行延时单元设计时,需要对IODELAY的位置进行约束,使其尽量接近输出端口,或者接近下一级逻辑单元。通过对时钟、数据等信号加上两个IODELY单元来实现延时控制的方法,需要进行如下设计配置:

1)为了满足最大偏移6 ns的要求,需要将两个IODELY串联使用;

2)为了满足IODELY的使用要求,在使用IDELAY模式时,IDELY单元的输出信号需要人为做一次逻辑后才能输出;

每个IO需要两个IODELY单元,因此布局布线时需要严格约束,且在使用前需要判断是所用到的IO附近的IOLEDY单元数量是否满足需求。在功能实现后,需要对IODELAY所在的位置进行时序约束,将IODELAY约束到IO的距离PAD最近的位置。图5为逻辑资源约束效果对比。

图5 逻辑资源约束

如图5所示,圈中线条为产生延时相关线路。在没有做约束的情况下,会默认优先调取X0Y0位置的IODELY。实际使用过程中,PAD的位置并不在X0Y0。这样会造成片内线路回绕,增大FPGA片内延时,影响时序拉偏测试精度。

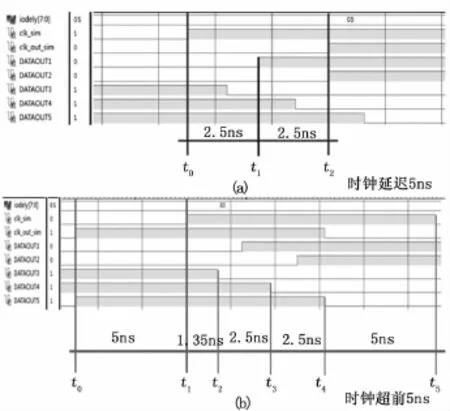

2.4 延时单元仿真

针对延时单元逻辑设计进行仿真,仿真结果如图6所示。图中DATAOUT1~DATAOUT5的变化情况一样,当偏移量为5时,会同时产生正向偏移和负向偏移,仅在clk_sim_ out最后输出时选择需要输出的信号。

图6 延时单元仿真结果

如图6(a)所示,iodely为8’h5时,需要将输出时钟延时5 ns输出。

1)t0,clk_sim为原始信号,

2)t1,经过一次可变IODELY之后,得到DATAOUT1,

3)t2,经过一次可变IODELY之后,得到DATAOUT2,如图6(b)所示,iodely为8’h85时,需要将输出时钟超前5 ns输出。

1)t1,将原始信号clk_sim取反输入一次固定IODELY。

2)t2,取反后的时钟经过一次固定IODELY之后,得到DATAOUT3,tap值为xx,参考时钟200 M,即产生1.35 ns延时;

3)t3,再经过一次可变IODELY之后,得到DATAOUT4,切控制器tap值为xx,参考时钟200 M,每个IODELY产生2.5 ns延时。

4)t4,再经过一次可变IODELY之后,得到DATAOUT5,切控制器tap值为xx,参考时钟200 M,每个IODELY产生2.5 ns延时。

5)t5,三次次叠加后得到了延时量等效为提前5 ns的clk _out_sim。

3 延时单元测试结果

由于固有延时的存在,因此当设施延时量为0时,输出量信号与延时信号存在一定的延时。通过校正,可以使延时量变为为0,但其缺点是使得负方向的可变化范围减小。

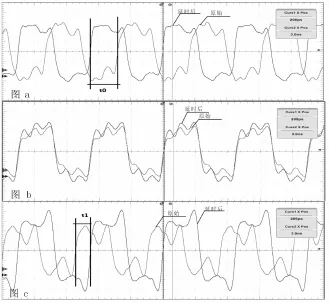

图7为SAR数据源输出时钟实测结果,下图蓝线偏移之后的时钟信号,红线为原始时钟信号。其中,图7(a)为延时值为0 ns时,原始时钟和延时时钟对比图(t0=6 ns),图7 (b)为延时值为-6 ns时(校正0点),原始时钟和延时时钟对比;图7(c)为延时值为10 ns时,原始时钟和延时时钟对比(t1=4 ns)。

4 结束语

本文提出与设计的基于IODELAY原语设计的延迟单元具有架构灵活、耦合度低和可扩展性强的特点,采用该延时单元可以实现SAR载荷模拟器时钟拉偏输出功能,测试结果表明,通过校正可以消除FPGA内传输固有延时误差,其延时功能可以满足SAR载荷模拟器针对星载数传分系统的信号拉偏测试需求,时序调整范围达到-6~6 ns,步进1 ns,LVDS接口输出时钟最高频率可以达到60 MHz。

图7 延时单元测试结果

[1]高洪涛,陈 虎,刘 晖,等.国外对地观测卫星技术发展[J].航天器工程,2009,18(3):84-92.

[2]张锐菊.航天器载遥感器与数传系统接口设计规范[S].2007.

[3]赵 宏,单庆晓,肖昌炎,等.遥感卫星数传基带数据模拟源的设计与实现[J].计算机测量与控制,2012,20(2):411-413.

[4]张文彬,邓云凯,倪 江.星载SAR目标回波信号模拟源的研制[J].计算机测量与控制,2005,13(3):265-266.

[5]Kilts S.Advanced FPGA Desgin:Architecture,Implementation and Optimization[M].孟宪元,译.北京:机械工业出版社,2009.

[6]Jurgenmattausch H,Matthiesen F.Amemory based high-speed digital delay line with a large adjustable length[J].IEEE Journal of Solid state E Circuits,1988,23(1).

Design of Delay Unit in SAR Load Simulator Based on IODELAY Primitive

Zhao Jun,Ai Tiezhu,Zhang Yukun

(Xi′an Aviation Institute of Computing Technology,Aviation Industry Corporation of China,Xi′an 710065,China)

In allusion to the requirement of timing perturbation between data and clock,which is in process of testing data transmission subsystem of spaceborne synthetic aperture radar(SAR),a new design of SAR load simulator,which is based on delay unit with FPGA primitive,is proposed in this thesis.For testing data transmission subsystem,the delay unit,completing timing perturbation between data and clock,consists of IODELAY primitive by timing rules.And it also analyzes the influence of the logic resource constraint in FPGA on the timing perturbation function.Finally,the performance and robustness are assessed through the simulation and test,whose result shows that the range of timing perturbation is from-6ns to 6ns with 1ns step.The system runs stably and meets the design requirements.

spaceborne synthetic aperture radar;data transmission subsystem;load simulator;IODELAY primitive

1671-4598(2016)08-0240-04

10.16526/j.cnki.11-4762/tp.2016.08.066

:TP957.51

:A

2016-02-23;

:2016-03-12。

航空科学基金-青年基金(2014ZD31006)。

赵 君(1982-),男,博士,一站博士后,高级工程师,主要从事新型机载机电系统嵌入式智能控制、机电系统综合仿真与评估技术方向的研究。