基于环形压控振荡器的电荷泵锁相环设计

2017-01-12何知龙郭裕顺

何知龙++郭裕顺

摘 要:在阐述了电荷泵锁相环的工作原理、分析和设计方法的基础上,结合环路稳定性和相位噪声两方面因素对锁相环电路进行了建模及分析。介绍了锁相环的系统级参数设计到电路设计的完整流程。首先利用Verilog-A语言建立了一个考虑各电路模块主要非理想因素的较为精确的锁相环行为级模型,然后进行单元电路的设计,考虑了温度变化对环形压控振荡器和锁相环系统的影响并分别进行了温度补偿。采用Cadence公司的Spectre-RF系列软件进行仿真,最后得到的锁相环输出频率范围为150 MHz~350 MHz,相位噪声为-113.8 dBc/Hz(振荡频率为240 MHz,频偏为2 MHz时),均方根抖动为3.65 ps,锁定时间小于3 μs,可为高速数字电路产生低抖动的片上时钟信号。

关键词:锁相环;行为级模型;温度补偿;相位噪声

中图分类号:TN453 文献标识码:A 文章编号:2095-1302(2016)11-00-04

0 引 言

锁相环(Phase Lock Loop,PLL)具有数据时钟恢复、消除时钟抖动、频率合成等多种用途。自从1965年PLL集成电路问世以来,PLL设计技术越来越成熟,从分立器件到集成电路,从双极型工艺到CMOS技术[1]。当前PLL的研究热点主要集中在低相位噪声、低杂散、高集成度、低电压、低功耗还有温度补偿等方面。在具体设计时,上述这些因素需要相互折衷以满足特定的应用要求。

本文的目的在于设计一个为高速数字电路产生低抖动片上时钟信号的PLL,要求输出的频率范围为150~350 MHz,均方根抖动(jitter_rms)小于5 ps,锁定时间小于3 s。

1 PLL系统级建模及设计

锁相环是一个反馈系统,本文所采用的三阶电荷泵锁相环主要由鉴频鉴相器(PFD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)和分频器(DIV)组成,其组成如图1所示。PFD将参考信号和分频输出信号两者的相位差转化为开关脉冲以控制CP的充放电,CP再将这种间断的电流提供给LPF,为其进行充放电来增大或者减小压控电压,从而动态控制VCO的振荡频率,使其最终达到平衡,锁定后压控电压保持不变,环路锁定在一个固定的输出频率上。

为了在设计过程中及时了解锁相环的整体性能,本文采用基于Verilog-A的行为建模方法,用Verilog-A建立了一个考虑各电路模块主要非理想因素的较精确的行为级模型[2],包括如下非理想因素:

(1)PFD、Divider模块的传输时延和同步相位抖动,信号的上升时间和下降时间[3]。

(2)在环路锁定过程中,由于刚开始CP输出压控电压比较小,电流源MOS管还未完全饱和,CP电流随压控电压线性增加直至电流源MOS管饱和,电流值ICP不变,整个过程可以在Verilog-A的行为级代码中用一个分段函数来表示,即

(1)

其中输出压控电压Vctrl的单位为V,ICP的单位为A,其对应的函数图像如图2所示。

(3)环路锁定之后CP充放电流源的电流不匹配,是因为在环路锁定后,由于电荷泵的非理想效应,在inc_high(充电电流源开关MOS管信号)和dec_high(放电电流源开关MOS管信号)同时为高电平(即充放电电流源MOS管同时导通)的导通时间内引入了充放电流不匹配的净电流输出mismatch_current[4]。

(4)由于MOS管在关断状态下漏电、低通滤波器中的电容漏电等,所以在行为级模型里,当inc_high和dec_high同时为低电平时,引入漏电流leak_current。

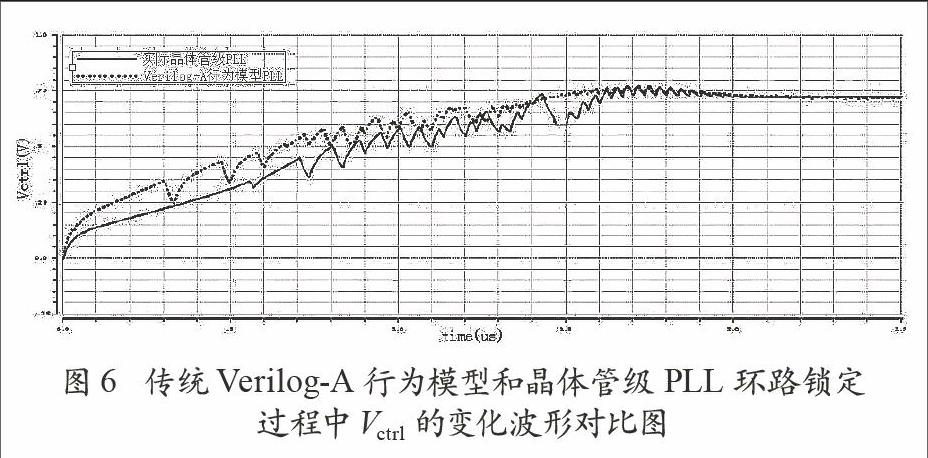

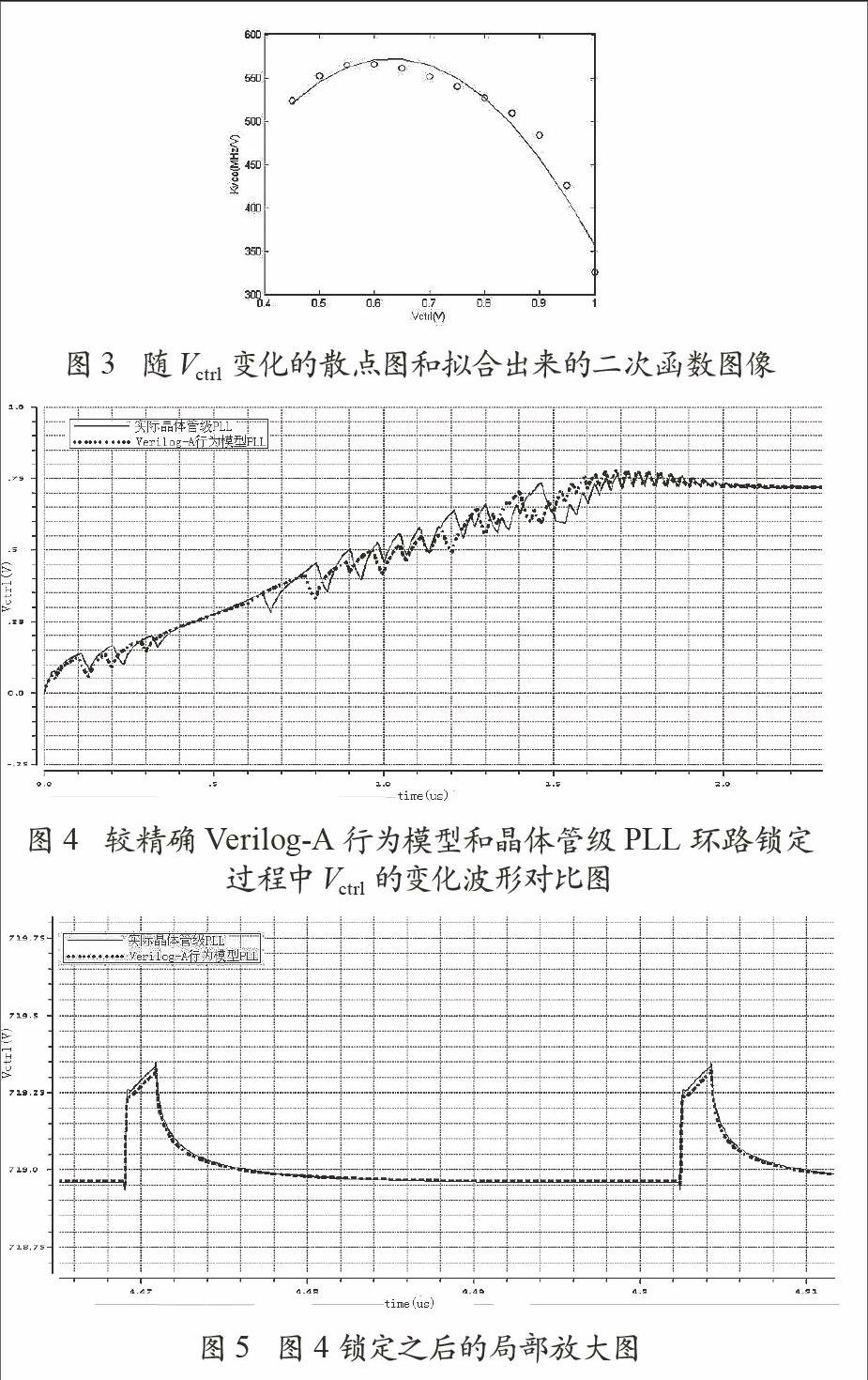

(5)VCO的压控增益KVCO与压控电压Vctrl的相关性[5],即KVCO不再是恒定的常数,其随Vctrl呈现类似抛物线的曲线特征,可以将KVCO随Vctrl的变化等效为一个二次函数,设这个二次函数为y=ax2+bx+c,可在VCO Verilog-A行为模型代码中用这个二次函数来表征KVCO随Vctrl的变化情况,在cadence中仿真电路级VCO模块其压控增益KVCO随Vctrl的变化,取一些离散点导入Matlab中并用二次函数拟合,如图3所示。由图3可以看到拟合出来的二次函数可以较好的模拟实际电路级中KVCO随Vctrl的变化情况。图4所示为考虑各电路模块的非理想因素之后的Verilog-A行为模型PLL与实际晶体管级PLL环路锁定过程中的压控电压Vctrl变化波形图对比,图5所示为图4锁定之后的局部放大图,图6所示为传统Verilog-A行为模型PLL与实际晶体管级PLL环路锁定过程中的压控电压Vctrl变化波形图对比。对比图4及图6可以看出,与传统理想行为模型PLL相比,较精确的行为模型PLL不管是环路的锁定过程、锁定时间还是锁定之后压控电压的周期性纹波都和实际晶体管级PLL较吻合。

2 PLL主要电路模块设计

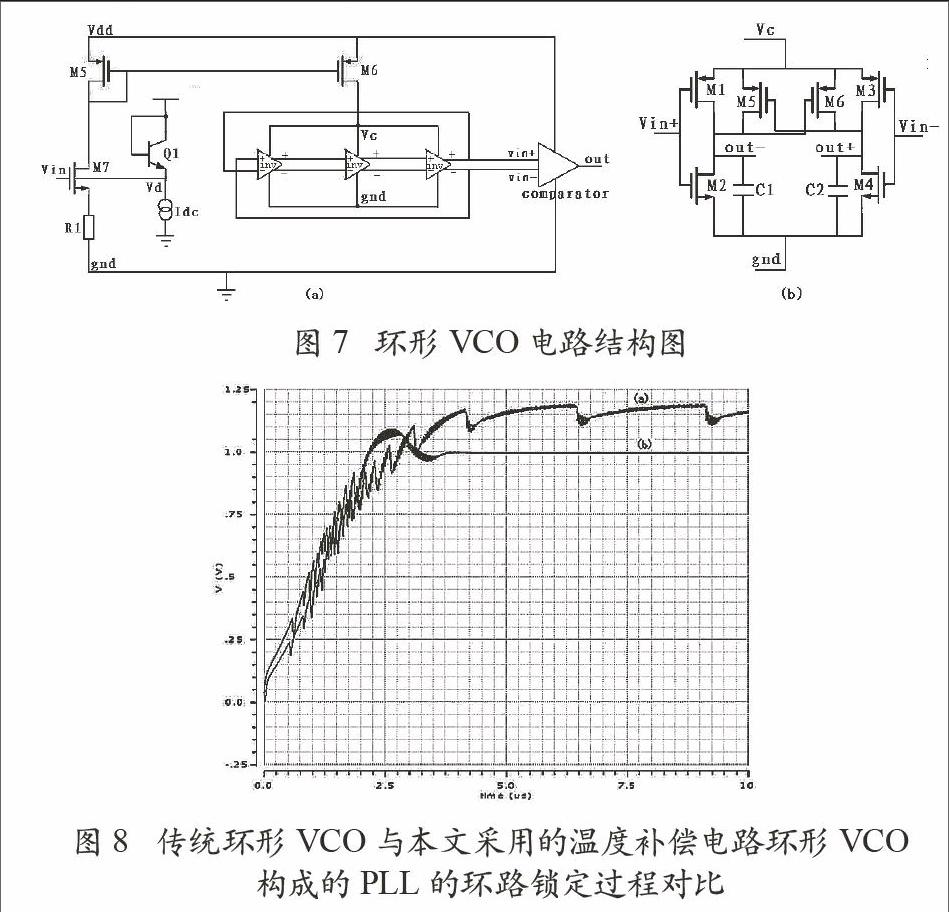

本文设计的环形VCO电路如图7所示,其中图7(a)表示环形VCO全电路结构图,图7(b)表示图7(a)中的延迟单元inv。该环形VCO使用了电流控制环形压控振荡器,并且是电压转换为电流(V-I)的结构。由于采用电流镜结构(图7(a)中的M5、M6),振荡器偏置电流受电源电压波动的影响较小,从而减小了电源噪声对环形VCO相位噪声的影响。本文采用图7(b)所示的延迟单元结构,这种结构集合了饱和单端反相器型CMOS环形VCO和非饱和差分对型CMOS环形VCO两者共同的优点,M1,M2构成反相器,M3,M4亦如此,从而形成差分输入差分全摆幅输出的反相器延迟单元,既克服了单端反相器电源和地等共模噪声的影响,又提供了全摆幅的输出振荡信号,从而优化了相位噪声。M5,M6在这里构成了正反馈加速管子的充放电从而减小延迟单元的延迟时间使振荡频率更高,并且这里的正反馈加速了管子的转换时间,使充放电管子的转换时间减小从而更快到达饱和。众所周知,在饱和状态下的噪声注入比在转换状态下对相位噪声的影响更小,因此进一步优化了VCO的相位噪声。输出端加负载电容C1,C2的目的是减小衬底噪声对频率抖动的影响,M2,M4管的源衬电容和漏衬电容很大程度上决定了延迟单元时间常数RC中C的取值,而源、漏衬电容值随衬底的电势发生变化,当衬底有噪声时,衬底电容发生改变因而出现频率抖动,而固定电容C1,C2的加入可以减小这种影响。

该环形VCO电路的振荡频率容易随温度发生变化,当PLL的环路锁定在某一个固定频率时,压控电压Vctrl保持不变,但当温度发生变化时,比如温度升高导致VCO的振荡频率降低,这时环路为了维持锁定,需要增大Vctrl的值(压控增益Kvco>0)从而保持VCO的振荡频率不变,当将Vctrl的值增大到一定程度时,可能会使压控电压Vctrl脱离调谐曲线的线性范围,甚至在调谐曲线上找不到所需频率,导致环路永久失锁。为此我们为它增加了一个温度补偿电路[6-9],在温度升高时,M5~M7的偏置电流增加,这样就能增加为延迟单元充电的电流,减小延迟时间,提高振荡频率。温度补偿电路的设计通过给图7(a)中的M7管的衬底单独提供一个偏置电压(图7(a)中的Vd)实现。该偏置由一个NPN管串联一个电流源Idc构成,由于NPN管基极发射极电压Vbe的负温度系数特性,所以端电压Vd呈现正温度系数特性,即此偏置电压Vd随温度的升高而增加。由于温度升高给衬底提供的偏置电压增加从而使M7管的阈值电压减小,而M7管的过驱动电压增加导致M7管的漏电流增加,从而补偿了因温度升高导致的M7管漏电流减小现象。

传统的未加温度补偿电路环形VCO与本文采用的温度补偿电路环形VCO在温度T=130℃时的仿真闭环PLL的环路锁定过程如图8所示,图8中曲线(a)表示传统未加温度补偿电路环形VCO构成的PLL环路锁定过程,可以看到在极端温度环境下(T=130℃)环路根本无法锁定。曲线(b)表示本文采用的温度补偿电路环形VCO构成的PLL环路锁定过程,可以看到环路依旧正常锁定。这验证了本文对环形VCO采用温度补偿电路的必要性。

3 PLL系统的温度补偿

对环形VCO的温度补偿解决了因极端温度引起的频率丢失问题,使得VCO在-40℃~130℃的温度范围中依旧能够线性工作在150 MHz~350 MHz的调谐频率范围内,但通过仿真发现,温度越高,VCO振荡在相同的频率时,压控增益Kv越小,具体变化情况如表1所列。在其他环路参数不变的情况下,环路带宽会变小,这样VCO的相位噪声贡献会变大,从而恶化了PLL输出的相位噪声,严重时会使环路相位裕度减小,系统趋向于不稳定。近似环路带宽的公式如下所示:

由于压控增益Kv随温度升高而减小,可以考虑提供一个PTAT电流即正温度系数的电流来补偿温度改变引起的环路带宽变化[10]。可求得一系列温度补偿所需的电流值,如表1中的第三行所列。

ICP可用一次函数ICP=kT+b来比较精确的拟合,其中k=0.5 A/℃,b=285 A。图9中同时绘出表1中ICP的数据散点图和一次函数ICP=0.5×T+285的图像,可以看到一次函数基本上和离散数据散点图吻合,即电荷泵提供的PTAT电流只要满足ICP=0.5×T+285就可以比较精确地对PLL的环路带宽进行温度补偿。

为了使电荷泵输出的电流满足ICP=0.5×T+285,可以先提供一个正温度系数的电流ICP1=0.5×T,再提供一个零温度系数的电流ICP2=285 A,之后将两路电流并联相加ICP=ICP1+ICP2。正温度系数参考电流源的电路结构如图10(a)所示,零温度系数参考电流源的电路结构如图10(b)所示。

传统锁相环未对PLL系统进行温度补偿,当T=130℃时,由表1可知Kvco=466 MHz/V(之前设置的Kvco为600 MHz/V),其他环路参数不变,环路带宽变为1.6 MHz(之前为2 MHz),仿真此时PLL输出的相位噪声[11-13]曲线如图11(a)所示,可以看到此时的系统环路带宽减小为1.6 MHz,对应的周期抖动均方根值jitter_rms =4.063 ps。本文设计的锁相环加入PLL系统的温度补偿电路后,再次仿真此时PLL输出的相位噪声曲线如图11(b)所示,可以看到系统的环路带宽又恢复为2 MHz(与常温下的系统环路带宽一致),此时对应的周期抖动均方根值jitter_rms =3.646 ps。可以看到加入PLL系统的温度补偿电路,PLL输出的相位噪声、周期抖动均方根值均与常温下T=27℃时保持一致,其性能不会随温度的升高而恶化。

4 结 语

本文阐述了电荷泵锁相环的基本工作原理、系统建模与设计方法,分析了其中主要电路模块VCO的设计。为提高锁相环的性能,设计中分别采取了一些有针对性的改进措施。从锁相环的环路稳定性和相位噪声入手,设计了一个用于高速数字时钟的锁相环系统,最后基于CMOS工艺给出了具体电路的设计和仿真结果。

参考文献

[1]白杨.一种新型电荷泵锁相环电路的设计[D].北京:北京工业大学,2015.

[2]Gabriele Manganaro, SU Kwak, SH Cho, et al. A behavioral modeling approach to the design of a low jitter clock source [J]. IEEE Trans. on Circuits and Systems II, 2003, 50(11) : 804-814.

[3]李建军.PLL-FS行为级建模仿真进行噪声和抖动性能预估的方法[J].集成电路应用,2007,16(4):46-50.

[4] LIU Lian-xi, YANG Yin-tang, ZHU Zhang-ming. System Design of PLL Based on Behavioral Model Using Verilog-A [J]. Chinese Journal of Electron Devices, 2004, 27(2) : 324-328.

[5]马哲,蔡敏.一种精确的锁相环IP模块行为级建模[J].半导体技术,2006,31(4):310-314.

[6]李小飞,刘宏,袁圣越,等.带温度补偿的低功耗CMOS环形压控振荡器设计[J].现代电子技术,2015,38(18):98-101.

[7]陈钰,洪志良,朱江.采用0.25um CMOS 工艺、适用于LVDS 驱动器的高性能多相时钟生成器的设计[J].半导体学报,2001,22(8):1069-1074.

[8]陈钰,洪志良.用于2.5 Gbps千兆以太网发接器的时钟倍频器设计[J].固体电子学研究与进展,2003,23(3):256-261.

[9]武威,万培元,侯立刚,等.一种具有温度补偿的时钟振荡器设计[J].固体电子学研究与进展,2014,34(6):555-558.

[10]樊勃,戴字杰,张小兴,等.SOC用400~800 MHz锁相环IP的设计[J].微电子学,2008,38(5):743-747.

[11]童姣叶,李荣宽,何国军.电荷泵锁相环的相位噪声研究[J].电子技术应用,2016,42(1):28-30.

[12] JY Ji, HQ Liu, Q Li. A 1-GHz Charge Pump PLL Frequency Synthesizer for IEEE [J]. Journal of Electronic Science and Technology, 2012, 10(4) : 319-326.

[13]Paolo Maffezzoni, Salvatore Levantino. Analysis of VCO Phase Noise in Charge-Pump Phase-Locked Loops [J]. IEEE Transactions on Circuits and Systems, 2012, 59(10) : 2165-2175.