改进的时钟偏斜误差校正方法的FPGA实现

2016-12-23王天明

聂 伟,王天明,邱 蓉

(北京化工大学 计算机系统与通信实验中心, 北京 100029)

改进的时钟偏斜误差校正方法的FPGA实现

聂 伟,王天明,邱 蓉

(北京化工大学 计算机系统与通信实验中心, 北京 100029)

利用改进的完美重构方法对多A/D采样系统的时钟偏斜误差校正方法进行了FPGA实现。采用自顶向下和模块化的设计方法,实现了多路采样数据的相位同步模块、数据位置映射模块、并行多相滤波器组模块以及多路数据合成模块。对完美重构方法中的滤波器组运用多相分解技术将其化为并行结构滤波器组,对输出数据采用流水线结构加法器组进行处理,降低了系统运算延迟,提高了系统的实时性。在MATLAB和ModelSim中进行仿真,结果表明了该实现的正确性和有效性。

时间交替采样;时钟偏斜误差;多相分解;FPGA

0 引言

在模拟信号采集中采样速率是其重要指标。传统单一A/D采样的不足是采样速率低,不能满足实际需求。为提高采样速率,现多采用时间交替并行采样技术,即TIADC(Time-Interleaved ADC)[1-4]。但是在多A/D采样系统中,由于时钟抖动以及A/D器件的离散性,系统存在时钟相位偏斜、增益和偏置误差,这些误差都具有随机性。

在这三个误差中,增益误差和偏置误差只需简单运算即可消除,而校正时钟偏斜误差却比较困难[3-5]。文献[5]提出的分数延迟滤波器法,需要过采样,占用很多的输入信号带宽;文献[6]提出了插值法,该方法运算量大,难以进行实时处理,主要用于离线校正;文献[7]中提出完美重构修正方法,其并行实现方式可带来很高的数据处理速率;文献[8]在完美重构基础上利用滤波器多相分解构建滤波阵列,对数据处理速率进行了有效提高。

本文在文献[8]的基础上,在FPGA中实现利用改进的完美重构方法实时校正时钟偏斜误差的系统结构。该系统利用FIFO对采样数据进行缓存及相位对齐,然后进行降速处理并对数据位置映射重置,再通过多相分解方法构建滤波器阵列对采样数据进行重构,最终将处理数据合成输出。这样不但有利于实时处理,还减少了系统的运算量[9]。

1 时间交替并行采样系统时钟偏斜误差校正方法

1.1 完美重构校正方法原理

时间交替并行采样对任意波形的采样示意图如图1所示。理想的多A/D器件采样时钟之间有相同的频率和固定的等间隔相差,但实际采样过程中,由于时钟抖动、传输路径延迟等因素使得各个通道间相对理想相差存在着一定的相位偏离,从而产生时钟偏斜差。

图1 任意波形时间交替采样示意图

时钟相位偏差会引起杂散频谱,经采样后的输出信号频域表示为:

(1)

图2 完美重构校正方法原理框图

如图2所示,带限模拟信号经多路A/D并行采样后将采样数据输入到滤波器组Fm(z)中,将每路输出数据累加就可以得到重构数据。图2中,Fm(z)可表示为:

(2)

其中,m=0,1,...,M-1,fm[k]是其滤波器系数,可以表示为:

(3)

1.2 改进的完美重构校正方法

为了使完美重构校正方法在数字电路实现高速实时的数据校正,把图2中的滤波器组用多相结构实现。可把Fm(z)表示为:

(4)

图3 重构滤波器的多相实现结构

如图3所示为滤波器组的多相实现结构。

它将每一路的重构滤波器分解为若干子滤波器,其中Fkm(z)就是Fm(z)的多相分量。图3中的F(b)(z)是m×m矩阵,可表示为:

(5)

最终的输出可表示为:

Y(z)=F(b)(z)X(z)

(6)

其中,

X(z)=[X0(z)X1(z)X2(z)...Xm(z)]T

(7)

Y(z)=[Y0(z)Y1(z)Y2(z)...Ym(z)]T

(8)

这里的X(z)是该系统的输入序列,Y(z)是X(z)经过多相结构滤波器组校正后的输出序列。

2 校正系统的FPGA设计实现

2.1 校正系统的FPGA设计实现

本设计选用Altera公司CycloneII系列的EP2C5芯片,采用原理图与VHDL(Very-High-Speed,Integrated Circuit Hardware Description Language)进行模块化设计。软件环境采用QuartusII,仿真工具为Modelsim。

利用前面介绍的改进方法在FPGA中进行设计,根据现有实验条件,设A/D通道数为4路,每路A/D转换精度为12位,每个通道的采样速率为50 MHz,系统最高采样频率200 MHz,输入信号频率为12.5 MHz。

根据参数及数据降速要求,现给出如图4所示的时间交替并行采样时钟偏斜误差校正电路的总体设计框图。

图4 时间交替并行采样系统校正电路总体设计框图

如图4所示,带限模拟信号xin(t)同时输入到4个采样时钟相位依次相差90°的A/D进行采样,然后将A/D的输出数据x0[n]、x1[n]、x2[n]、x3[n]送入FPGA进行数字处理。FPGA主要由数据缓存同步模块、数据映射模块、多相滤波器组、数据合路模块以及时钟产生模块组成。

2.2 校正系统各模块详细设计

2.2.1 数据缓存同步模块的设计

图5 四个通道写时钟的控制结构图

在该模块中采用四个FIFO来完成数据缓存和数据相位对齐,其中每个FIFO的写时钟与它对应通道的采样时钟一致。如图5所示,WEN为写使能信号,Wclk0、Wclk1、Wclk2、Wclk3分别是四个采样通道对应的写时钟,为使从4个FIFO中读出的数据同步并且保证第一个数据是从FIFO0中读出的,故在写使能信号有效之后用Wclk3作为同步的读时钟。

2.2.2 数据映射模块设计

此模块主要完成串并转换及数据顺序重置。串并转换的本质就是移位寄存并行读出的过程,该模块实现比较简单,每个通道只需要利用4个D触发器外加计数器即可。需要注意的是,输出数据是按照采样的先后顺序进行合成,所以第一路输入数据经串并转换后四路输出数据应为x0,x4,x8,x12;同理,得到其他三个通道共16路数据。

2.2.3 多相滤波器组的设计

该模块设计的重点是多相滤波器的参数,其电路实现比较简单。根据提供的时钟相位误差信息,在MATLAB中仿真确定滤波器的阶数为64。

利用式(3)可以计算出4个A/D通道每个通道对应的滤波器组的系数,对这16个滤波器的系数进行多相分解,得到16×16=256个子滤波器的系数,每个系数不为零的子滤波器的阶数都是4。

此16×16的滤波器阵列由式(5)可以表示为:

(9)

其中,每个元素Fj,i(z)代表一个子滤波器,可以由滤波器组里的Fi(z)计算得到,即:

(10)

(11)

式(10)中,Fi(z)代表每个通道的重构滤波器,式(11)中,fi[j+16·m]为滤波器系数,可以根据式(3)进行计算。依照式(6),滤波校正过程可表示为:

(12)

其中,Xi(z)表示16路输入数据,Yi(z)表示滤波后的16路输出数据。

分析可得,这个16×16的滤波器阵列只有3/4的滤波器系数不为零,故只需在FPGA中实现192个子滤波器即可。

依照式(12),在图6中给出了校正滤波器阵列数据流的示意图,在FPGA中易于实现。每个输出数据流由16个滤波器的输出相加得到,在FPGA中用流水线型加法器组实现16输入加法。

图6 误差校正模块结构图

2.2.4 数据合路模块的设计

数据合路模块的功能是实现16路12 bit的数据到1路12 bit的数据的转换。该模块工作输入时钟为12.5 MHz。由于最终16路数据串行输出需要200 MHz时钟,故通过PLL对系统输入时钟倍频,再用一个4 bit计数器作为选通信号来完成合路。

3 仿真及性能分析

3.1 数据缓存同步模块仿真

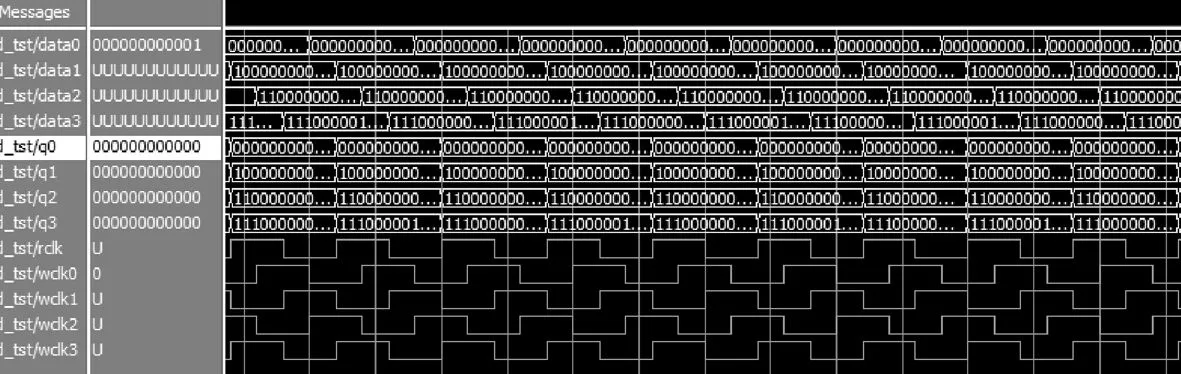

采用图4结构,产生4个相位相差90°的输入时钟,每路输入数据均为两个12 bit数循环输入。在QuartusII环境下进行VHDL实现,在Modelsim中对该模块进行仿真,得到图7所示仿真波形。

图7 数据缓存模块仿真图

图7中,4路数据data0~data3分别按照各自对应通道的时钟wclk0~wclk3进行输入操作,每个通道的时钟相位依次相差90°,4路输出数据q0、q1、q2、q3是在同一个读时钟rclk下读取输出,它们之间无相位差,rclk与wclk3频率相位一致,可以看出该模块程序实现了缓存同步功能,达到设计要求。

3.2 数据合路模块仿真

此模块需要把误差处理模块中的并行数据按照顺序高速串行输出,按照前面设计要求,在一个输入数据周期内串行输出16个数据。用VHDL语言描述数据合路模块并进行仿真,其结果如图8所示。

图8 数据合路模块仿真波形图

图8中,clk_in为输出时钟,它是经过对系统输入时钟倍频得到的,cnt是为了方便观察引出的计数端口,输出端y_out将16路并行输入数据y0~y15进行了串行输出,输出16个数据所需的时间与输入端单个数据周期相同,输入数据顺序与输出数据顺序一致,说明该模块设计正确。

3.3 多相滤波器组MATLAB与Modelsim联合仿真

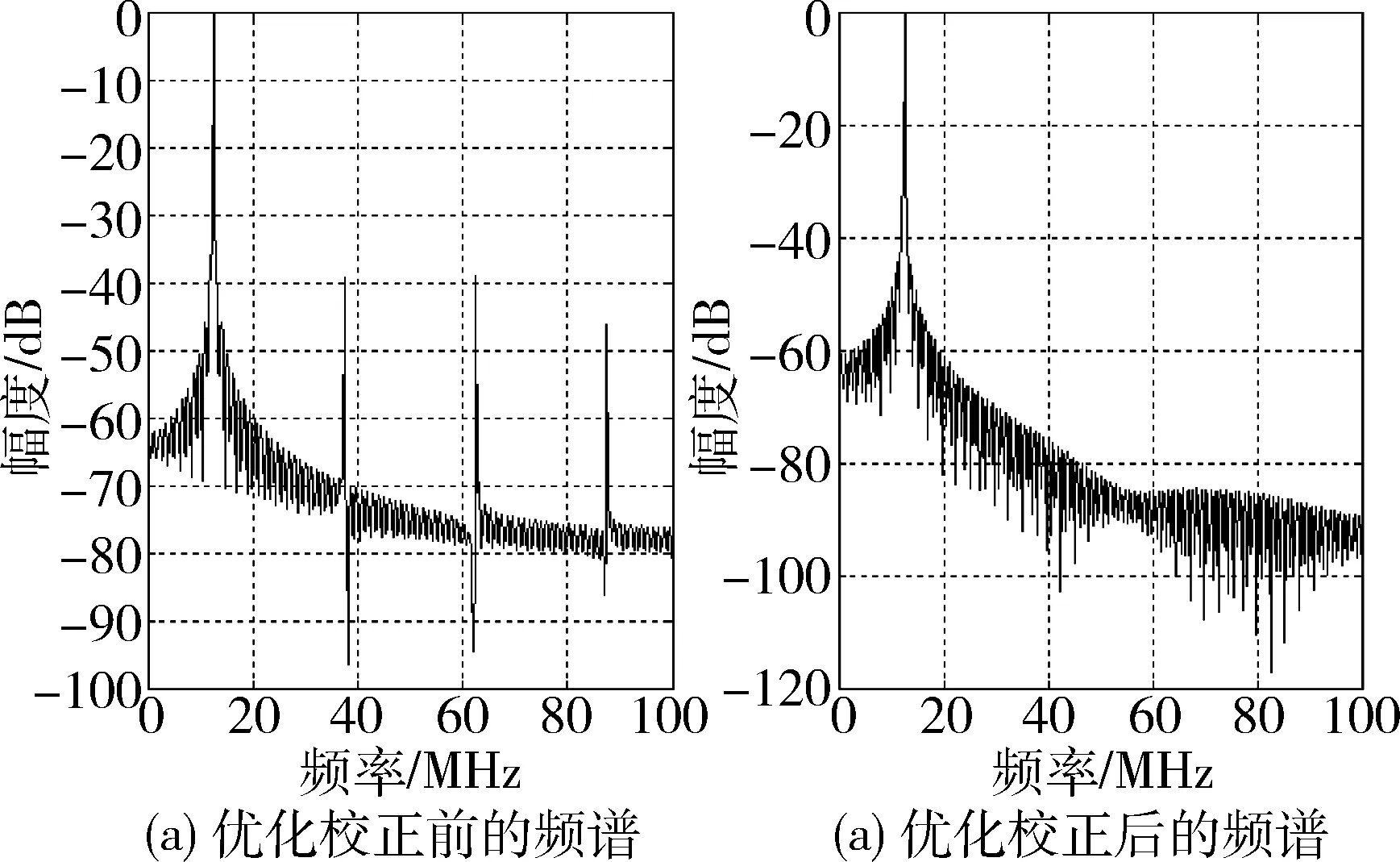

由于在ModelSim中只能进行时域数据波形仿真,无法看到频域变化,故采用ModelSim和MATLAB联合仿真。设置4个通道时钟偏斜误差分别为[0,-0.01,0.02,0.01]Ts,[0,-0.03,0.03,0.02]Ts,[0,-0.05,0.05,0.05]Ts三种情况。

在用VHDL实现了误差校正模块后,在Modelsim中对该模块进行仿真。按照仿真步骤,将MATLAB生成的正弦波采样数据送给ModelSim,得到未经校正的输入信号和校正后的输出信号,截图如图9所示。

图9 ModelSim仿真波形图

从图9中可以看到,经过该模块输出的正弦波相对于输入波形只是增加了延时,而输出的幅值基本不变,这是由滤波器引起的。在此图中从时域波形不能够看出该模块的校准性能。为了验证滤波器的校准功能,将输出信号导入到MATLAB中进行测试,得到校准前后信号频谱如图10~12所示。

图10 误差为[0,-0.01,0.02,0.01]Ts时优化校正频谱对比

图11 误差为[0,-0.03,0.03,0.02]Ts时优化校正频谱对比

图12 误差为[0,-0.05,0.05,0.05]Ts时优化校正频谱对比

从校正前和校正后的频谱可以看出,时间偏斜误差越大,杂散频谱幅度越高,此时该校正系统依旧能够滤除杂散频谱,保证采样的均匀性。

4 结束语

本文对改进的时间交替并行采样时钟偏斜误差校正方法进行FPGA设计并实现,在Modelsim中仿真表明各模块均能达到相应功能要求;在MATLAB仿真测试中可以看到,在不同时钟偏斜误差参数下,未滤波时相应杂散频点幅度随误差参数变化,误差越大,杂散频谱幅度越大,而经多相滤波阵列后均能够有效滤除杂散频谱,说明该方法正确有效,可以应用于需要多A/D采样的仪器前端。

[1] 黄武煌,王厚军,曾浩. 一种超高速并行采样技术的研究与实现[J]. 电子测量与仪器学报,2009(8):67-71.

[2] BLACK W C, HODGES D. Time interleaved converter arrays[J]. IEEE Journal of Solid-State Circuits, 1980, 15(6):14-15.

[3] 潘卉青. 高速TIADC并行采样系统综合校正技术研究[D]. 成都:电子科技大学, 2010.

[4] HUANG L, LIN B, ZHANG S. A digital-background TIADC calibration architecture and a fast calibration algorithm for timing-error mismatch[C]. ASICON '07. 7th International Conference on. IEEE, 2007:253-256.

[5] 李玉生. 超高速并行采样模拟/数字转换的研究[D]. 合肥:中国科学技术大学, 2007.

[6] 王吉林,郭钢,赵力. 高速数字示波器中的插值算法的研究[J]. 电子器件,2009,32(3):627-630.

[7] 秦国杰,刘国满,高梅国,等. 一种时间交替ADC时间失配误差自适应校正方法[J]. 仪器仪表学报,2013,34(12):2730-2735.

[8] 聂伟,邱蓉. 一种TIADC系统时钟偏斜误差的全并行校正方法[J]. 实验技术与管理,2015,32(4):47-51.

[9] 唐邵春. 基于时间并行交替技术的超高速高精度波形数字化研究[D]. 合肥:中国科学技术大学, 2012.

聂伟 (1960-),男,博士,副教授,主要研究方向: 软件无线电、通信信号处理等。

王天明 (1990-),男,硕士研究生,主要研究方向:信号处理技术、通信系统设计。

邱蓉 (1991-),女,硕士研究生,主要研究方向:信号处理技术。

The realization of improved clock skew error correction method on FPGA

Nie Wei,Wang Tianming,Qiu Rong

(Computer System and Communication Laboratory, Beijing University of Chemical Technology, Beijing 100029, China)

In this paper, the clock skew error correction of multi A/D sampling system is realized by using the improved perfect reconstruction method on FPGA. Using the top-down and modular design method, phase synchronization module of multi channel sampling data, data location mapping module, parallel multi phase filter bank module and multi-channel data synthesis module are realized. For the perfect reconstruction method, the multi phase decomposition technique is used to change the filter banks to parallel structure filter bank. The output data is processed by the pipeline structure adder. It can reduce the system operation delay and improve the real-time performance of the system. The correctness and effectiveness of the implementation are shown in the simulation results of ModelSim and MATLAB.

time interleaved sampling; clock skew error; polyphase decomposition;FPGA

TN74

A

1674-7720(2016)07- 0083- 04

聂伟,王天明,邱蓉. 改进的时钟偏斜误差校正方法的FPGA实现[J].微型机与应用,2016,35(7):83-86.

2015-12-07)