N漂移区减薄的BPL SOI LDMOS器件的耐压特性

2016-12-16杭州电子科技大学电子信息学院李阜骄张海鹏郝希亮

杭州电子科技大学电子信息学院 李阜骄 张海鹏 郝希亮 何 健 张 强

N漂移区减薄的BPL SOI LDMOS器件的耐压特性

杭州电子科技大学电子信息学院 李阜骄 张海鹏 郝希亮 何 健 张 强

为了提高横向小尺寸薄埋氧层BPL SOI LDMOS器件的横向耐压,提出一种N漂移区减薄的BPL SOI LDMOS结构。该结构在BPL SOI LDMOS N漂移区的上表面引入一个沟槽。当器件正向截止时,与原结构相比,新结构具有更高的横向耐压值和漂移区最优掺杂浓度。采用2维数值仿真工具TCAD对该器件结构仿真测试,结果表明与原结构相比,该结构横向耐压得到显著提高。

沟槽;N漂移区;BPL SOI LDMOS;横向耐压

0 引言

相比于体硅功率集成电路,SOI功率集成电路具有隔离性能更好、工作速度更高、抗辐射能力更强等优点,逐渐受到从业者的关注,其中关于SOI高压功率器件耐压值的提高是研究的热点之一[1-5]。在满足RESURF原理的基础上,当漂移区长度较短时,SOI LDMOS器件的横向耐压一般会低于纵向耐压。而在SOI横向高压功率器件中,击穿电压取决于横向耐压和纵向耐压中的较小者,所以漂移区长度较短的器件中,器件耐压值的大小一般取决于横向耐压值。传统SOI LDMOS结构通常是通过在较长的漂移区长度上利用场板技术[6]、横向变掺杂技术[7]等方式调整表面场分布来获取高的横向耐压值,但当漂移区长度较短时,上述技术的作用不甚明显。BPL SOI LDMOS结构利用N型漂移区与P埋层之间的反偏PN结承担器件绝大部分纵向耐压,获得了很高的纵向耐压值,解决了纵向耐压的问题[8],在漂移区长度较短时,器件横向耐压成为限制器件耐压的主要因素。针对该问题提出一种采用沟槽减薄N漂移区(Trench N-Drift,TND)的BPL SOI LDMOS结构来提高器件的横向耐压值。该结构通过在BPL SOI LDMOS的N漂移区上表面引入一个沟槽,利用沟槽的结构参数增加了电场积分路径,同时栅场板适当覆盖沟槽顶部,将横向峰值电场引入沟槽中,通过沟槽内低介电常数的填充物,阻止器件在该点发生击穿,以期能够有效提高器件的横向耐压。

1 TND BPL SOI LDMOS器件结构

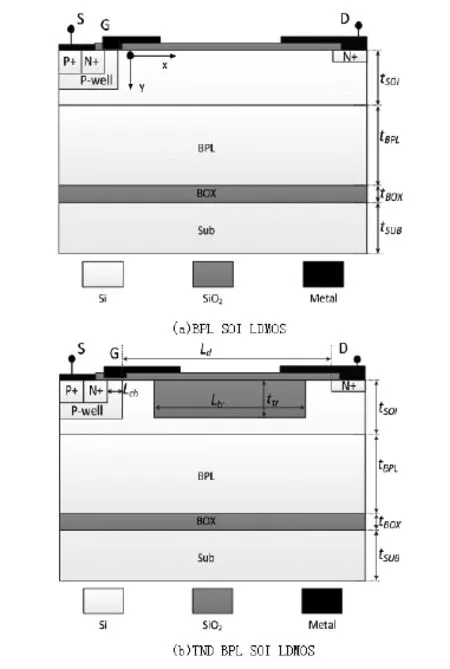

BPL SOI LDMOS结构和Trench BPL SOI LDMOS结构的横截面示意图如图1(a)、(b)所示。相对于图1(a)中的结构,图1(b)中的TND BPL SOI LDMOS结构在BPL SOI LDMOS结构中N漂移区顶部增加一个氧化物沟槽,同时栅极场板和漏极场板末端延长覆盖部分沟槽。为分析TND BPL SOI LDMOS结构的特性,除漂移区浓度Nd和沟槽深度ttr之外,其它主要参数固定如下:埋氧层厚度tBOX为0.2μm,漂移区厚度tSOI为20μm,BPL厚度tBPL和硼掺杂浓度分别为40μm和1×1014cm-3,沟道长度Lch为2μm,栅场板长度和漏极场板长度均为7μm,栅氧厚度为300Å,漂移区长度Ld为25μm。当沟槽长度Ltr固定为19μm时,沟槽深度ttr是所提出新结构的关键参数之一,取BPL SOI LDMOS漂移区上表面为纵向坐标原点。

2 TND BPL SOI LDMOS工作机理

与BPL SOI LDMOS结构相比,由于顶部沟槽的存在,TND BPL SOI LDMOS结构中电场积分路径由原本漏极端到源极端近乎直线的路径变为由漏极端沿着沟槽的边缘到达源极端的路径。因此,沟槽的存在客观的增长了器件在横向上电场积分路径,也即变相的增长了漂移区长度,由此可以提高横向耐压。TND BPL SOI LDMOS结构中阶梯栅极场板末端覆盖部分沟槽,其目的是将原本硅上表面场板末端的电场尖峰转移到沟槽中,沟槽内填充了具有高临界场强的低介电常数材料,使该结构在横向上可以承受更高的外加电压。

图1 截面结构示意图

3 TND BPL SOI LDMOS耐压特性分析

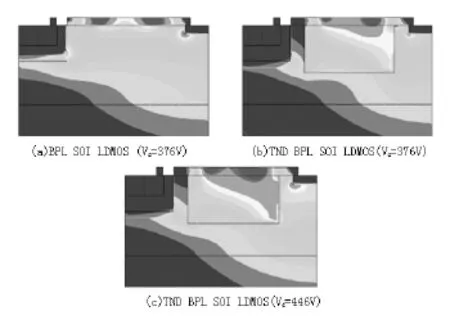

利用二维仿真软件TCAD对上述结构进行仿真,仿真过程中设置源极、栅极和衬底都接地,二维电场分布如图2所示。保持漂移区掺杂浓度不变,图2(a)为BPL SOI LDMOS达到击穿电压时的二维电场分布。由图2(a)可见,BPL SOI LDMOS结构硅膜中的电场尖峰位于栅极和漏极场板末端下方、漏极欧姆接触区左下角拐点以及P阱右下角附近。图2(b)为漏端所加电压大小等于图2(a)击穿电压时的TND BPL SOI LDMOS结构的二维电场分布。由图2(b)可见,沟槽的存在可显著降低沟槽左右两侧的电场尖峰。图2(c)为TND BPL SOI LDMOS结构达到击穿电压时的二维电场分布。由图2(c)可见TND BPL SOI LDMOS结构硅膜中的电场尖峰点位于漏极欧姆接触区左下角拐点以及沟槽右下角,栅极和漏极场板末端的电场尖峰被引入沟槽内;与图2(a)相比,可以看出图2(c)中沟槽左侧电场强度被显著减小。

图2 二维电场分布

图3 一维横向电场分布图

图3(a)为图2所描述三种情况在y=0时的一维横向表面电场分布曲线。由图3(a)可见,在表面处三种情况均有四个明显的电场尖峰,有所不同的是与BPL SOI LDMOS相比,TND BPL SOI LDMOS曲线沟槽部分的电场尖峰均显著提高,这是因为硅和氧化物之间介电常数有差别引起的,N漂移区与沟槽交界面处电场强度遵循高斯定律;图3(b)为图2中描述的三种情况在y=2时的一维横向表面电场分布曲线。由图3(b)可见,漏极欧姆接触区左下拐角处的电场强度在漂移区硅膜部分最高,该处电场强度达到临界电场时即发生击穿。与相同电压下BPL SOI LDMOS结构比较,TND BPL SOI LDMOS结构中沟槽的存在明显降低了拐角处的电场强度,只有当漏极电压增大,拐角处电场强度重新达到临界场强时,器件才又重新发生击穿。

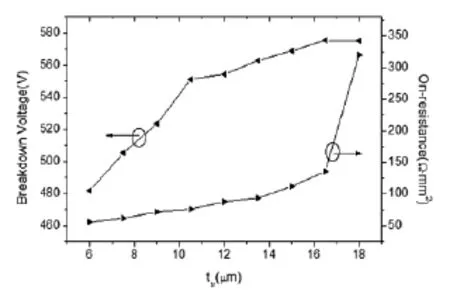

保持N漂移区掺杂浓度不变,图4为TND BPL SOI LDMOS结构中沟槽深度与击穿电压和相应通态电阻的关系曲线。由击穿电压与沟槽深度的关系曲线可见,随着沟槽深度的增大,击穿电压先快速增大然后缓慢增大,这是由于随着沟槽深度增大,沟槽对两侧电场的调制作用得到增强,到达一定程度沟槽深度继续增大,沟槽对两侧电场的调制作用逐渐达到饱和。由通态电阻与沟槽深度的关系曲线可见,随沟槽深度的增大,通态电阻先缓慢增大然后迅速增大。这是由于当器件处于导通状态时,沟槽深度越深,沟槽下表面与BPL层间的距离越小,在外加电压下,N漂移区与BPL层之间电流传导路径越易被两者形成的耗尽层所夹断,从而引起通态电阻的急剧增加。

图4 沟槽深度对器件性能的影响

图5 沟槽深度对击穿电压和通态电阻的影响

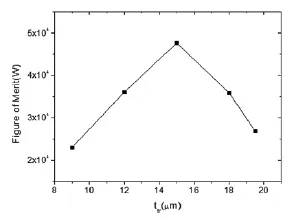

图6 沟槽深度对FOM值的影响

图5为TND BPL SOI LDMOS结构在不同沟槽深度下,改变漂移区浓度得到对应的最大击穿电压以及通态电阻与沟槽深度的关系曲线,同时图中包含BPL SOI LDMOS结构相应击穿电压和通态电阻。由图5中TND BPL SOI LDMOS结构最大击穿电压与沟槽深度的关系可见,随着沟槽深度的增大,最优击穿电压先保持较快速度增长,尔后趋于一个定值。击穿电压变化曲线的特性主要是由于当沟槽深度达到一定程度后对击穿点处电场的调制作用增量开始变得不甚明显。通态电阻先降后升是由于其大小随漂移区浓度增大和载流子输运路径变窄共同影响,由图可以看出,前期漂移区浓度的影响是主要作用,后期载流子输运路径变窄是主要作用。

在SOI横向高压功率器件的设计中,击穿电压BV和比导通电阻Ron,sp是两个关键指标,器件的性能需要在这两者之间进行折中选择,Figure of Merit(FOM=BV2/Ron,sp)优值是评价这种折中关系优劣的指标之一(沟槽结构中比导通电阻不易取得,以通态电阻代替),引入图6所示的沟槽深度与FOM值的关系曲线。从图6中可见,沟槽深度与FOM值的关系曲线先升后降,TND BPL SOI LDMOS器件在沟槽深度为15μm时FOM值最高,选取沟槽深度为15μm时的TND BPL SOI LDMOS结构与BPL SOI LDMOS结构进行比较。可以发现,虽然TND BPL SOI LDMOS结构相较BPL SOI LDMOS结构通态电阻有所增大,但击穿电压提升了83.5%,FOM值提高了68.5%。

4 结论

SOI LDMOS器件在漂移区较短的情况下,横向耐压不易提高,提出一种TND BPL SOI LDMOS来对该情况进行改善。针对漂移区较短的情况,利用沟槽深度的改变调制沟槽两侧电场强度分布,增加电场积分路径,使横向耐压获得极大的增强。当在第1小节所示基本参数下,当沟槽深度为15μm时,通过优化漂移区浓度,TND BPL SOI LDMOS可获得690V的耐压值,而BPL SOI LDMOS耐压值只有376V。前者与后者相比,虽然通态电阻略有提升,但击穿电压提升了83.5%,FOM值提高了68.5%。

[1]谢书珊,亢宝位.功率集成电路技术的发展[J].电力电子,2005(01): 4-10.

[2]D M Garner,F Udrea,H T Lim,et al.Silicon-on-insulator power integrated circuits[J].Microelectronics Journal,2001(32):517-526.

[3]张海鹏,宋安飞,杨国勇,等.漂移区减薄的多沟道薄膜SOl LIGBT的研究(I)——低压截止态泄漏电流的温度特性[J].固体电子学研究与进展,2001,21(1):37-42.

[4]张海鹏,邱晓军,胡晓萍,等.DRT MC SOl LIGBT器件漂移区新结构的可实现性[J].电子器件,2006,29(1):8-21.

[5]H P Zhang,Lifei Jiang,Lingling Sun,et a1.A novel SOI LDMOS with a Trench Gate and Field Plate and Trench Drain for RF applications[C]//Proe.Of ISCIT’2007,2007,34-39.

[6]Der Gao Lin,S L Tu,Yee Chaung See,and Pak Tam.A novel LDMOS structure with a step gate oxide[C].1995 International Electron Devices Meeting,1995:963-966.

[7]R Sunkavalli,A Tamba,and B J Baliga.Step drift doping profile for high voltage DI lateral power devices[C].Proceedings 1995 IEEE International SOI Conference,1995:139-140.

[8]Xu Shenggen,Zhang Haipeng,Fan Lingyan,et al.Forward Block Characteristic of a Novel RF SOI LDMOS with a Buried P-type Layer,2010 IEEE International SOI Conference,Oct.11-14,2010,CA,USA:88-89.

李阜骄(1990—),山东曲阜人,研究生,现就读于杭州电子科技大学。