多通道同步时钟技术

2016-12-13涂正林赵晨光

涂正林,赵晨光

(中国船舶重工集团公司第723研究所,扬州 225001)

多通道同步时钟技术

涂正林,赵晨光

(中国船舶重工集团公司第723研究所,扬州 225001)

随着阵列天线应用的发展,通讯、仪表、雷达、电子战等行业已不再满足于单通道高速模数转换器(ADC)的使用,因此多通道同步采样技术得到长足发展。基于ADI公司主流器件搭建了一个可行的多通道同步采样架构。

多通道;同步时钟;阵列采样

0 引 言

随着阵列数字信号处理技术的发展,单通道模数转换器(ADC)采样已不能满足通讯、仪表、雷达、电子战等行业需求,这促进了多通道高速ADC同步采样技术的长足发展与进步。这项技术面临的最大挑战除ADC的采样速度和接口速度匹配,还有如何控制这些先进的ADC同步采样、同步传输、同步存储以及数据重构等。本文基于TI公司高速器件搭建了一个可行的多通道同步采样架构。

1 多通道同步采样的3个关键要素

1.1 采样时钟的同步

一般阵列时钟以功分器组阵,它的优点是组阵方案简单易行,缺点是若阵面孔径较大,则体积重量会随之增大,对时钟源功率也要求较高。如果ADC采用压控振荡器(VCO)+锁相环(PLL)的独立时钟,比如ADI公司的LMX2531、LMX2582等器件,优点是体积小,重量轻,时钟杂散和相噪控制较好;缺点则是每个采样板之间时钟相对独立,不能同步[1]。各AD板时钟之间相位差是随机的,最坏的情况是,某2个子阵时钟相差π,此时2个时钟延时达到最大值。对于1GHz采样时钟,时间延时:

根据存在误差时阵列天线方向图公式:

(1)

由上式可以推导出以下几种情况[3]:

当存在幅相误差时,阵列天线增益损失:

(2)

当各阵元幅度加权相等时,波束指向误差方差:

(3)

当存在相位误差时,波束平均旁瓣电平:

(4)

从公式(2)可知,当阵元数N较大时,阵列天线增益损耗只与相位误差成正比;从公式(3)可知,波束指向误差正比于相位误差,但与阵元数成反比;从公式(4)可知,旁瓣电平随相位误差的增大而抬高。

从以上计算可以看到,在中频频率更高的场合,即使时钟间延时非常微小,相位差都会导致后端很大的通道间相位采样误差,而相位误差增大会导致数字波束增益下降,旁瓣恶化,主波束指向偏离。

1.2 系统参考信号的同步

在各通道时钟同步的前提下,系统同步参考信号在多通道同步采样系统中十分重要,它也是周期信号,用于ADC内部多帧时钟的前沿对准。系统同步参考信号不仅让多通道同步采样系统进行时钟前沿同步,同时也实现了整个ADC系统的同步数据传输。如果阵列存储系统没有收到同步参考信号,各个通道采集的数据将被认为无效而忽略。因此,同步参考信号将对系统阵列数据采集、同步传输和存储起着关键作用。外部系统参考信号用于对齐所有的内部时钟相位和本地多帧时钟到一个特定的采样时钟边缘,允许在一个系统中的多个设备同步,并最大限度地减少时间和定位的不确定性。

1.3 数据传输的同步

高速ADC器件都有SYNC*输入引脚,它是ADC的一个对外接口,用于数据传输同步,它的时序产生也是依赖采样时钟和SYSREF,由现场可编程门阵列(FPGA)统一触发产生。有了这个同步输入引脚,使大规模ADC组阵成为可能。

2 多通道时钟和控制设计与分析

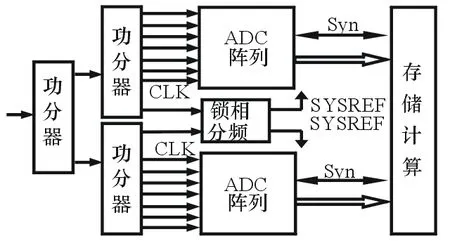

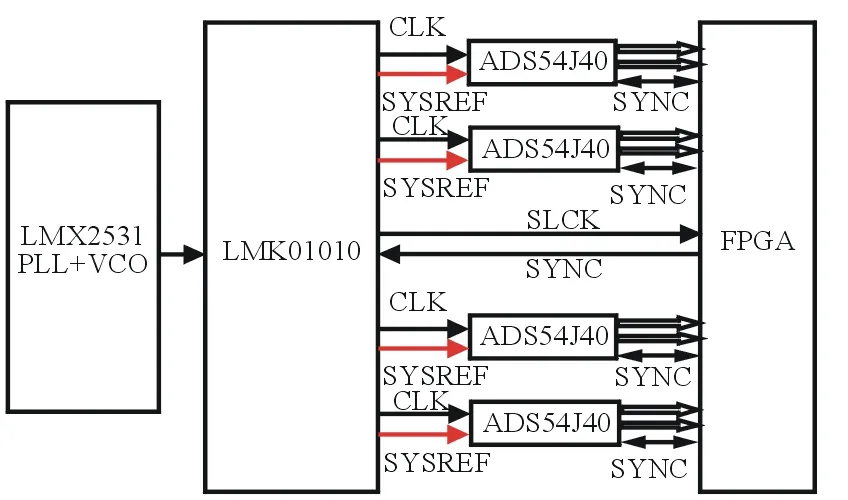

早期时钟同步使用功分器和射频电缆,通过调整射频电缆长度保证各通道时钟同步,再以SYSREF进行采样时钟前沿对齐。其基本框图见图1。

图1 早期多通道同步采样

但这种方法只适用于通道较少的情况,而且时钟源功率要求较大,同步精度不高,调试需要矢量分析网络、高精度等相电缆,调试维护工作量较大,遇到差分时钟要求的ADC器件,还需使用类似ADT1-1WT等射频变压器转换。由于射频变压器的个体差异,各通道原本同步的时钟会再次失配。 随着电子器件工作频段的不断提高,当前相当数量的高速ADC时钟都可以由集成电路直接提供,并且现在高速ADC支持多种类型的时钟信号,包括LVDS时钟信号。本文选用TI公司推出的LMX2581锁相时钟源、高速ADC芯片ADS54J40和多通道时钟分配器LMK01010搭建了1个多通道同步采样系统框架。

LMK01010是TI公司LMK01000系列高速时钟分配芯片,它具有以下优点:

(1) 8路独立可编程LVDS时钟,支持0~1 600 MHz;

(2) 全局时钟输出同步,支持多片时钟同步;

(3) 30 fs时钟抖动@20 MHz;

(4) 芯片内任一时钟输出都可以独立完成延时、移相、分频等操作;

(5) 最多可同时为8个高速ADC提供等频率(分频)同步高速时钟。

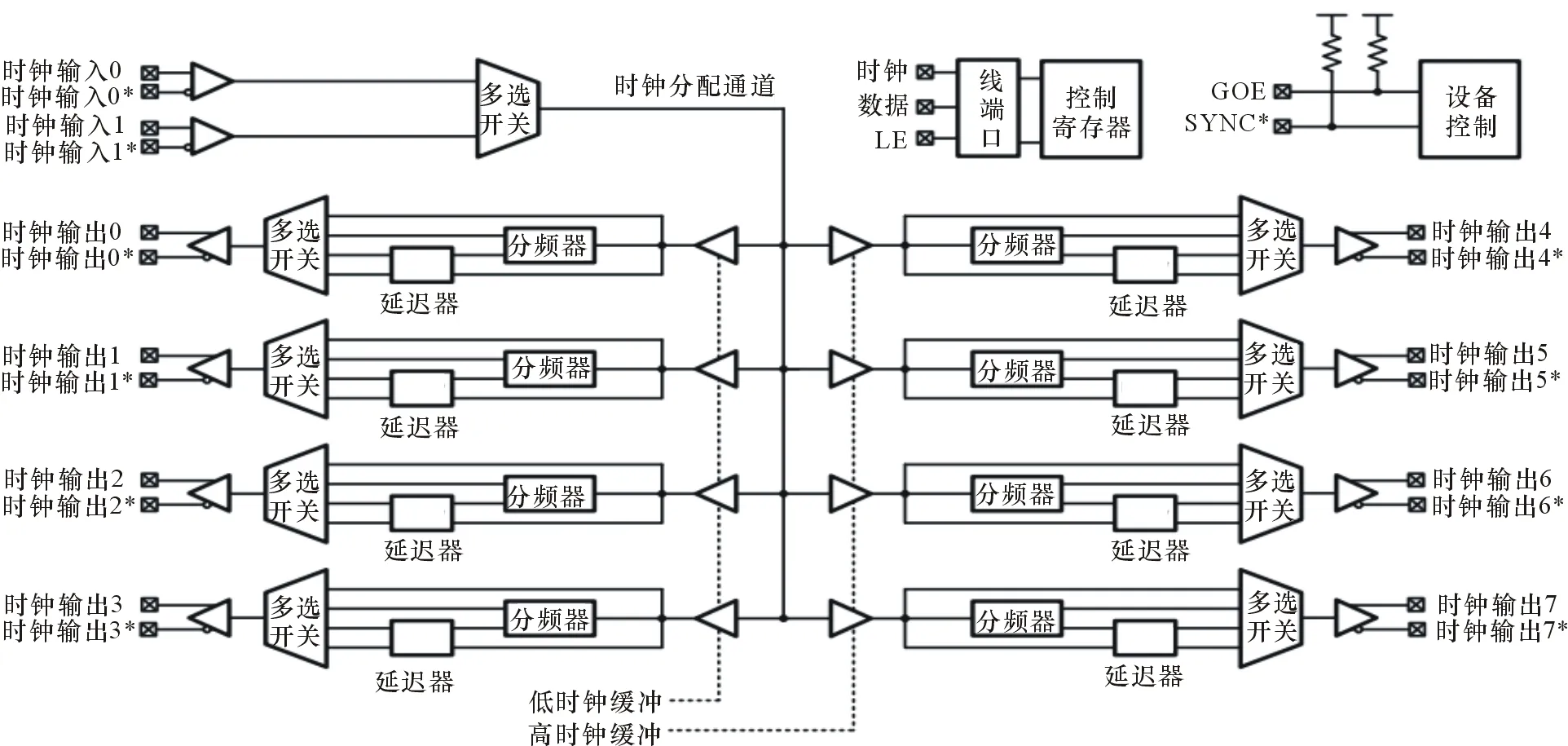

其基本框图如图2所示。

图3是以单片LMK01010为核心的多通道ADC同步采样系统,其中LMX2531作为LMK01010唯一的驱动,为整个同步采样系统提供统一的时钟源;ADS54J40采样率1 GSPS并支持LVDS时钟。FPGA为AD54J40经过直接数字控制器(DDC)后的采样数据分配传递给后端的信号存储分析系统。

图2 LMK01010框架简图

图3 单片LMK01010为核心的多通道采样系统

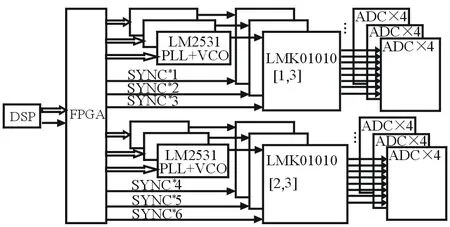

然而在某些场合,几路ADC同步采样并不能满足对数量庞大的传感器系统采样分析的需求。因此,对于大规模通道传感器场合,可以充分利用LMK01010芯片中SYNC*全局时钟控制信号实现多片时钟分配芯片的组合,驱动更大数量的ADC进行同步采样。

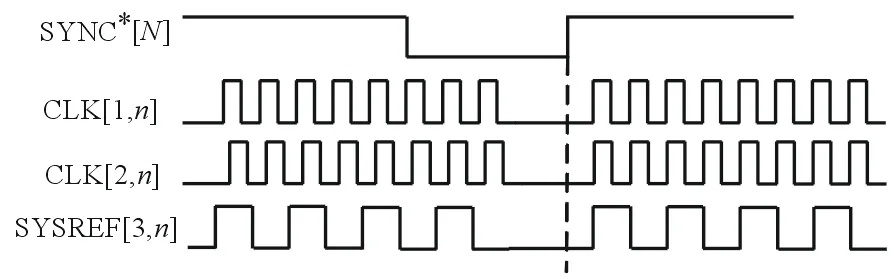

图4中每一个LMK01010都有一个独立的时钟源,它们分配时钟的同步控制都由高精度前沿正对的SYNC*[N]来实现。同步时序如图5所示。

图4 多片LMK01010架构的多通道同步采样系统

图5 多片时钟分配同步时序

图5中,SYNC*[N]抽取任意一路时钟同步信号,CLK[1,n]为第1片LMK01010芯片的第n路时钟输出(n=1,3,5,7;n=2,4,6,8分频后作为SYSREF使用);CLK[2,n]为第2片LMK01010芯片的第n路时钟输出;SYSREF[3,n]为第3片LMK01010芯片的系统参考信号。这样选取时钟逻辑进行测量比较,能客观反映多片LMK01010芯片系统中由SYNC*控制的同步情况。

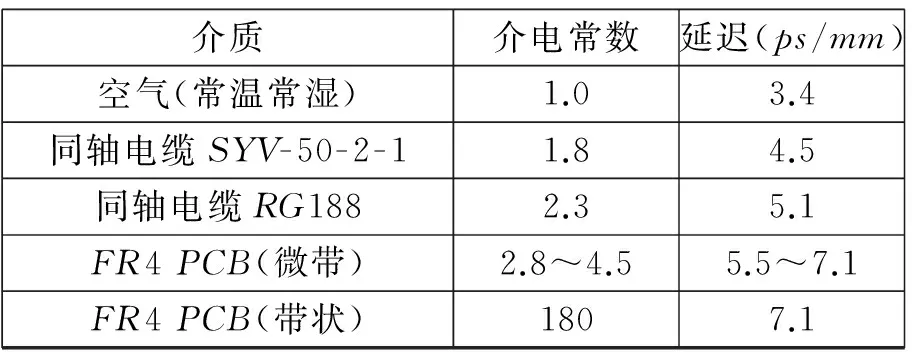

相对于高频的时钟信号,频率低得多的视频信号SYNC*[N]更容易实现前沿正对。但随着ADC阵列板的数量不断增加,SYNC*[N]控制线的长度差也会越来越大,这个长度差对SYNC*延时影响根据传输线介电常数ε的不同而不同,如表1所示。

选取介电常数2.3进行计算,信号传输延时的计算公式为:

(5)

假设最长传输线与最短传输线的长度差为1.5 m,那么它们之间SYNC*传输时间差为7.58 ns。这样的时间差是无法让板间LMK01010的时钟同步的,SYNC*信号在传输线中的延迟补偿设计也必须重点设计。根据上述计算,知道在一个强调高度同步的采样系统中,首先选择好同步信号传输线,保证其电长度误差在设计范围;如果实际长度之间存在误差,还可以根据时钟前沿实际测量结果,通过LMK01010的时钟延迟通道或者移相,对时钟同步进行微调。

表1 介电常数延迟对照表

LMK01010不仅可以在单板中为ADC及其外部接口提供高精度的同步时钟,还可以应用于ADC的组阵。在设计指标允许范围内,通过SYNC*管脚将LMK01010组阵,再通过其8路时钟输出将ADC同步组阵,以满足大阵面场合的应用需求。只要对SYNC*前沿进行精心设计,并辅以芯片内部移相和延迟功能,ADC阵面可以进一步扩展。以LMK01010为核心的时钟设计方案具有体积小、重量轻、功耗低、工作频带宽、设计一致性好、扩展能力强、生产调试方便、阵元微调能力突出等优点。

3 结束语

多通道同步采样时钟是系统同步的先决条件,设计方案不同,选取器件不同,设计方法也有不同。现在各大公司厂家根据设计师要求提供了各种不同的时钟分配芯片,方便电子设计师的设计和调试,同时也为多通道采样系统的小型化、实用化提供了技术支持。类似系统可以广泛应用于多输入多输出系统、电磁环境采集与检测、雷达电子战、阵列声纳等领域。

[1] 孙进才,朱维杰.信号相位匹配原理及其应用[M].西安:西北工业大学出版社,2007.

[2] 毕增军,徐晨曦,张贤志.相控阵雷达资源管理技术[M].北京:国防工业出版社,2016.

[3] MAILLOUX R J.Phased Array Antenna Handbook[M].Boston,America:Artech House,1993.

Multi-channelSynchronousClockTechnology

TUZheng-lin,ZHAOChen-guang

(The723InstiuteofCSIC,Yangzhou225001,China)

Withdevelopmentoftheapplicationofarrayantenna,communication,instrumentation,radar,electronicwarfareandotherindustriesarenolongersatisfiedwiththeuseofsinglechannelhigh-speedanalogtodigitalconverter(ADC),somulti-channelsynchronoussamplingtechnologyhasbeengreatlydeveloped.Thispaperconstructsaviablemulti-channelsynchronoussamplingarchitecturebasedonthemainstreamdevicesofADICo..

multi-channel;synchronousclock;arraysampling

2016-06-11

TN

A

CN32-1413(2016)05-0094-04

10.16426/j.cnki.jcdzdk.2016.05.024