基于DSPC6678多核平台的实时任务调度架构设计分析

2016-12-13任志明

任志明

(中国船舶重工集团公司第723研究所,扬州 225001)

基于DSPC6678多核平台的实时任务调度架构设计分析

任志明

(中国船舶重工集团公司第723研究所,扬州 225001)

分析了数字信号处理器(DSP)C6678的多核模式,设计了一种基于C6678高速多核DSP硬件平台的实时任务调度软件架构,实现了实时任务调度。通过实际测试,整体设计满足了设计指标。

实时任务调度;多核数字信号处理器;软件架构

0 引 言

在当前舰载设备的控制系统中,任务调度模块需要从外部接收大量导航数据、目标更新参数,并实时进行坐标转换计算,输出控制。单核主机已经难以满足既能快速处理大量网络输入输出,又能实现稳定的脉冲级的实时控制,因此需要选用合适的多核硬件平台,并研究相应的系统控制软件架构。

1 系统分析

舰载设备任务是以正北坐标设置的,任务最后的执行必须是以设备坐标进行控制,整个流程有大量的坐标转换计算,需要较高的浮点计算能力。实时任务调度运行的模式是以指定的周期运行,通过调度算法输出每个周期需要执行的动作序列,然后依次执行每个控制[1]。在大网络数据流量的输入下,需要能够稳定地输出调度结果,实时地执行调度结果,因此需要从物理上将网络输入和调度、执行隔离,避免影响调度、执行的实时性。

按照对时间的响应要求划分,整个处理流程可以分为3类:非实时性的,实时性的,强实时性的。如果从硬件上将3个层次的处理完全隔离,就可以保证在系统高数据流量输入的情况下,不影响调度输出的稳定性和执行的强实时性。系统功能分级示意图如图1所示。

图1 软件模块分级示意图

所以,系统的硬件平台需要支持多核、高速度计算性能,同时需要设计匹配多核的软件架构,实现稳定的实时控制输出。TI公司的C6678是一款高速多核DSP芯片,有8个核,而且TI也提供了配套的多核软件开发包[2]。

设计目标是从网络接收100次/s的导航数据,500次/s目标更新的情况下,调度模块实现小于1ms精度的控制输出,在执行模块实现精度为2μs的实时控制。

2 硬件平台分析

C6678是TI公司的多核高速数字信号处理器,支持高速定点和浮点计算,每个核的主频高达1GHz,它是为了满足高速的计算性能和低功耗的要求,以多核实现系统的性能提升,同时保持低功耗。每个核可以运行独立的操作系统,有独立的L2SRAM,可以通过GPIO响应外部硬件中断,通过EMIF和SRIO与外部设备进行高速通信[3]。核之间通过消息队列和共享内存进行同步、数据共享。

C6678计算能力强,多核并行同时处理,为软件设计提供了强大的硬件平台,为软件的架构提供了极大的灵活性,但是软件设计难度较大,测试比较麻烦。

TI为C6678提供了实时操作系统Sys/Bios,具备操作系统的任务调度、中断管理、同步模块、定时器服务、内存管理、硬件抽象层管理、输入输出管理等主要功能,而且提供了集成开发调试工具CCS,能够在开发过程中查看任务和各个对象的状态[2]。和多核计算相关的软件组件主要包括IPC、MCSDK、NDK、PDK和OpenMP。

IPC提供了处理器多核管理组件、共享区域管理组件、消息队列管理组件、内存堆管理组件,如果使用多核必须使用IPC提供的组件进行配置和调度[3]。MCSDK提供了芯片支持库、驱动、平台配置工具、核间通信模块[2]。NDK是TI公司的网络通信组件模块,实现了TCP/IP协议[2]。PDK是TI公司提供的平台配置开发包,实现了CSL库和硬件驱动程序、平台库。OpenMP是TI对实现并行计算的软件支持包。

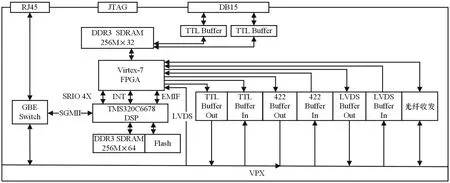

设计实时任务调度的硬件平台框图如图2所示。

图2 硬件平台框图

3 多核模式分析

C6678多核的使用模式主要有3类:主从模式、数据流模式、OpenMP模式[2]。

3.1 主从模式

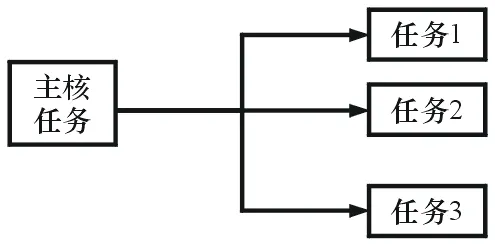

主从模式中有一个核作为主控,其他核只负责执行分配的任务,集中控制分布执行。主核负责调度分配任务,将数据分发给从核,主核使用高级操作系统linux运行复杂的逻辑控制、任务监控。此种模式适用于有很多小的独立任务的应用,每个任务可以独立在单核上运行,任务之间不需要进行交互、同步、数据共享。对于电信协议的多路解析,每一链路对应一个独立的任务,可以同时将多个任务分布到多个核上,各自独立运行。主从模式示意图如图3所示。

图3 主从模式示意图

主核负责管理空闲资源以均衡运行,不至于有过载或过闲的核。任务分配通过消息队列传输,从核一直有一个独立的任务处于等待接收消息的状态,在消息没有到来之前处于挂起状态。

此种模式的难点在于如何实时均衡地分配任务和监控执行状态,因为每个核运行的任务不同,而且执行顺序是随机的,任务的需求吞吐可能相差很大,所以需要不断地进行任务的动态分配与资源调整。

3.2 数据流模式

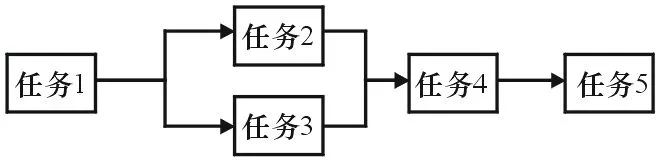

数据流模式代表的是一种分段流水式的控制和执行,每个核负责处理过程的一个步骤,然后将处理结果传递到下一个核进行后续处理,各个核相互协同,共同完成整个处理过程。一般的会有一个核负责从外部接收输入的指令或者数据,可以从网络或者现场可编程门阵列(FPGA)接收外部输入,整个处理流程是数据流驱动的。一个核处理的输出是另外一个核的输入,适用于大型、复杂、相互依赖、不适合单核进行处理的任务,或者是需要实现高速外部输入的情况下、能够实时稳定输出控制的应用,每个核各自独立地运行实时操作系统。

此种模式的难点在于如何将一个复杂的任务分解到多个核上,形成一个处理的流水,同时设计核之间高速的数据通信模式,保证数据流输出的稳定性,形成数据处理流水线。数据流模式示意图如图4所示。

图4 数据流模式示意图

3.3 OpenMP模式

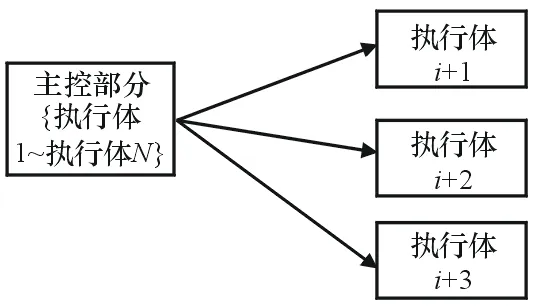

OpenMP模式是一套在对称多处理(SMP)模式下开发多任务应用的接口,由编译指令、库以及环境变量构成。一般是在主程序中通过编译指令,指定需要运行时用的核和执行体,执行时展开到各个核上并行运行。

这种模式和主从模式有点类似,但是使用比主从模式简单,只需要通过编译指令就可以实现,不需要对任务进行动态的监控调整。每个核上运行的代码可以是相同的,也可以是不同的。OpenMP模式示意图如图5所示。

每个核执行相同代码的OpenMP示例:

omp_set_num_thread(4);

#pragmaompparallel

{

ProcessData();

}

每个核执行不同代码的OpenMP示例:

#pragmaompparallel

#pragmaompsections

{

#pragmaompsection

Process1();

#pragmaompsection

Process2();

}

图5 OpenMP模式示意图

此种模式一般用于计算量较大、数据能够分段并行处理的场合,典型的应用有图像数据处理、雷达快速傅里叶变换(FFT)计算等。

4 软件架构

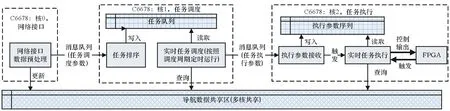

软件架构必须匹配于应用模型,相应地也分为3个部分:非实时部分、实时部分、强实时部分,分别对应于接口、调度和执行,3个部分分别运行于3个核上,相互独立,通过消息队列和直接共享内存传递、控制数据。软件架构图如图6所示。

多核模式中的数据流模式比较符合此种应用场景,因此选用了多核模式中的数据流模式作为实时任务调度的控制模式。

通过物理隔离,将不同时间响应要求的功能模块分布到不同的核上,避免了大流量的网络输入对调度和执行的影响。

图6 软件架构图

在核0上接收到导航数据后,写入共享内存,核1与核2在需要时,直接访问共享内存。在核1上,实时任务调度从核内的任务队列空间读取需要调度的任务,输出每个调度周期的执行波位序列。在核2上接收到执行参数后,触发实时任务执行,从执行波位序列中读取执行参数,实时任务执行通知FPGA控制外部,当第1个结束后,FPGA触发实时任务执行继续读取第2个,直到执行序列全部处理结束。图6中核2的框图内部使用粗实线表示与FPGA的硬中断实时交互控制。

5 应用设计

基于以上的分析,设计了实时任务调度系统。应用分为3个部分,每个部分为一个独立的工程,分布在C6678的3个核上(核0、核1和核2)。

在核0上进行接口和数据预处理,处理非实时数据,连接非实时的对外接口;在核1上运行调度模块,以小于1ms的误差输出调度的执行序列;在核2上运行强实时执行模块,将一个调度周期的执行序列在FPGA的实时中断驱动下,以微秒级别的控制精度输出。

6 测试验证

给系统输入导航数据,模拟目标更新数据,然后启动一个控制任务,经过实时任务调度输出调度结果,每个调度结果代表一组连续执行的脉冲,测量其运行参数,进行验证测试。

6.1 测试方法

通过网络以100次/s的速度发送导航数据,按照500次/s的速度发送更新参数,然后启动运行1个控制任务,工作参数是1组16个脉冲,每个脉冲的执行时间长度为1 000μs。通过计算相邻的调度结果输出的时间间隔,可以评估调度输出的稳定性;通过计算1组脉冲连续输出的时间间隔,可以评估脉冲的控制精度。在调度输出的节点和任务执行的节点录取时间戳信息,然后通过网络输出,在外部进行录取和统计分析,最后进行整体控制精度评估。

调度结果的输出间隔应该是10ms的整数倍,脉冲执行输出的时间间隔应该是1 000μs,调度间隔与10ms整数倍的偏差小于1ms,脉冲执行的偏差小于2μs。

6.2 测试结果统计

在设计中,在DSP和FPGA之间采用了数据流水线设计,在1组脉冲中,第1个脉冲执行间隔实际是参数的计算时间,并不是执行间隔,最后一个脉冲的时间间隔是下一个调度周期的脉冲的时间间隔,所以在数据处理的过程中需要去掉第一个脉冲间隔和最后一个脉冲间隔。

从录取的输出参数中总共提取了1 936 987组脉冲执行参数、269 200组调度间隔参数。脉冲执行参数偏差超过1μs的有22个,最大偏差1.159μs,其余的偏差均小于1μs。从录取中共提取了269 200组数据,统计出调度的最大偏差为89.7μs,小于0.1ms。

7 结束语

本文通过分析舰载控制系统实时任务调度的过程,采用高速多核DSP平台,通过分层设计将不同时间响应要求的逻辑处理进行物理隔离,设计了实时任务调度的多核软件架构。从实际的测试数据可以看出,在高速网络数据流输入的情况下,调度结果的输出是稳定的,调度结果的执行是实时的,实际的偏差在设计范围内,实现了实时任务调度和实时任务执行。

[1] 胡卫东,郁文贤,卢建斌,王壮.相控阵雷达资源管理的理论与方法[M].北京:国防工业出版社,2010.

[2] 董言治,娄树理,刘松涛.TMS320C6000系列DSP系统结构原理与应用教程[M].北京:清华大学出版社,2014.

[3] 牛金海.TIC66X多核软件开发技术[M].上海:上海交通大学出版社,2015.

DesignandAnalysisofReal-timeTaskSchedulingArchitectureBasedonDSPC6678Multi-corePlatform

RENZhi-ming

(The723InstituteofCSIC,Yangzhou225001,China)

Thispaperanalyzesthemulti-coremodeofdigitalsignalprocessor(DSP)C6678,designsareal-timetaskschedulingsoftwarearchitecturebasedonC6678high-speedmulti-coreDSPhardwareplatform,implementsreal-timetaskscheduling.Thetotaldesignissatisfiedforthedesignindexesthroughactualtest.

real-timetaskscheduling;multi-coredigitalsignalprocessor;softwarearchitecture

2015-05-03

TN

A

CN32-1413(2016)05-0090-04

10.16426/j.cnki.jcdzdk.2016.05.023