基于FPGA的多路E1传输高速RS422业务方案

2016-12-05白杨韦以超

白杨,韦以超

(中国电子科技集团公司 第三十四研究所,广西 桂林,541004)

基于FPGA的多路E1传输高速RS422业务方案

白杨,韦以超

(中国电子科技集团公司 第三十四研究所,广西 桂林,541004)

提出了一种高速RS422业务通过多路E1进行传输的设计和实现方案,该方案能够将标称速率为8704kb/s的同步RS422业务映射为5路E1,同时在接收端正确恢复业务数据,实现业务传输,并利用FPG A实现了该传输方案。

SD H;E1;映射;解映射

0 引言

SDH协议采用时分复用技术将多个低速数据业务复用到一个高速数据通道中进行传输,我国采用的SDH复用映射结构包括C-12(2Mb/s)、C-3(34Mb/s)和C-4(140Mb/s),对应的SDH设备一般提供丰富的E1和以太网接口,但在实际应用中,存在8M、10M等串行业务需求,无法直接通过SDH设备进行传输[1]。本文针对标称速率为8074kb/s的高速同步RS422业务的传输需求,提出了5路E1业务进行传输的反向复用技术设计方案,此方案可以在已有SDH设备基础上实现业务传输。

1 系统方案

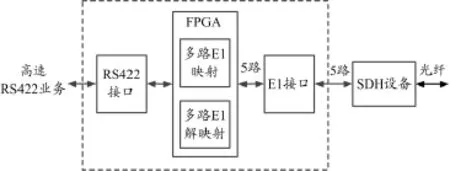

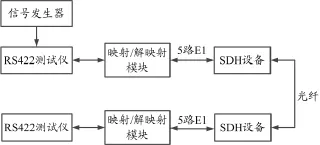

图1为系统方案的原理框图。上行方向(多路E1映射)FPGA通过RS422接口电路接收同步RS422业务,并将其映射成5路E1信号,通过现有SDH设备的E1业务接口传输至对端。下行方向(多路E1解映射),接收由SDH设备输出的5路E1数据,并由FPGA将其映射为1路RS422串行数据,同时根据数据速率恢复出接收时钟,输出至RS422端口。此设计方案的核心在于映射/解映射协议的设计和实现,需要考虑的关键问题有以下三点。

图1 系统方案框图

①RS422业务速率变化。RS422业务标称速率为8074kb/s,但由于时钟频率偏差等原因,其实际速率会出现波动,需要通过映射协议的设计将其频率偏差吸收进E1数据中。

②E1传输延时。SDH复用、交叉或传输路径等原因会带来各E1线路传输延时不同,解映射时如需充分考虑这些延时,可在设计方法上容忍一定时间的延时[2]。

③误码恢复。5路E1中传输的是同一个RS422业务,因此,任意一路E1的误码、中断等都会造成RS422业务的相应故障,但该故障必须是可恢复的,即当E1故障恢复时,RS422业务也应尽快恢复。

2 主要功能设计方案

2.1映射功能设计

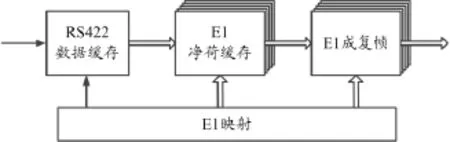

图2为上行方向(E1映射)的功能设计框图,以下对主要设计思路和功能模块进行说明。

①E1单帧结构定义。根据业务速率,我们提出了满足传输要求的E1单帧结构。标准E1单帧的周期为125μs,即每个比特位的传输带宽为8kb/s,RS422业务速率的标称值为8072kb/s,由此可以计算出平均每路E1的每帧中的有效净荷比特数量为 8072÷8÷5= 201.8。根据上述结果,在映射协议中,设计有两种速率帧:正调整帧和负调整帧。其中,正调整帧中每帧的净荷数量为 201bit,负调整帧中每帧的净荷数量为202bit,因此5路E1实际传输带宽为8040~8080kb/s。E1单帧有32个时隙 (TS0~TS31),其中30个时隙(240bit)可以用于传输业务数据,除去上述净荷数量外,剩余有足够的开销通道。为了使映射协议具有良好的可扩展性,我们在E1单帧结构定义中设计了2个字节作为开销数据,剩余的12bit可作为预留带宽。

图2 E1映射功能设计框图

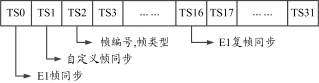

图3所示为E1帧结构的定义,其中TS0和TS1是标准E1开销时隙,TS1用于自定义帧同步字节,TS2的bit7~bit4定义为帧编号,bit3~bit0用于标识帧类型,TS3~TS29(不包括TS16)和TS30的bit7~bit6作为数据净荷,TS30的bit5~bit0和TS31保留。

图3 E1单帧结构定义

②RS422数据缓存和E1净荷缓存。RS422数据缓存用于存储来自业务端口RS422数据,采用1bit位宽的FIFO作为数据缓存,在业务端口时钟域下写入,并在E1映射/开销插入模块的控制下,将数据读出,并依次写入5个E1净荷缓存中。5个E1净荷缓存分别用于存储5路E1的净荷数据,同样采用1bit位宽的FIFO存储器,从RS422数据缓存中读出的数据流将轮流存入上述5个缓存。

③E1映射。E1映射的主要功能是通过对缓存的读写控制及E1开销字节插入,产生符合上述结构定义的E1帧。

自定义帧同步(TS1)采用每帧正向递增1的心跳字节。帧编号为0~15,且同时发送的5路E1具有相同的帧编号,即相同编号的5路E1帧数据净荷拼接可得到原RS422串行数据流。帧类型包括正调整帧和负调整帧两种,正负调整的判决来自每个E1净荷缓存FIFO的almost_empty和almost_full状态指示。

E1映射模块根据上述功能产生缓存的读/写控制时序,从而形成E1单帧的净荷数据部分,同时产生E1单帧开销数据和TS0、TS16。

④E1复帧。E1复帧主要功能是将自定义的每路E1单帧组成符合标准协议的E1复帧结构,从而能够正确接入SDH设备[3]。E1复帧成帧功能可参考具体标准协议,不作为本文重点论述内容。

2.2解映射功能设计

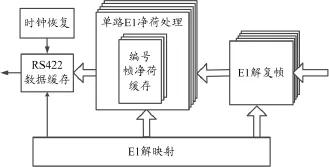

图4为E1解映射的功能设计框图,其中主要功能是从接收的5路E1中提取数据净荷,拼接出原RS422数据流,并输出至业务端口,下面对各主要功能模块进行介绍。

①E1解复帧。E1解复帧是映射过程中E1成复帧的逆处理,其主要功能是完成标准的E1复帧同步,并从中提取出E1单帧。

②E1解映射。E1解映射主要功能是实现5路E1数据净荷的提取和拼接,是实现业务传输的核心功能,它需要解决的关键问题是定位5路E1单帧中具有相同帧编号的单帧,但是由于前述延时问题的存在,每路E1中编号相同的单帧接收时间无确定关系。

图4 E1解映射功能设计框图

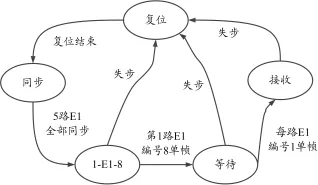

图5所示为解映射功能顶层的控制状态机,该控制状态机的功能是保证各路E1之间延时在2ms内的准确同步。复位状态先对各功能模块和缓存进行复位,复位结束后,进入同步状态;每路E1单独进行同步,采用E1复帧同步和单帧心跳字节同步的双重同步机制,确保帧数据正确;当5路E1全部同步后,进入1-E1-8状态,该状态中第1路E1开始搜索编号为8的单帧;搜索成功后,进入“等待”状态,该状态中5路E1分别等待各自编号为1的单帧;接收到编号为1的单帧后,进入“接收”状态,向E1帧编号净荷缓存中写入数据。

③数据缓存。解映射方向同样采用两级缓存,第一级缓存为E1单帧净荷缓存,第二级缓存为RS422数据缓存。与映射不同的是,为了减小线路误码对RS422数据恢复的影响,每路E1净荷均按照帧编号进行缓存,不同编号的单帧使用独立的数据缓存,即每路E1设置有16个帧编号净荷缓存,同样采用位宽为1bit的FIFO。

在解映射产生的控制时序下,5路E1单帧的净荷分别按照帧编号写入对应的缓存中,同时,从相同帧编号的缓存中依次读取数据,当相同帧编号数据全部读取完毕后,再对下一个编号帧进行相同操作,依次类推,将5路E1中的数据净荷恢复成原RS422的数据流,并写入RS422缓存中。

④时钟恢复。时钟恢复模块产生RS422业务的发送时钟[4],其标称值为8704kHz,并且根据RS422缓存中的almost_full和almost_empty状态,对时钟频率进行调整,使其最终跟踪发送端的时钟频率。

图5 解映射控制状态机

3 测试结果

图6为硬件测试平台示意图,其中RS422测试仪设置为外时钟工作,通过信号发生器为其提供频率可调节的工作时钟,SDH设备为通用的SDH设备,且具备至少5个E1接口。经过长时间拷机测试,同步RS422业务在8704±1kb/s无误码,满足设计要求。对信号发生器时钟频率在8740~8780kHz范围内进行抽样测试,每次测试48小时均无误码,测试结果与设计原理符合。

图6 测试平台

4 结束语

本文提出了一种高速RS422业务到多路E1的反复用设计方案,并详细介绍了映射协议的E1单帧结构及其实现原理。测试结果与设计相符合。本方案原理可应用于其它高速业务到多路E1的映射处理,在后续设计时可对解映射的数据缓存结构和业务时钟恢复进行进一步优化。

[1]陈朝枢.SDH的映射和同步复用原理[J].数字通信,1995(3):56-57.

[2]陈立胜.多路E1传输以太网的应用及其实现[J].通信技术,2002,4(9):97-98.

[3]李鹏程,颜永红,帅金晓,等.E1成/解帧器设计[J].微计算机信息(嵌入式与SOC),2009(23):225-227.

[4]李鑫,黄海生,张斌,等.一种E1时钟数据恢复电路的设计[J].西安邮电学院学报,2012,17(3):67-70.

High speed RS422 transmission scheme over E1 based FPGA

BAI Yang,WEI Yi-chao

(The 34th Research Institute of CETC,Guilin Guangxi 541004,China)

A High Speed RS422 transmission scheme over E1 is proposed in the paper.In the presented scheme,synchronous RS422 which nominal speed is 8704kb/s can be transmitted over 5 channels E1,and the business recovery is implemented in the receiver.And the scheme is implemented by FPGA.

SDH,E1,mapping,demapping

TN248

A

1002-5561(2016)05-0022-03

10.13921/j.cnki.issn1002-5561.2016.05.007

2016-01-28。

白杨(1982-),男,硕士,工程师,从事光通信相关FPGA的设计开发工作。