一种LTE-A帧定时同步算法的AISC设计与实现*

2016-12-03代文强李贵勇

代文强,李贵勇

(重庆邮电大学,重庆400065)

一种LTE-A帧定时同步算法的AISC设计与实现*

代文强,李贵勇

(重庆邮电大学,重庆400065)

研究了一种TD-LTE-Advanced系统中基于同步信号的帧定时同步算法,对该算法进行仿真和分析,并提出算法实现方案。然后,根据精度、面积、功耗、可扩展性等需求,确定了ASIC实现策略以及实现方案,并对帧同步和FFT模块进行了ASIC的详细设计实现。最后经过仿真、验证和逻辑综合,得出ASIC设计能够达到预期功能目标。该方案在功耗和面积上有一定的优势,本文ASIC设计的面积比同类模块小8.8%,功耗低9.3%。

LTE-A;帧同步;定时同步;ASIC

0 引言

当前 LTE-Advanced系统架构趋于扁平化,以往的帧定时同步方案已不再适合 LTE-Advanced系统,因此,需要寻找一种新的帧定时同步实现方案。本文将该算法分成3个步骤:粗定时同步和小区组内ID号检测、精定时同步、帧同步和小区组ID号检测。由于定时同步需进行FFT运算以及相关运算,这样划分能够利用粗定时同步迅速地找到PSS的大致位置,缩小精定时同步的检测范围,很大程度上减少了精定时同步的计算量,并且加快帧定时同步过程的完成。

本文通过ASIC设计方案与传统的FPGA处理相比,得出ASIC设计更适合于对实时性和可靠性要求高的大规模复杂的信号处理系统,并且在面积和功耗上也有很大优势,可保证良好地适用于LTE_A用户终端。

1 相关算法研究

1.1 粗定时同步和小区组内ID号检测

粗定时同步是为了迅速地找到主同步信号(Primary Synchronization Signal,PSS)的大致位置并获得小区组内标识(Identity,ID)号,以便确定 PSS的滑动范围,因此从减少计算量、方便实现等因素考虑,决定采用基于接收 PSS对称性相关的粗定时同步方案[1]。

PSS在时频域均具有对称性,能够在接收端利用该特性检测PSS。该方案的具体步骤是:接收半帧的数据(假设这半帧的数据中含有一个完整的 PSS),以第 1个数据点为起点,依次取出长度为2 048的数据,用r(n)表示,并将 r(n)分成两个部分。对这两部分数据做滑动相关运算,运算结果的最大值所在位置就是PSS的大致位置,如式(1)所示[2]:

其中,N表示相关窗长度,即半个OFDM符号长度,当降采样率设成1/16时,N取64。获得的PSS大致位置为:

对该粗定时同步方案进行 Matlab仿真,设置的仿真条件为:高斯白噪声信道,信噪比为-10 dB,普通CP,定时偏移设为0,频偏设为2 000 Hz,发送信号中PSS采用的为1。仿真图如图1所示。

图1 PSS前后部分对此相关的粗同步仿真图

从上图可看出,最大值的横坐标是2 333,通过换算得到在接收数据中的位置是35 280。PSS的实际位置为35 265,仿真结果与它差了15个点。由于进行了降采样处理,采样率为 1/16,15个点的误差可以接受。

该方案在找到PSS的大致位置后,最大值所在的组所对应的即为接收PSS的根指数,通过u与的一一对应关系[2],可以得到的值。

1.2 精定时同步

为满足同步精度要求,需要在粗定时同步的基础上进行精定时同步来缩小查找范围。本文采用基于接收PSS与本地PSS相关的算法[3]进行精定时同步。首先,由粗定时同步得到的在本地生成频域 PSS,再通过快速傅里叶反变换运算 (Inverse Fast Fourier Transform,IFFT)变换到时域上。然后在d的左右各64个点范围内,即[d×16-64,d×16+63],直接与降采样前的时域接收数据进行滑动相关,最大值所在的位置即精定时同步的位置。相关函数由下式所示[3]:

由式(4)算出最大值所在的位置即精同步的位置:

对精定时同步进行Matlab仿真,设置的仿真条件为:高斯白噪声信道,信噪比为-10 dB,普通 CP,定时偏移设为 0,频偏设为 2 000 Hz,发送信号中 PSS采用的为1。仿真图如图2所示。

图2 PSS前后部分对此相关的粗同步仿真图

从上图可看出,最大值的横坐标是63,与实际的位置相符。

1.3 帧同步和小区组ID号检测

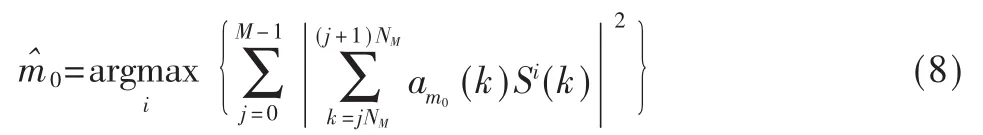

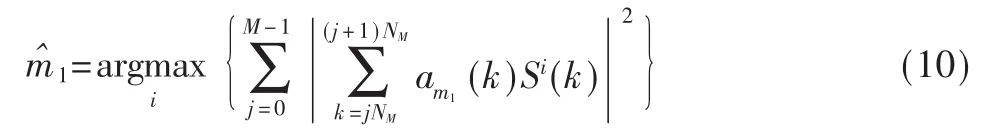

通过定时同步可以找到PSS的精确位置,但是不能判断当前接收数据属于前半帧还是后半帧(子帧0或者子帧 5)[5]。因此需要通过检测辅同步信号(Second Synchronization Signal,SSS)来完成帧同步,并获得。为了降低复杂度、减少计算量,决定采用解扰的办法获取SSS生成式[1]中的参数 m0和 m1,根据 m0和 m1与的一一对应关系,得到小区ID组号。

常用的解扰检测算法有相干检测算法与非相干检测算法,本文采用相干检测算法[4]。此算法的原理如下:

将时域接收PSS通过FFT变换成频域PSS,用Rpss(k)表示,并生成本地频域 PSS,用 Tpss(k)表示。当信道的相干时间大于4个OFDM符号长度时,能够算出信道冲激响应的估计值:

根据CP类型和PSS的位置,取出时域SSS并做FFT变换成频域SSS,对其进行信道补偿:

其中,i=0,1,…,30,M表示分段相关时的分段数,NM表示每段中的数据长度,这里假设M=4。

生成本地扰码序列 c1(k)和(k),并对 Rsss(2k+1)进行解扰,可得:

根据参考文献[1]中表 6.11.2.1-1可得,m1与 m0的估计值的对应关系如下:

2 ASIC设计与实现

2.1 结构说明

本文所设计的帧定时同步模块的硬件结构如图3所示,由4个部分组成:接口模块、存储器模块、控制模块和运算模块。

图3 帧定时同步模块硬件结构图

图3中,regif模块采用通用的ZSP总线接口,对模块相关功能所需参数进行设置,并能查询该模块的运行状态;mem模块实现ZSP总线和运算模块对存储器资源的读写,包含输入与输出存储器。

2.2 运算(core)模块

本模块主要分为FFT模块、产生本地 PSS或 SSS序列模块、最大值查找模块、PSS冲激响应计算模块和 m0/ m1估计模块。

2.2.1 FFT模块

本模块支持的运算点数分为 128点、256点、512点、1 024点和2 048点。FFT运算完成后,找出最大值以及归一化因子并输出。同时采用八路并行的方式来设计。八路并行结构就是在并行迭代结构的基础上,把并行迭代结构中每一级的全并行改成八路并行,减少了并行单元的数量,从而降低芯片的面积[6]。

2.2.2 产生本地PSS或SSS序列模块

本模块能够根据不同的需要产生本地频域或时域同步序列。首先根据配置的小区ID组号和小区组内ID号,和 PSS序列或者 SSS序列生成公式,产生62点频域的PSS或SSS序列。

2.2.3 最大值查找模块

本模块能够查找到输入数据中的主峰值以及两个次主峰值,并能够查找到每个主峰值周围的3个辅助峰值。每个主峰值至少间隔128个点。以输入数据长度为2 048点为例,首先找出第1个点到第2 048个点的最大值和所在的位置并记录。然后,取当前峰值左右共128个(可配)长度位置之后开始读取,左右各读取 18个(可配)数据进行对比,找出3个最大值作为辅峰值,记录这3个辅峰值的大小及位置。接下来,将该主峰值以及左右各 128点数据清零,开始查找第二个主峰值,后续以此类推。

2.2.4 PSS冲击响应计算模块

本模块输入数据长度固定为128点,为接收到的时域PSS序列,每点数据虚实各占16 b。输入数据首先进行FFT运算,得到频域的128点 PSS序列,并提取出其中的62点PSS序列。根据配置的小区组内ID号和PSS序列生成公式,产生62点本地的频域PSS序列。将接收的PSS序列与本地PSS序列进行相关运算,得到PSS序列的冲激响应。此冲激响应信号为 62点32 b数据,实部16 b,虚部16 b。

2.2.5 m0估计模块

本功能模块输入数据长度固定为128点,为接收到的时域 SSS序列,每点数据大小为32 b,虚实各占16 b。输入数据进行FFT运算后,得到频域的128点从 END状态跳转到 IDLE状态。提取出其中的 62点 SSS序列,得到偶数位置上的数据 Rsss(2k)。然后,根据配置的小区组内 ID号 M=m0-m1,生成解扰序列 c0(k),对(2k)进行解扰。

2.2.6 m1估计模块

本功能模块在m0估计模块中提取出62点SSS序列,得到奇数位置上的数据(2k+1)。然后,根据配置的小区组内ID号和 m0值估计功能运算得到的,生成扰码序列 c1(k)和(k),对(2k+1)进行二次解扰。

2.3 控制模块

本文所设计的控制模块使用有限状态机(Finite Status Machine,FSM)来进行实现。控制模块的FSM跳转如图4所示。

图4 控制模块FSM跳转图

(1)IDLE状态:模块未启动时均处于该状态,当模块的启动信号start有效时,从IDLE状态跳转到PARA状态。

(2)PARA状态:进入此状态后,并且para_en有效时,模块会从参数寄存器读取对应功能的参数配置值。当参数读取完成后,拉高para_finish信号,指示参数读取已经完成,从PARA状态跳转到PROC状态。

(3)PROC状态:进入此状态后,并且 meas_en有效时,进行模块具体功能的运算。当运算完成后,拉高proc_finish信号,指示运算已经完成,从 PROC状态跳转到 END状态。

(4)END状态:进入此状态后,表明外部配置的功能任务已经完成,拉高cell_finish信号,从END状态跳转到IDLE状态。

3 实验部分

3.1 仿真验证

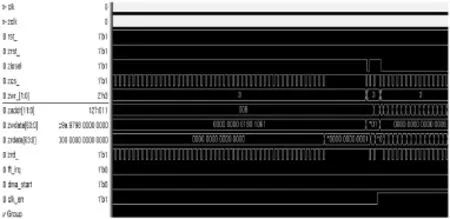

3.1.1 m0值估计功能仿真结果

从图5可以看出,本次仿真没有使能中断,因此只能不断读取中断标志寄存器的值,直到中断标志寄存器置位,才能判断该模块运行已经结束,然后再从存储器中读取输出数据,并比较输出数据的正确性。对比结果表明,该功能能够达到预期的目标。

图5 m0值估计功能仿真波形

3.1.2 m1值估计功能仿真结果

从图6可以看出,在运行m1值估计功能之前,首先运行了存储器清零功能。在模块完成了存储器清零功能之后,将需要进行m1值估计的输入数据存入存储器中,然后对参数寄存器和控制寄存器进行配置,并启动模块工作。模块运行结束后,正常产生中断信号。仿真结束后的数据对比表明,该功能能够达到预期的目标。

图6 m1值估计功能仿真波形

3.2 逻辑综合

本文采用了Design Compiler综合工具对所设计模块进行逻辑综合,它能够将RTL代码转换成门级网表,并且产生相应的延时文件。

从图7和图8能得出:本设计综合后的逻辑面积是1 302 392.271 666 μm2,总功率是51.291 1 mW。

图7 帧定时同步模块面积报告

图8 帧定时同步模块功率报告

4 结论

实验表明,本文设计的实现方案能够快速准确实现定时同步、帧同步和小区ID号检测等功能,经过验证、综合后,本设计可作为一个成熟的IP核,并可移植到含有帧定时同步功能的ASIC芯片中。

[1]ZHANG Z,LIU J,LONG K.Low-complexity cell search with fast PSS identification in LTE[J].Vehicular Technology,IEEE Transactions on,2012,61(4):1719-1729.

[2]张德民,朱翔,李小文.LTE系统中小区搜索定时同步的FPGA设计[J].电子技术应用,2013,39(9).

[3]SHENG Y,LUO X.Algorithm study on cell search in LTE[J]. Communications Technology,2009(3):035.

[4]PARK H G,KIM I K,KIM Y S.Efficient coherent neighbour cell search for synchronous 3GPP LTE system[J]. Electronics Letters,2008,44(21):1267-1268.

[5]3GPP TS 36.211 v11.0.0.Evolved universal terrestrial radio access(E-UTRA);physical channels and modulation (Release 11)[S].2013:108-111.

[6]李杰.低功耗可扩展FFT专用集成电路的设计[D].长沙:湖南大学,2011:20-53.

ASIC design and implementation of a LTE-A frame timing synchronization scheme

Dai Wenqiang,Li Guiyong

(Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

The paper researches a frame timing synchronization algorithm based on synchronization signals in TD-LTE-Advanced system,simulate the algorithm,do some necessary analysis and propos a realization scheme.Then,the strategies and scheme of ASIC realization are determined according to the precision,area,power consumption and other requirements,and the ASIC realization of frame synchronization module and FFT module are completed.Finally,through simulation,verification and logic synthesis,results show that the module can reach the expected goals of the functions.The ASIC design in this thesis has advantages in both power consumption and area size,by comparing with the similar module,the area of the ASIC design in this thesis is smaller about 8.8 percent,power consumption is lower about 9.3 percent.

LTE-A;frame synchronization;timing synchronization;ASIC

TN929.5

A

10.16157/j.issn.0258-7998.2016.03.013

代文强,李贵勇.一种 LTE-A帧定时同步算法的 AISC设计与实现[J].电子技术应用,2016,42(3):47-50.

英文引用格式:Dai Wenqiang,Li Guiyong.ASIC design and implementation of a LTE-A frame timing synchronization scheme[J]. Application of Electronic Technique,2016,42(3):47-50.

2015-08-07)

代文强(1990-),男,硕士研究生,主要研究方向:无线移动通信。

国家科技重大专项资助项目(2012ZX03001012-002)

李贵勇(1971-),男,硕士,正高级工程师,主要研究方向:无线移动通信。