高度整合硬件加速器的原型验证平台Protium

2016-12-01孙丰军李文强陈思若

孙丰军,李文强,陈思若

(1.北京展讯高科通信技术有限公司,北京100190;2.Cadence公司,北京 100100)

高度整合硬件加速器的原型验证平台Protium

孙丰军1,李文强1,陈思若2

(1.北京展讯高科通信技术有限公司,北京100190;2.Cadence公司,北京 100100)

Protium是Cadence最新型的FPGA快速原版验证平台,和Cadence的硬件加速器 Palladium系列高度整合,可完全重用Palladium的编译流程,运行速度提升最高可到 10倍,当出现可疑 RTL bug的时候可无缝移植到 Palladium进行调试,是软件调试的理想平台。以展讯北京的AP+GPU项目验证为例,展示了Protium在软件调试和系统验证流程中的价值和收获。

原型验证;硬件加速器;早期软件开发;帕拉丁

1 展讯手机芯片性能验证的挑战

随着智能手机的快速发展,用户对手机芯片的性能要求也越来越高,与之对应的是芯片的规模也越来越大,软件也越来越复杂,为了提高用户体验,加速芯片上市时间,在芯片流片回来前,需要尽早启动大量的软硬件系统调试工作,而传统的FPGA流程已经很难满足要求。比如芯片性能测试中必须用到的GPU模块,对应传统的 FPGA测试,一片 Xilinx公司的 Virtex7芯片已经无法容纳一款中高性能手机芯片的 GPU模块,GPU模块的特殊性又使得该模块在 FPGA上做partition变得很繁琐困难。同时FPGA调试板由于其调试复杂性往往延迟到项目后期才能成熟和使用,对于软件团队来说存在着无米下炊的困惑。

2 现有仿真平台在软件调试上的局限

硬件加速器现在已经成为验证流程里一个不可或缺的关键平台。由于相对于软件仿真(simulation)巨大的速度优势和全面的 debug调试能力,硬件加速器已经广泛应用在硬件加速仿真,系统级验证,软件开发调试等各个阶段,是整个验证周期最早可以获得的软硬件协同的系统级验证平台。然而当RTL开发进入到成熟期后,硬件加速器的硬件 debug能力已经不是必需的,反而是运行速度成为软件工程师关注和体验的焦点。硬件加速器的典型速度约在1 MHz~2 MHz,对于软件工程师来说还是不够快。另外当多个软件工程师同时需要硬件加速器的资源进行调试时,将加剧硬件加速器的资源短缺,也增加了软件调试开发的成本。

自研FPGA原型板或者是选择商用FPGA原型板由于其运行速度的优势也是目前广泛使用的配套解决方案。可是其缺点也是非常明显的。调试FPGA原型板往往由于FPGA先天调试能力的欠缺而使得整个调试周期冗长且不可控,而且也需要投入大量的人力资源做专门的维护,这对于时间预算紧张的项目来说往往意味着风险。有没有一种解决方案可以结合硬件加速器调试能力和商用FPGA原型板的速度优势呢?

3 Protium的基本特点和优势

Protium是Cadence新近推出的基于 FPGA的快速原型验证解决方案,适用于早期软件开发,回归测试和高性能系统级验证。Protium应用了最新一代的超大规模FPGA,提供了一整套从编译到软件调试的流程,具有快速启动和简单易用的特点。最有价值的是Protium完全兼容Cadence硬件加速器 Palladium的编译流程,可重用硬件加速器上广泛使用的降速桥(speedbridge),用户因此可以平滑快捷地从Palladium仿真环境过渡到更高性能的快速原型验证平台上来。Protium具有以下特点及优势:

(1)基本特点

最大支持8 x Xilinx Virtex-7 2000T FPGA。

(2)与硬件加速器Palladium完美整合

①可重用Palladium仿真编译环境,包括编译和运行时脚本;

②兼容Palladium的speedbridge系列加速桥;

③自动生成 post-partition数据库,可返回Palladium进行快速模型验证。

(3)全自动的FPGA后端实现

①全自动的FPGA partition和布局布线(PNR);

②全自动的Memory Model转换和模型化;

③全自动时钟树转换 (包括 gated clock,multiplexed clocks,latch etc.);

④全自动的 timing closure,自动消除 setup/hold time violations。

(4)多样化的调试解决方案

①支持对存储单元的数据上载和下载;

②支持force和release;

③可选的 black-box解决方案,可支持高速设计模块和接口;

④提供扩展子板支持用户定制接口;

⑤可返回Palladium进行复杂调试。

4 Protium编译运行流程

4.1Protium系统级验证环境

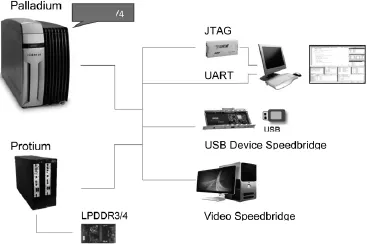

实验室系统级验证环境如图1所示。

(1)Palladium PXPII X16:硬件加速器72M gate。

(2)Protium:FPGA快速原型验证系统,支持 8 Xilinx Virtex-7 FPGA。

Acquity超高效液相色谱仪、紫外检测器、Synapt Q-TOF MS(美国沃特斯公司);SHB-IIIA循环水式多用真空泵、DLSB低温冷却循环泵(上海豫康科教仪器设备有限公司);RE-2000旋转蒸发仪(上海洪旋实验仪器有限公司);KQ-200VDE型双频数控超声清洗器(昆山市超声仪器有限公司);10KD超滤离心管(美国密理博公司);Avanti J-26XP高速冷冻离心机(美国贝克曼库尔特公司);SynergyMx多功能酶标仪(美国伯腾公司);BT-125D电子天平(赛多利斯科学仪器北京有限公司)。

(3)JTAG&UART:通过SOC的JTAG接口连接ARM debugger;通过 SOC的 UART接口连接 PC串口,用于打印软件debug信息。

(4)Video speedbridge:通过 SOC视频输出接口显示实时视频图像。

(5)USB Device speedbridge:通过 SOC USB接口连接U盘文件存储器。

图1 Protium系统验证环境

(6)DDR daughter board:Protium专用子卡,用于支持SOC外接的DDR。

4.2Protium的编译及运行流程

Protium编译运行流程如图2所示,主要步骤如下:

图2 Protium编译运行流程

(1)在 Palladium上做回归仿真测试,确保 RTL和主要端口工作正常,比如串口,JTAG,LPDDR4。

(2)复用 Palladium的编译脚本,加入FPGA控制命令,如board file,probes等。

(3)将步骤(1)产生的 Palladium网表作为设计输入,执行步骤(2)更新后的脚本完成HDLICE编译和FPGA布局布线并产生最终FPGA可用的bitfile。

(4)下载步骤(3)产生的bitfile到Protium。

(5)复用 Palladium仿真过程中使用的初始化脚本,以执行必要的初始化过程,比如 load image文件到ROM/SRAM/LPDDR4,force/release,setup trigger等。

(6)执行run命令。

5 硬件调试过程

如果硬件运行不正常,可通过以下三种途径调试:

(1)设置触发条件,并通过Xilinx Chipscope下载信号波形调试。

(2)返回 Palladium运行,执行同一运行时初始化命令脚本,排除RTL版本差异导致的功能性问题。

(3)利用编译中产生的 verification model直接在 Palladium上运行,以排除FPGA后端处理阶段可能产生的时序和功能性问题。

6 软件调试过程

软件测试目的为:Boot Android及 Benchmark测试,包括 Memory Copy,Antutu跑分等。

软件的调试过程如图3所示,首先是健全测试,包括JTAG连接,UART打印,DDR初始化及读写测试,这些是软件调试的必要条件。主要步骤如下:

图3 软件调试过程

(1)JTAG&UART打印:相对简单,调试比较顺利。

(2)DDR测试:在Emulator平台,包括Palladium XP及Protium,用的是专用DDR PHY与DDR颗粒,与EDA仿真平台用的Model不同,对于DDR的初始化及读写测试,需要软件工程师与ASIC设计工程师的紧密配合。在这个过程中,Palladium XP强大的Debug功能为Protium平台DDR的调试工作提供了有力支持。

(3)Bootloader及 DisplayC测试:不论是 Boot Android及 Benchmark测试,都需要屏幕显示,Protium外接与Palladium XP相同的Video Speedbridge,在液晶显示器上显示图像。

(4)GPU测试:包括 GPU的 driver调试,功能测试及GPU本身BenchMark评估。

(5)Android及 Antutu相关的测试:包括 ANTUTUMEMORY Operation,ANTUTU-RAMSPEED,ANTUTUSINGLE_INTEGER,ANTUTU-SINGAL-FLOAT等。

7 测试结果

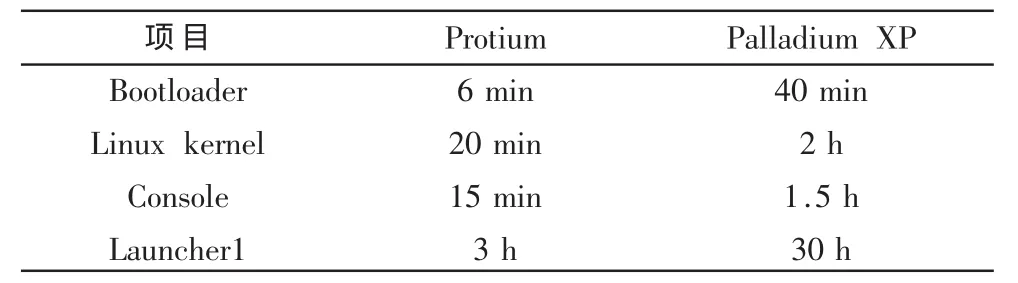

测试结果如表1和表2所示。

表1 Protium与Palladium XP编译结果对比(Gate Count:~100 M)

表2 Protium与Palladium XP Bootup time对比

8 总结

借助 Protium平台,在芯片流片前,成功完成了软硬件协同的性能测试,包括 Boot Android及 Antutu跑分。Protium和Palladium XP相得益彰的特性,使得在 Protium开发过程中遇到问题时,可以迁移回退到Palladium XP平台进行 Debug,问题解决后,再利用 Protium的速度优势,回归到 Protium平台进行开发,如此缩短了项目的开发周期,加速了芯片的上市进程。

Highly integrated hardware acceleration platform Protium

Sun Fengjun1,Li Wenqiang1,Chen Siruo2

(1.Beijing Spreadtrum High-Tech Communication Technology Co.,LTD,Beijing 100190,China;2.Cadence,Beijing 100100,China)

The Cadence rapid prototyping platform Protium is addressing and solving challenges by providing a low cost and high speed solution that is fully integrated with the emulator in compile and debug flow,reducing the prototype bring up from months to weeks.This paper demonstrates the integrated flow of prototype and emulator in developing the AP+GPU SOC project at Spreadtrum Beijing design center.The Protium reuses the emulator compile environment and is fully automatic in FPGA implementation.It provides a 10X faster platform than emulator for software development and can still leverage the super debug capability of Emulator when runs to issue.

prototyping;Emulator;early software development;Palladium

TN402

A

10.16157/j.issn.0258-7998.2016.08.008

2016-06-16)

孙丰军(1980-),男,硕士研究生,高级工程师,主要研究方向:SOC Emulator验证。

李文强(1986-),男,本科,高级工程师,主要研究方向:SOC Emulator验证。

陈思若(1973-),男,硕士研究生,高级工程师,主要研究方向:硬件加速器和快速原型验证的技术。

中文引用格式:孙丰军,李文强,陈思若.高度整合硬件加速器的原型验证平台 Protium[J].电子技术应用,2016,42 (8):41-43.

英文引用格式:Sun Fengjun,Li Wenqiang,Chen Siruo.Highly integrated hardware acceleration platform Protium[J].Application of Electronic Technique,2016,42(8):41-43.