基于SRAM型FPGA的SEU敏感性研究*

2016-11-30王大鸣张彦奎代龙震

冯 兴,王大鸣,张彦奎,代龙震

(中国人民解放军信息工程大学,河南 郑州450001)

基于SRAM型FPGA的SEU敏感性研究*

冯兴,王大鸣,张彦奎,代龙震

(中国人民解放军信息工程大学,河南 郑州450001)

目前星载信号处理平台中大量使用商用芯片,但商用芯片抗辐射能力较弱,在空间环境下常出现单粒子翻转(Single Event Upset,SEU),从而造成系统功能紊乱,甚至中断。提出以星载信号处理平台中大量使用的SRAM型FPGA为研究对象,采用故障注入的方式研究FPGA中不同硬件资源对于SEU效应的敏感性问题。根据不同资源对SEU效应表现出不同敏感性的结论,可在SRAM型FPGA的抗SEU防护上进行有针对性的设计。

单粒子翻转;SRAM;FPGA;故障注入;敏感性

0 引言

随着星载信号处理平台对于信号处理能力需求的不断提升,宇航级芯片已越来越难以满足需求,而商用芯片相对宇航级芯片拥有更强的处理能力和更多的处理资源。所以基于商用芯片构建星载处理平台的商用现成技术(Commercial Off-The-Shelf,COTS)成为当前卫星通信平台设计领域的研究热点。

由于商用芯片向着高密集度、低操作电压的方向迅速发展,使得它们在空间辐射环境下的可靠性大大降低。其中软故障是主要故障,它是由带电粒子和PN结相互作用引起的一种暂态故障,可造成芯片严重的运行错误[1]。所以如何弥补商用芯片本身抗辐照能力的不足是需要解决的重要问题。

国内外研究机构对于星载信号处理平台抗SEU方法目前主要分为两类:一类是针对SEU的屏蔽,包括各种抗SEU加固结构设计、高性能抗SEU的CMOS(Complementary Metal Oxide Semiconductor)工艺等[2];另一类是针对 SEU的修复,如动态可重构技术、编码纠正[3]等方法。另外,由于星载平台中包含大量的诸如 FIR(Finite Impulse Response)滤波和 FFT(Fast Fourier Transform)的处理过程,故近年来针对各种滤波器和信号处理算法本身抗SEU的方法研究特别广泛,如文献[4]、文献[5]分别实现FIR滤波器和FFT算法的容错技术。

相对于上述研究思路,本文则重点关注芯片内部各种不同硬件资源对于SEU事件的敏感性。以星载平台上应用广泛的SRAM型FPGA为研究对象,通过模拟星载平台和故障注入的实验,根据各种资源在故障源注入后诱发系统出现功能紊乱的概率总结出各种资源对于SEU敏感性高低的结论。

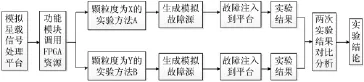

1 SEU敏感性研究模型

为验证SRAM型FPGA不同资源对于SEU存在不同的敏感性,需要模拟星载信号处理平台SRAM型FPGA在外部空间遭遇SEU效应的整个过程。即在地面上模拟采用SRAM型FPGA的星载信号处理平台,模拟FPGA出现的SEU错误,以及将模拟的SEU错误注入到FPGA内部不同资源中。据此提出SEU敏感性研究的模型,如图1所示。

图1 研究模型

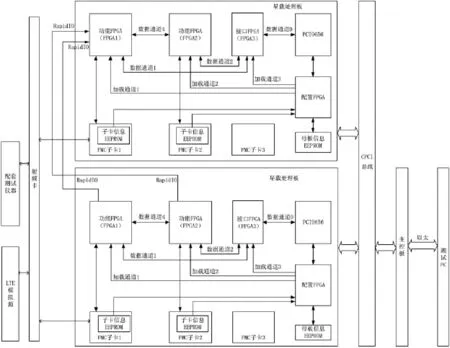

根据研究模型,首先可以采用基于商用芯片的星地联合处理平台来模拟星载平台,其硬件环境如图2所示。其中CPCI(Compact Peripheral Component Interconnect)总线用来模拟星地链路,星载处理板模拟星载信号处理平台,处理板采用了多片SRAM型FPGA芯片作为实验的测试芯片。

为调用FPGA内部资源,采用两种功能相同但实现方式不同的功能模块,因此可以针对两种模块设计颗粒度不同的实验A和实验B来分别进行实验。基于功能模块通过故障注入的方式生成模拟的SEU错误,在系统正常运行的情况下,将错误注入到平台FPGA的功能模块中,观察注入前后的输出状态,对比两次实验结果,得出SEU敏感性研究的结论。

2 SEU敏感性实验设计

2.1基于IP核的FFT敏感性实验设计

通常星载平台中拥有大量的FFT运算,而这些运算大都通过在FPGA中调用IP核来实现。因此以基于IP核的FFT来进行SEU敏感性实验是合理的。SRAM型FPGA芯片由6个部分组成,其中Slice资源是可编程逻辑单元的基本逻辑单元,RAM资源是FPGA常用的硬核模块,两种资源都是FPGA内部广泛分布且应用较多的资源。所以基于IP核的FFT敏感性实验所针对的资源就是Slice和RAM。

Slice资源内部主要的配置关系是逻辑关系,即“+”、“~”、“*”关系;RAM资源内部主要的配置关系是数值关系,即0、1数值关系。所以针对这两种资源的故障注入将分别围绕这两种配置关系进行修改。利用FPGA_Editor查看网表文件,并对其进行修改,生成差异比特文件,即模拟故障源。在FFT模块正常运行后通过测试电脑经模拟星地链路,反复将故障源注入到FFT模块中,通过chipscope抓取结果,根据结果得出结论。

2.2基于软件实现的FFT敏感性实验设计

为进一步验证上述结论,在前述实验的基础上,设计了另一种颗粒度更高的实验来加以证明。该实验运用VHDL语言编程实现16点的FFT功能模块,该模块调用更多的FPGA资源,采用相同的星地联合处理平台,同样针对Slice和RAM两种资源进行故障注入实验。

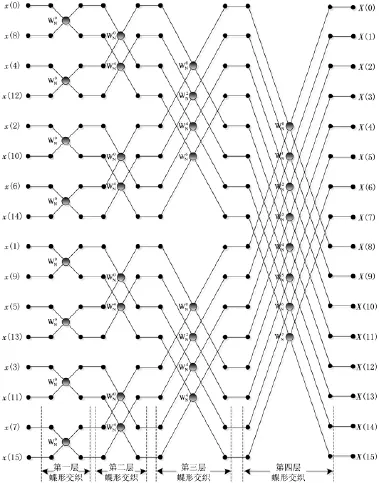

设16点数据为 x(0)、x(1)…x(15)的 16位的实数数据,按时间抽取的基2 FFT算法原理可得该16点FFT的蝶形交织运算,如图3所示,其结果即是X(0)~X(15)的16点FFT输出。由图可知,该FFT算法原理的核心是每一层的蝶形交织运算,因此整个16点FFT程序设计的关键是四层的蝶形交织运算。

图2 星地联合处理平台

图3 16点FFT蝶形交织运算流图

设计程序分成五部分,即顶层的输入输出和4个蝶形交织层。最初输入16点的16位实数数据,然后通过每层的蝶形交织计算得到最终FFT的输出。将结果与MATLAB仿真进行对比,验证该FFT模块是否编写正确。确认模块功能正确后,同样针对 Slice和 RAM进行修改;然后进行故障注入试验,通过chipscope抓取结果;最后根据结果得出结论。

3 SEU敏感性实验及分析

3.1基于IP核的FFT敏感性实验及分析

通过FPGA_Editor可得知 IP核FFT模块拥有 1 227个 Slice、17个 RAM资源。将 1 227个 Slice资源中每连续的20个左右分为一组,共分为60组。对每一组资源中的每一个Slice都在数量为10处进行逻辑修改。将17个RAM资源划为17组,对每一个RAM分别进行数量统一为10处的数值修改。最后得到60个Slice和17个RAM的差异比特文件,并对每一个差异比特文件进行100次的反复注入。

3.1.1实验结果

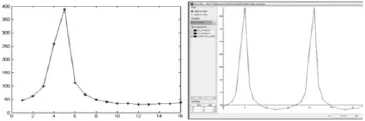

针对 Slice资源的故障注入结果分为四个程度,分别如图4~图7所示。所有60组试验中只有4组结果正确,其余组都出现各种错误。

针对RAM资源的故障注入结果分为三个程度,如图4、图8和图9所示。所有试验中只有4组出现错误。

图4 正确FFT输出

图5 FFT出现较轻微错误

图6 FFT出现特别明显错误

图7 FFT出现严重错误

图8 FFT出现较明显错误

图9 FFT出现特别明显错误

3.1.2实验结论

(1)在Slice颗粒度约为20个一组、共60组的情况下,根据大量反复注入的试验结果,利用统计数据可得针对Slice资源故障注入后模块的故障率为:θ1=(56/60)× 100%=93.3%;针对RAM资源故障注入后的故障率为:θ2=(4/7)×100%=23.5%。故在 SEU效应敏感度上,Slice强于RAM。

(2)试验中每组故障注入的数量一致,但注入的位置各不相同。通过每组最后的结果对比可知,不同位置的故障注入将对模块产生不同程度的影响。

(3)在 77组故障注入试验中,结果是逻辑修改引起的模块故障率更高。故SEU造成逻辑上的故障对整个模块影响要明显强于数值故障造成的影响。

3.2基于软件实现的FFT敏感性实验及分析

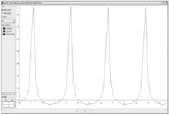

为了验证该编写的FFT模块功能正确,首先在MATLAB中实现FFT算法,然后将其每层蝶形交织结果与VHDL程序的每一层蝶形交织结果进行对比。对比输出结果如图10所示,左侧为MATLAB仿真结果,右侧为VHDL程序运行结果。

图10 FFT蝶形交织结果对比

由对比可知,VHDL程序运行结果与MATLAB仿真吻合,证明该程序具备正确的FFT功能,可作为本次实验的模块。通过FPGA_Editor可知,生成的FFT模块拥有2 265个Slice、2个RAM资源。

与前述实验类似,将该 FFT中的 2 265个 Slice资源每连续的10个左右分为一组,共分为240组,对每个Slice进行数量为10处的故障注入;将2个RAM资源划为2组,对每个RAM进行数量10处的数值修改。最后生成240个Slice和2个RAM差异比特文件,并对每个文件进行100次的反复注入。

3.2.1实验结果

针对Slice资源试验,所有试验中有32组结果正确,其余出现明显错误,如图11所示。针对RAM资源的试验结果2组都正确,如图12所示。

图11 FFT出现明显错误

图12 FFT正确无误

3.2.2实验结论

(1)本次实验在前述实验的基础上将Slice测试颗粒度提高1倍,试验组数提高4倍。由大量反复注入的试验结果,利用统计数据可得针对Slice注入模块故障率为:θ1=(208/240)×100%=86.7%;针对RAM资源故障注入后的FFT模块故障率为:θ2=(0/2)×100%=0%。所以有θ1>θ2,故在 SEU效应敏感度上,Slice强于 RAM。

(2)每组故障注入的数量相同,但位置不同。结果发现不同位置的注入对模块产生不同程度的影响。

(3)该次实验依然是针对Slice资源进行逻辑修改,针对RAM资源进行数值修改。从结果来看,依然是逻辑的错误对整个模块的影响强于数值错误。

4 结论

本文重点分析芯片内部不同硬件资源对于SEU效应敏感性的问题。以SRAM型FPGA为研究对象,设计进行了两种颗粒度不同的故障注入实验。结果表明,在FPGA内部资源中,Slice资源对于 SEU效应的敏感性很强,RAM相对较弱。SEU效应引起的逻辑错误比数值错误更能诱发系统的功能紊乱。所以,可针对FPGA中占用Slice资源较多的模块进行防护,重点针对逻辑错误进行防护。

[1]裴志强,周刚.FPGA的空间容错技术研究[J].微处理机,2011,32(6):18-20.

[2]冯彦君,华更新,杨桦,等.国外星载容错计算机技术及最新进展(综述)[C].全国第十二届空间及运动体控制技术学术会议论文集,2006.

[3]徐斌,王贞松,陈冰冰,等.适用于空间环境下的FPGA容错与重构体系[J].计算机工程,2007,33(3):231-233.

[4]GAO Z,REVIRIEGO P,PAN W,et al.Efficient arithmetic residue-based SEU tolerant FIR filter design[J].Circuits& Systems II Express Briefs IEEE Transactions on,2013,60 (8):497-501.

[5]REVIRIEGO P,BLEAKLEY C J,MAESTRO J A.A novel concurrent error detection technique for the fast Fourier transform[C].Signals and Systems Conference(ISSC 2012),IET Irish.IET,2012:1-5.

[6]邢克飞.星载信号处理平台单粒子效应检测与加固技术研究[D].长沙:国防科学技术大学,2007.

[7]REVIRIEGO P,MAESTRO J A,O′DONNELL A,et al.Soft error detection and correction for FFT based convolution using different block lengths[C].11th IEEE International OnLine Testing Symposium.IEEE,2009:138-143.

[8]宋凝芳,朱明达,潘雄.SRAM型 FPGA单粒子效应试验研究[J].宇航学报,2012,33(6):836-842.

[9]邢克飞,杨俊,王跃科.Xilinx SRAM型 FPGA抗辐射设计技术研究[J].宇航学报,2007,2(1):123-129.

[10]REVIRIEGO P,BLEAKLEY C J,MAESTRO J A.Signal shaping dual modular redundancy for soft error tolerant finite impulse response filters[J].Electronics Letters,2011,47(23):1272-1273.

[11]YANG W,WANG L,ZHOU X.CRC circuit design for SRAM-based FPGA configuration bit correction[C].Solid-State and Integrated Circuit Technology(ICSICT),2010 10th IEEE International Conference on.IEEE,2010:1660-1664.

SEU sensitivity research in SRAM-based FPGA

Feng Xing,Wang Daming,Zhang Yankui,Dai Longzhen

(PLA Information Engineering University,Zhengzhou 450001,China)

Current commercial chips are widely used in spaceborne signal processing platform.But the commercial chips are weak to resist radiation and often appear SEU causing system dysfunction or even interruption.This paper aims at studying the subject of SRAM-based FPGA which is extensively used in the spaceborne signal processing platform.By adoptting the way of fault injection, we study different sensitivity to SEU effects presented in different hardware resources in FPGA.According to different sensitivity to SEU effects presented in different hardware resources,the protection for resisting SEU design of SRAM-Based FPGA will be targeted.

single event upset;SRAM;FPGA;fault injection;sensitivity

TN47;V19

A

10.16157/j.issn.0258-7998.2016.05.015

国家高技术研究发展计划(863计划)(2012AA01A502)

2016-01-06)

冯兴(1990-),通信作者,男,硕士研究生,主要研究方向:星载信号处理平台的抗 SEU设计,E-mail:aishangmeiling2011@126.com。

王大鸣(1971-),男,博士,教授,博士生导师,主要研究方向:卫星与移动通信。

张彦奎(1990-),男,硕士研究生,主要研究方向:卫星与移动通信。

中文引用格式:冯兴,王大鸣,张彦奎,等.基于SRAM型FPGA的 SEU敏感性研究[J].电子技术应用,2016,42(5):53-56.

英文引用格式:Feng Xing,Wang Daming,Zhang Yankui,et al.SEU sensitivity research in SRAM-based FPGA[J].Application of Electronic Technique,2016,42(5):53-56.