基于Tsi578的多通道短波通信系统交换模块设计与实现*

2016-11-30王青波娄景艺

王青波,高 俊,娄景艺

(海军工程大学 电子工程学院,湖北 武汉 430033)

基于Tsi578的多通道短波通信系统交换模块设计与实现*

王青波,高 俊,娄景艺

(海军工程大学 电子工程学院,湖北 武汉 430033)

为更好地将串行RapidIO总线(SRIO)和相控阵技术应用于多通道短波通信系统中,提出一种基于Tsi578的SRIO互连交换系统的设计和实现方案,并对该系统的SRIO实验性能进行了测试。该交换单元采用DSP+FPGA结构,易于系统维护和扩展,且提升了系统的灵活性和运算效率。实验表明,该交换单元正常稳定工作,SRIO传输速度与传输数据包大小有线性关系,在传输1 024 Byte时达到最高速率496.941 2 Mbps。此外,文章总结了SRIO在工程应用中的三个问题,并提出了相关优化建议。

Tsi578;SRIO;交换机;短波通信

0 引 言

短波通信系统是以短波作为通信媒介的通信系统,天波为其主要传播方式。凭借着天然的“中继系统”电离层,且便于搭建的特点,短波通信系统的抗毁性明显优于其他通信系统,使其在军事通信领域一直有着不可替代的地位。但是,短波通信也有明显的缺点,其中继系统电离层作为自然产物,具有不稳定,受昼夜、季节、气候等影响较大。此外,短波天线指向性差,使得短波通信稳定性差,通信效率低。在电磁环境日趋复杂的今天,随着相控阵技术的不断发展与成熟,为了实现更好的通信效率、更高的隐蔽性,文献[1]提出短波任意分布阵的功率合成技术,文献[2]提出相控阵短波发信系统相位校正技术,将相控阵技术应用于短波通信系统成为短波通信系统发展的新内容。于是,多通道短波通信系统应运而生。一个多通道短波通信系统包含多个发射单元和接收单元、一个波束控制单元、交换单元和相应的业务单元。其中,交换单元作为整个系统的中枢节点,与多个发射单元、接收单元直连,完成数据转发,并与波束控制单元一起完成对发射单元的波束指向配置[3]。

1 交换模块设计

1.1 总线选择

在典型的嵌入式系统中,系统各模块之间的传输速率成为嵌入式系统发展的制约瓶颈。传统总线如VME、PCI、PCI-X、CPCI等,均属于分时共享总线,传输速率受到限制,一般都低于500M bps,不能很好地满足系统的需求。现代总线如千兆以太网、PCI-E、InfiniBand、RapidIO等技术,总线传输速率均能达到1 Gbps,满足系统的需求。但是,千兆以太网主要用于建设高速局域网,使用TCP/IP协议,软件开销大。InfiniBand是一种支持多链接的“转换线缆技术”,主要应用于系统域网络互连,服务器与服务器之间的互连[4]。PCI-E协议开销大、功耗高、管脚多,不适用于嵌入式系统。

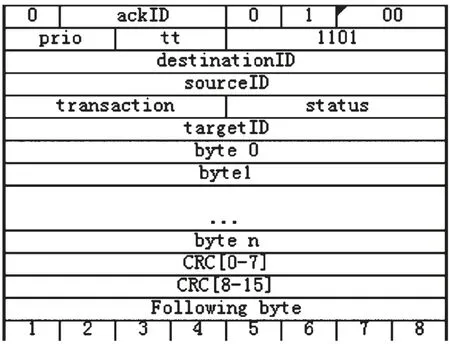

本系统设计采用RapidIO技术。RapidIO是为了满足现在和未来高性能嵌入式系统的独特需求而设计的一种开放式互连体系标准,是一种基于背板互连的高速串行互连标准[5]。它采用基于报文交换的互连体系结构,具有高性能、低引脚数、低延迟的特点。RapidIO总线采用三层结构,由逻辑层、传输层、物理层[6]组成,采用了唯一的传输层规范,向上向下兼容不同的逻辑层和物理层[7]。SRIO一共支持六种基本的I/O操作,分别为读操作、写操作、带响应的写、流操作、原子操作和维护操作。数据包类型共有16种,其中第13类型的包对应的格式如图1所示。

图1 SRIO传输数据包格式

1.2 SRIO互连结构

基于SRIO总线的嵌入式系统可以分为两种结构。一是基于线连接的SRIO总线系统。此种结构各模块之间直接采用导线进行连接,通过各模块使系统联通。由于此结构系统各模块相互关联,不适于扩展和升级,因此只适用于结构相对简单、固定的系统。二是基于交换器件的SRIO总线系统。此种结构通过SRIO交换器件连接各模块,使得各模块之间形成点到点的数据传输,且各模块相互独立,易于系统升级和扩展,简化系统的复杂度,提高系统性能,适用于较为复杂、结构灵活的系统。SRIO互连结构框图如图2所示,本系统采用交换器件的互连结构。

图2 SRIO互连结构

本系统中的SRIO交换器件采用IDT公司的Tsi578。Tsi578是由IDT公司[8]在原来业界领先的Tsi568A(SRIO Switch)的基础上研制的SRIO交换器件,完全兼容Tsi568A,方便原有系统的升级。Tsi578基于RapidIO 1.3规范,最大聚合带宽达到80 Gbps,采用低功耗和低延迟的直通传输方式,支持热插拔;一块芯片支持混合的速度和带宽配置;端口配置灵活,可以满足多种I/O带宽要求,可以配置8个4X或者16个1X模式的端口[9],可以通过内部寄存器对端口速率可以进行分别配置,配置速率分别为1.25、2.5、3.125 Gbps;查找表分为本地查找表和全局查找表,其中本地查找表支持512个ID,全局查找表支持高达6 400个ID。

1.3 系统方案设计

交换模块的整个框图如图3所示。交换单元包含一块DSP芯片、FPGA芯片、SRIO交换器件和15个光电转换器件。交换器件采用IDT公司的Tsi578芯片;FPGA采用ALTERA的EP2AGX95DF2515N;DSP芯片采用Tms320C6416定点DSP芯片。DSP有满足算法控制结构复杂、运算速度高、寻址方式灵活和通信性能强大的特点,但是其本质上还是串行的,对于处理数据量大,处理速度要求高,但是运算结构相对简单的底层信号处理算法并不能发挥其优点。此部分适于采用FPGA硬件实现,采用DSP+FPGA结构,把二者的优点结合,兼顾速度和灵活性,既满足底层信号处理要求,又满足顶层信号处理要求,适合于模块化设计,从而提高算法效率,且易于系统维护和扩展。DSP负责对整个交换单元的管理工作,完成对Tsi578的路由表配置、复位设置等,特别在实现波束指向时,DSP对4台发射机进行控制组阵。为了更有效地发挥短波通信系统的抗毁性,一般发射机与收信机之间的距离很远,达到十公里以上,而SRIO总线的传输长度(小于100 m)受限。由于SRIO逻辑层与物理层独立,因此可以在任何一种物理介质上传播,故每个Tsi578的端口连接到一个光电转换器,将电信号转换成光信号,使用光纤在各模块之间进行传输,以有效增强信号传输的完整性和抗干扰性,减少信号长距传输过程中的衰减。

图3 交换模块整体框

2 交换模块实现

2.1 Tsi578管理模块实现

SOC设计是以IP核为基础,而SOPC(System On Programmable Chip,可编程的片上系统)是由Altera公司提出的一种灵活、高效的SOC解决方案。可以通过SOPC在片上轻松集成存储器、I/O接口、处理器等系统外设,可视化地完成模块之间的连接,大幅提高硬件开发效率。

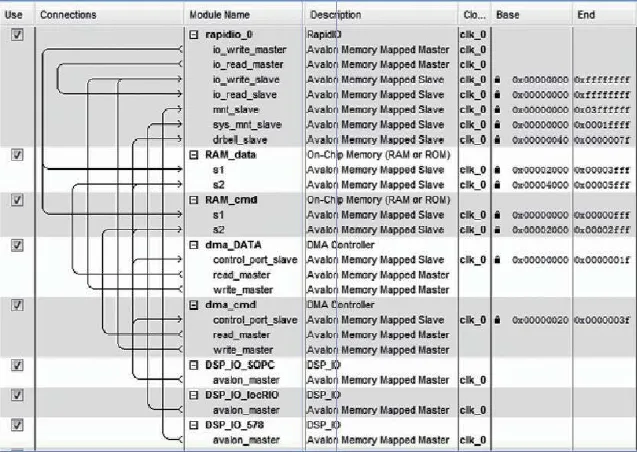

SOPC各模块连接图如图4所示。

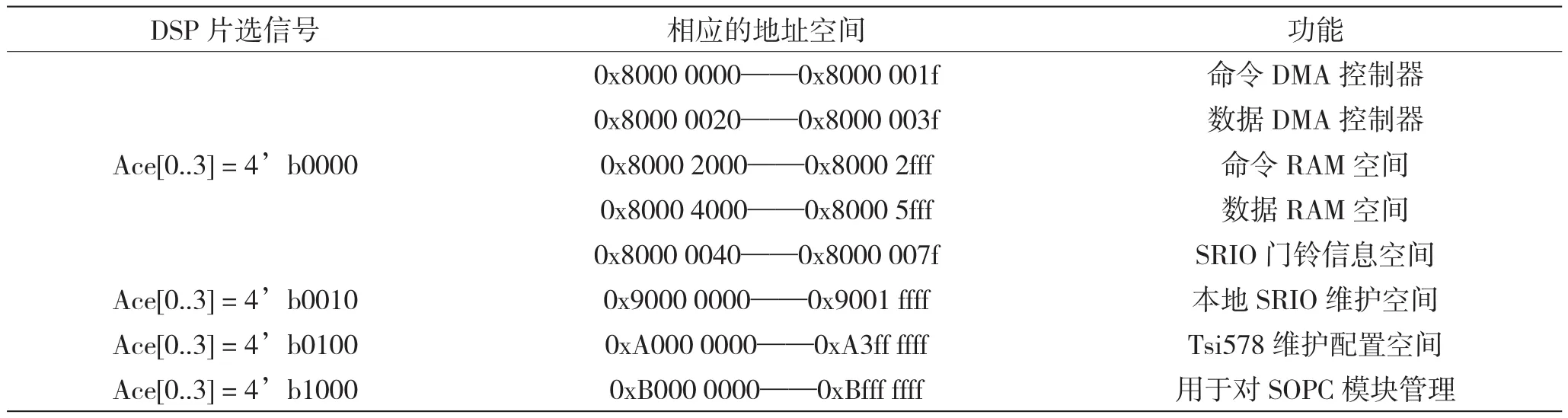

DSP地址空间划分如表1所示。

图4 SOPC内部连接

表1 DSP空间规划

本系统采用分组交换的思想,数据命令分别存储,且确定数据和命令包的大小。具体设计如下:命令缓存区为0x000——0xfff,共4 096(256×16)Byte,命令包大小设定为256 Byte,每个ID对应一个256 Byte缓存。数据缓存区为0x2000——0x3fff,共8 192(512×16) Byte,数据包大小设定为512 Byte,每个ID对应一个512 Byte缓存。发方DSP将数据存入FPGA中的第一个缓存(作为本地命令和数据缓存),在DMA传输配置中,根据目的器件的ID(DEST_ID)得到DMA写地址的基地址,根据自身ID得到地址偏移量,基地址BASEADDR=DEST_ID×0x10000;命令偏移量CMD_OFFSETADDR=LOCAL_ID×0x100,数据包偏移量DATA_OFFSETADDR=LOCAL_ ID×0x200+0x2000,将数据写到目的IDSRIO中自身ID对应的缓存区,通过门铃通知目的ID到相应缓存区读取数据。DMA传输数据的流程如图5所示。

图5 DMA传输流程

2.2 Tsi578的配置管理

Tsi578的配置共有三种方法:

(1)通过I2C接口对Tsi578进行配置;

(2)通过JTAG口对Tsi578进行配置;

(3)通过SRIO维护操作对Tsi578进行配置。

因为采用SRIO维护操作对Tsi578的维护可以减少板上布线,而且可以实现动态配置Tsi578,故本系统采用交换单元上的DSP芯片作为整个单元的管理模块。由于采用了通过SRIO发送维修数据包的方式对Tsi578进行配置,所以在配置Tsi578前需对FPGA中的SRIO进行配置。交换单元的配置管理流程如图6所示。整个复位流程设计为DSP的一个任务(TSK),并使用信号灯sem作为触发标志,初始值设置为1,开机启动复位流程。运行阶段,对RapidIO IP核物理层提供的port_error信号若检测到高电平,则触发任务,完成配置RIO发射、接收和维护窗口,并复位Tsi578。

由于SRIO采用了基于请求、响应的方式设计,本地缓存数据队列等待确认,所以需要在本地缓存队列溢出前收到第一包数据的确认信息。链接超时和响应超时需要根据实际环境(如传输距离、电磁干扰情况)进行合理配置,以保证数据的正常传输。本系统设计光纤传播长度为30 km,光在光纤中的传播速度为2×108m/s(由于光在光纤中折线传输,所以不能以3×108m/s的直线传播速度进行计算),光电转换和电光转换耗时分别按0.1 ms计算,一次回路的数据传输时间0.5 ms,故最后对响应超时和连接超时设定为0x95D00。

3 性能测试与分析

3.1 测量方案设计

选择由一块发射板或接收板与交换模块上的DSP通过Tsi578形成数据通路(光纤传输距离为5 m),在发射板的数据RAM中预先存放好数据,接收机挂起一个任务(屏蔽其它全部硬中断和软中断,保证测量准确性)等待接收到完整的数据。由发射机通过DMA控制器发送一定数量字节的数据包,并立即拉高测试脚的电平,接收机一旦接收到这个包完整的数据,立即拉高其测试脚的电平。使用的示波器型号为Tektronix TDS3052C,采样率为5 Gsa/s,两个通道扫描两个测试脚的电平,两个测试脚上拉电平的时间差即为此数据包的传输时间,测试平台如图7所示。

图6 Tsi578复位流程

图7 实验测试平台

3.2 实验结果及分析

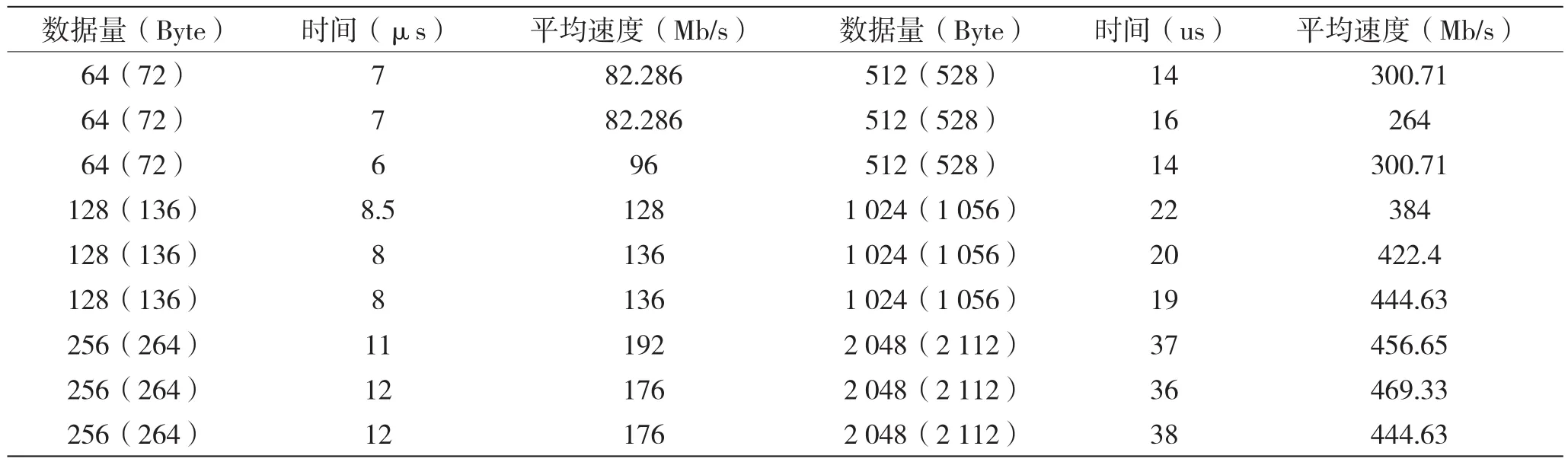

由发射板和交换板进行的测试结果1如表2所示。

使用同样的测试方法,选用一块接收板和交换模块来完成数据通路的搭建测试结果2,如表3所示。

表2 SRIO数据传输测试结果1

表3 SRIO数据传输测试结果2

表中括号内的数据为加上此次传输所包含的包头字节数。由图1的SRIO包格式可知,每包数据包含8 Byte包头,且SRIO协议规定每次传输的数据包负载最大为256 Byte,故当DMA传输量大于256 Byte时,将会进行分包传输,包含多个包头数据。计算过程中没有考虑8B/10B编码器,认为SRIO总线的理论传输速率为1 Gb/s(1.25×0.8)。

由实验结果可以看出:

第一,数据的传输速率基本与DMA传输量呈正相关,传输数据量达到1 024 Byte时,传输速率趋于平稳且达到峰值,故建议在系统中对同一目的ID的数据进行组包后发送,避免频繁发送小数据包。

第二,测量中出现差异明显的现象,如传输512 Byte,耗时16 μs,速率明显高于其他两次测量,表明SRIO总线传输易受到外界环境的影响。当受到外界干扰严重时,将会产生数据重发,导致传输延时。因此,建议对含SRIO总线的电路板或机箱以封闭金属外壳形成静电屏蔽。对于传输距离较长时,可采用光电转换器件,将电信号转换为光信号,在信道条件较好的光纤中进行传输,以尽量减短金属导线的长度。

第三,在两次相同的环境下使用相同的方法对不同PCB板测试得到的结果不同,说明PCB设计时对SRIO总线的布局布线对SRIO的传输速率有明显影响,应尽量降低SRIO总线受到的电磁干扰。因此,建议在PCB设计时采用各种高速走线的技巧,如减小同一PCB中长并联线的长度和信号抑制线间的接近程度,高隔离度的信号抑制线应该走不同的层等。

4 结 语

本文提出一种基于Tsi578的多通道短波系统的数据交换模块的设计方案,并给出交换模块的SOPC设计和配置管理流程图,最后对整个交换模块进行连通性测试和传输速率测试,得出SRIO在实际应用中的三个问题及其优化建议。SRIO总线作为唯一的系统互连国家标准,发展前景巨大。SRIO互连结构的研究对SRIO在大型系统中的应用意义重大,特别是使用SRIO总线技术和对系统结构的合理布局,值得深入研究。

[1] 章宇兵,张浩,廖桂生.任意分散布阵短波通信干扰机空间功率合成技术[J].西安电子科技大学学报:自然科学版,2006,33(01):150-154. ZHANG Yu-bing,ZHANG Hao,LIAO Gui-sheng.A Technology of Spatial Power-combination for the RanDom Decentralized Jammer Array[J].Journal of Xidian University(Natural Science),2006,33(01):150-154.

[2] 邓冉,高俊,屈晓旭.相控阵短波发信系统相位校正方案设计[J].通信技术,2015,48(10):1129-1133. DENG Ran,GAO Jun,Qu Xiao-xu.Phase Correction Schemeof Phased Array Shortwave Transmitting System[J].Communications Technolo-gy,2015, 48(10):1129-1133.

[3] 何宪文,高俊,屈晓旭等.多信道射频信号相位检测技术的研究与实现[J].通信技术,2014,47(05):478-482. HE Xian-wen,GAO Jun,Qu Xiao-xu,et al.Research and Realization of Phase Detection Technology for Multichannel RF Signal[J].Communications Technology,2014,47(05):478-482.

[4] 刘琳.基于RapidIO的高数数据传输系统设计[D].哈尔滨:哈尔滨工程大学,2013. LIU Lin.The Design of High-speed Data Transmission System Based on RapidIO[D].Harbin:Harbin Engineering University,2013.

[5] Fuller Sam.Anatomy of A Forward-looking Open Standard RapidIO[J].Computer,2002,35(01):140-234.

[6] 张娟娟.RapidIO高速串行总线的研究和实现[D].长沙:湖南大学,2011. ZHANG Juan-juan.Study and Implementation of RapidIO High Speed Serial Bus[D].Changsha:Hunnan University,2011.

[7] 李少龙,高俊,娄景艺等.基于SRIO总线的数字信号处理系统的实现[J].通信技术,2012,45(05):101-103. LI Shao-long,GAO Jun,LOU jing-yi,et al.Implementation of Digital Signal Processing System based on SRIO Bus[J].Communication Technology,2012, 45(05):101-103.

[8] 邓豹.RapidIO交换互连与配置管理研究[J].航空计算技术,2014,44(02):124-127. DENG Bao.Resaerch on RapidIO Switched Interconnect and Configuration Management[J].Aerobautical Computing Technique,2014,44(02):124-127.

[9] 汪星宇.RapidIO技术在信号处理系统中的应用于研究[D].南京:南京理工大学,2009. WANG Xing-yu.The Application and Research of RapidIO Technology in Signal Processing System[D]. Nanjing:Nanjing University of Science and Technology,2009.

王青波(1992—),男,硕士研究生,主要研究方向为数字通信、软件无线电;

高 俊(1957—),男,博士生导师,教授,主要研究方向为通信理论与技术;

娄景艺(1979—),女,硕士生导师,副教授,主要研究方向为卫星通信。

Design and Implementation of Switch Module for Multichannel Short-wave Communication System based on Tsi578

WANG Qing-bo,GAO Jun,LOU Jing-yi

(College of Electronic Engineering,Naval University of Engineering,Wuhan Hubei 430033,China)

In order to apply Serial RapidIO bus(SRIO) bus and phased array technology to multichannel short-wave communication system, the design and implementation of RapidIO interconnect switch system based on Tsi578 is proposed, and the test of SRIO's transmission speed in the system. This switch module adopts DSP + FPGA structure, thus is easy for system maintenance and expansibility, and improves system flexibility and operation officiency. The test indicates that this switch module can work normally and reliably.There exists a linear relationship between transmission speed and the size of packet, and it could reach the peak value of 496.9412 Mbps when the size of packet is 1024 Byte. This paper also discusses several performance optimization strategies in SRIO engineering application.

Tsi578; SRIO; switch; short-wave communication

TN915.05

A

1002-0802(2016)-07-0937-06

10.3969/j.issn.1002-0802.2016.07.026

2016-03-13;

2016-06-09 Received date:2016-03-13;Revised date:2016-06-09